【導(dǎo)讀】系統(tǒng)工程師在開發(fā)復(fù)雜的電子產(chǎn)品�����,例如傳感器和傳感器接口應(yīng)用時(shí)�����,他們所面臨的重大挑戰(zhàn)為更小的外形尺寸�����、杰出的功能�����、更佳的效能及更低的物料列表成本(BoM)���。設(shè)計(jì)者可以采用具有較高整合密度的較小制程節(jié)點(diǎn)來縮減晶方尺寸,同時(shí)也能使用先進(jìn)的封裝技術(shù)來實(shí)現(xiàn)系統(tǒng)小型化�。

3DIC成為縮小傳感器IC新解方

對于更高系統(tǒng)整合度的需求持續(xù)增加,這不只促使傳統(tǒng)的組裝服務(wù)供貨商�����,也推動(dòng)半導(dǎo)體公司開發(fā)更創(chuàng)新和更先進(jìn)的封裝技術(shù)����。 最具前景且最具挑戰(zhàn)性的技術(shù)之一就是采用硅通孔(TSV)的三維積體(3DIC)。 3DIC技術(shù)現(xiàn)在已被廣泛用于數(shù)字IC(例如���,內(nèi)存IC�、影像傳感器和其他組件的堆棧)中,其設(shè)計(jì)和制造方法已經(jīng)在數(shù)字世界中獲得成功證明��。 接下來��,設(shè)計(jì)者要如何將3DIC技術(shù)成功導(dǎo)入以模擬和混合訊號(hào)為主的的傳感器IC中�����?

在今日�����,走在前面的模擬和混合訊號(hào)IC開發(fā)商已開始意識(shí)到采用模擬3DIC設(shè)計(jì)的確能帶來實(shí)質(zhì)好處��。 智能傳感器和傳感器接口產(chǎn)品鎖定工業(yè)4.0����、智能城市或物聯(lián)網(wǎng)(IoT)中的各種應(yīng)用。 在各種芯片堆棧技術(shù)中��,TSV和背面重新布局層(BRDL)可用來替代傳統(tǒng)金線接合�,此技術(shù)的用處極大。

3D積體技術(shù)���,特別是來自領(lǐng)導(dǎo)晶圓代工業(yè)者的特殊模擬TSV技術(shù)����,在結(jié)合正面或背面重新布局層(RDL)后,由于互連更短且能實(shí)現(xiàn)更高的整合度���,因此能以更小的占板面積提供更多功能�。 特別是小尺寸的TSV封裝技術(shù)(總高度在0.32mm范圍內(nèi))能解決智能手表或智能眼鏡等穿戴式裝置的的小尺寸需求�����。

在不同的芯片或技術(shù)組合中���,TSV技術(shù)還能提供更高水平的靈活度,例如采用45奈米制程的數(shù)字芯片中的芯片至芯片堆棧��,以及在模擬晶圓(例如180nm)中����,微機(jī)電(MEMS)組件或光傳感器和光電二極管數(shù)組的堆棧,這只是其中的幾個(gè)例子���。

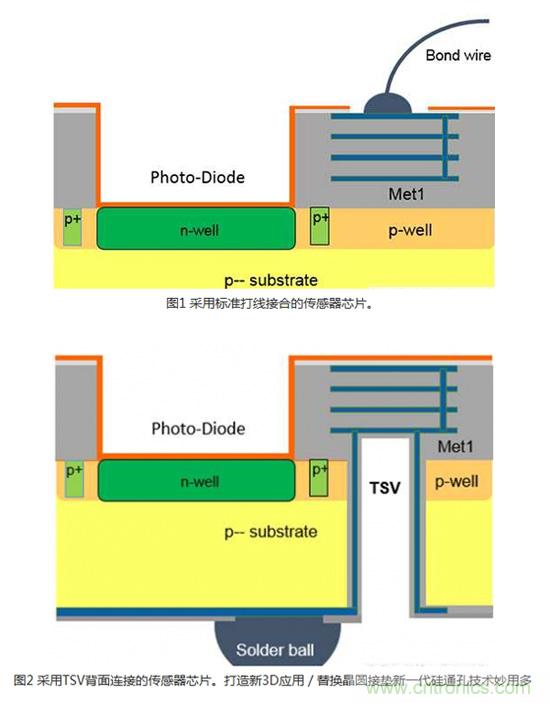

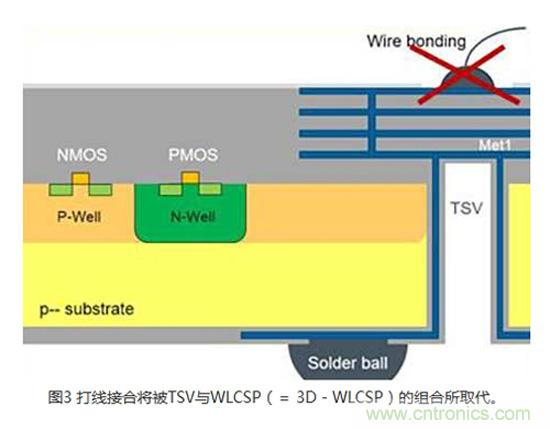

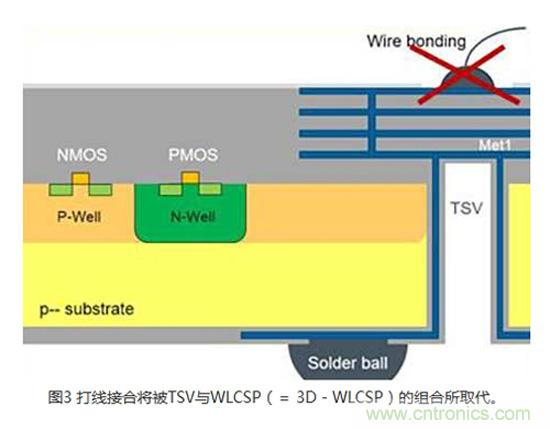

模擬3DIC技術(shù)通常是透過建造芯片正面到IC背面的電氣連接來實(shí)現(xiàn)傳感器應(yīng)用�����。 在許多傳感器應(yīng)用����,例如光學(xué)、化學(xué)���、氣體或壓力傳感器中���,感測區(qū)域是位在CMOS側(cè)(晶圓的頂端)。 芯片和導(dǎo)線架之間最常用的連接是打線接合(Wire bonding)(圖1)�����。 無論是使用塑料封裝����,或是將裸片直接接合在印刷電路(PCB)或軟性電路板上,對于某些會(huì)將感測區(qū)域暴露出來的應(yīng)用而言�,打線接合并非理想的解決方案。 采用專業(yè)晶圓代工業(yè)者的專有TSV技術(shù)�����,可以利用TSV、背面RDL和芯片級(jí)封裝(WLCSP)(圖2)來替代打線���。

類似于半導(dǎo)體技術(shù)�����,新的制程技術(shù)是透過使用更小的幾何形狀和設(shè)計(jì)規(guī)則(摩爾定律)提供更高的效能和更高的積體密度��,下一世代的TSV技術(shù)將優(yōu)于當(dāng)前可用的3DIC技術(shù)�。 一些專業(yè)晶圓代工業(yè)者正在開發(fā)下一世代TSV技術(shù)�����,其直徑(約40μm)將大幅縮小��,因此能提供更小的間距和更高的密度��,同時(shí)提供相同或甚至更好的模擬效能�����。 這種下一代TSV技術(shù)是新3D應(yīng)用的基礎(chǔ)��,晶圓代工業(yè)者正在開發(fā)提供全新服務(wù)�,像是所謂的「第三方晶圓上的接墊置換(Pad Replacement on 3rd Party Wafer)」或「主動(dòng)3D中介層(Active 3D Interposer)」等。

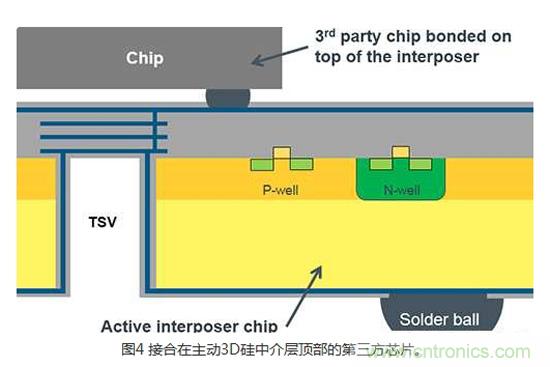

另外��,直徑和間距更為縮減的下一世代TSV技術(shù)�����,將能夠透過結(jié)合背面RDL和晶圓級(jí)芯片尺寸封裝(WLCSP的)TSV�,也就是所謂的3D-WLCSP來替換任何已經(jīng)處理和完成的晶圓的接墊(Pad)。 即使在制造過程完成后����,客戶也能夠靈活地決定產(chǎn)品是否應(yīng)在正面進(jìn)行打線接合,或者在背面使用WLCSP技術(shù)進(jìn)行凸塊封裝���。 這種新技術(shù)概念允許在任何芯片�,甚至是在第三方芯片上處理TSV�����,做為后處理步驟之一(后鉆孔概念)�����。 在TSV開發(fā)方式中�,其直徑和最小間距能極佳地匹配第三方芯片所采用制程的接墊需求(圖3)�����。

硅中介層為3DIC創(chuàng)新技術(shù)

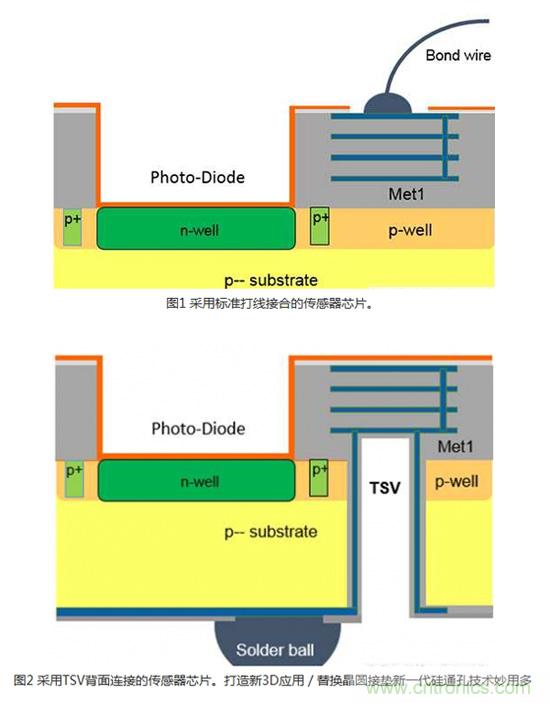

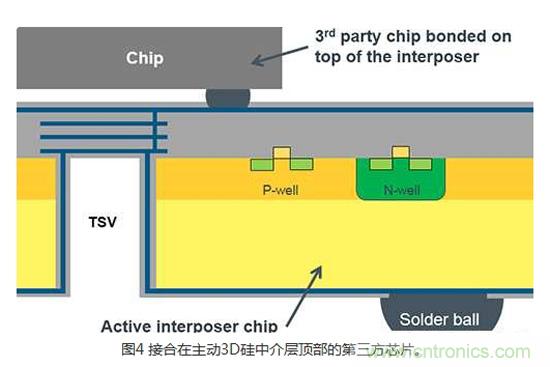

3DIC技術(shù)的另一個(gè)變化和極為創(chuàng)新的發(fā)展����,是硅中介層架構(gòu)(Silicon interposer architecture)�。 所謂的被動(dòng)3D硅中介層是用來產(chǎn)生一個(gè)從芯片的頂端到底部的簡單電氣連接。 所謂的主動(dòng)3D硅中介層能支持實(shí)現(xiàn)完整CMOS設(shè)計(jì)所需制程技術(shù)的所有被動(dòng)和主動(dòng)組件�����。

晶圓代工領(lǐng)導(dǎo)廠商提供3D中介層技術(shù)����,這些技術(shù)通常是基于0.18μm模擬專業(yè)制程,具有各種制程模塊����,例如金屬絕緣層金屬電容(MIM cap)�、高阻值多晶硅電阻(Poly resistor)、最多六個(gè)金屬層�����、厚頂金屬電感(Thick top metal)等,還有更多��。 主動(dòng)中介層具有正面和背面接墊��,前側(cè)接墊可用于組裝/堆棧任何種類的晶方�,例如傳感器或MEMS組件,背面接墊則主要用于電路板層級(jí)的整合(圖4)�����。 提供各種尺寸閘球和間距的WLCSP技術(shù)是由晶圓廠提供的額外服務(wù)�。 另一個(gè)選擇是,背面的接墊可以用于將更遠(yuǎn)的芯片附著于底部�。

設(shè)計(jì)套件整合加速開發(fā)時(shí)程

領(lǐng)先的模擬晶圓代工業(yè)者確實(shí)為IC開發(fā)提供了設(shè)計(jì)環(huán)境。 理想而言�,一些極少的產(chǎn)業(yè)基準(zhǔn)制程開發(fā)工具包(PDK)確實(shí)能提供創(chuàng)建復(fù)雜的混合訊號(hào)設(shè)計(jì)所需的全部建構(gòu)區(qū)塊,而這些設(shè)計(jì)是基于專業(yè)晶圓代工業(yè)者的先進(jìn)晶圓制程技術(shù)��,并且適用于所有主要的先進(jìn)CAD環(huán)境�。

透過些微的修改,已經(jīng)建立了3D積體參考設(shè)計(jì)流程���,這讓設(shè)計(jì)者得以對3D積體IC系統(tǒng)進(jìn)行全部功能和物理的驗(yàn)證�����。 PDK有助于針對裸片尺寸��、效能����、良率和更短的上市時(shí)間實(shí)現(xiàn)更有效的設(shè)計(jì),并為產(chǎn)品開發(fā)人員提供一個(gè)「首次就正確」設(shè)計(jì)的可靠途徑�。

改善尺寸/降低物料成本 3DIC技術(shù)發(fā)展?jié)摿?/strong>

3DIC技術(shù)廣泛用于內(nèi)存IC、影像傳感器及其他組件的堆棧���,并且已經(jīng)在數(shù)字世界成功獲得證明����。 在模擬和混合訊號(hào)主導(dǎo)的應(yīng)用中���,為客戶提供先進(jìn)的3DIC技術(shù)���,這是晶圓代工業(yè)者所面臨的主要挑戰(zhàn)。

藉由縮小TSV直徑���、減少TSV間距,并與晶圓級(jí)芯片尺寸技術(shù)結(jié)合,3D系統(tǒng)架構(gòu)得以能夠取代傳統(tǒng)2D系統(tǒng)級(jí)封裝解決方案���。 3DIC概念����,例如接墊替代技術(shù)或主動(dòng)中介層將大幅改善系統(tǒng)的外形尺寸���、提高效能��,并有助降低物料列表成本�����,這是物聯(lián)網(wǎng)領(lǐng)域中所有行動(dòng)設(shè)備���、穿戴式裝置或智能傳感器裝置的關(guān)鍵所在。