【導(dǎo)讀】數(shù)據(jù)轉(zhuǎn)換器充當(dāng)現(xiàn)實模擬世界與數(shù)字世界之間的橋梁已有數(shù)十年的歷史。從占用多個機架空間并消耗大量電能(例如DATRAC 11位50kSPS真空管ADC的功耗為500W)的分立元件起步,數(shù)據(jù)轉(zhuǎn)換器現(xiàn)已蛻變?yōu)楦叨燃傻膯涡酒琁C。

數(shù)據(jù)轉(zhuǎn)換器充當(dāng)現(xiàn)實模擬世界與數(shù)字世界之間的橋梁已有數(shù)十年的歷史。從占用多個機架空間并消耗大量電能(例如DATRAC 11位50kSPS真空管ADC的功耗為500W)的分立元件起步,數(shù)據(jù)轉(zhuǎn)換器現(xiàn)已蛻變?yōu)楦叨燃傻膯涡酒琁C。從第一款商用數(shù)據(jù)轉(zhuǎn)換器誕生以來,對更快數(shù)據(jù)速率的無止境需求驅(qū)動著數(shù)據(jù)轉(zhuǎn)換器不斷向前發(fā)展。ADC的最新化身是采樣速率達到GHz的RF采樣ADC。

早先的ADC設(shè)計使用的數(shù)字電路非常少,主要用于糾錯和數(shù)字驅(qū)動器。新一代GSPS(每秒千兆樣本)轉(zhuǎn)換器(也稱為RF采樣ADC)利用尖端65nm CMOS技術(shù)實現(xiàn),可以集成許多數(shù)字處理功能來增強ADC的性能。這樣,數(shù)據(jù)轉(zhuǎn)換器便從20世紀(jì)90年代中期和21世紀(jì)早期的大A (模擬)小D(數(shù)字)式ADC變身為現(xiàn)在的小A大D式ADC。

這并不意味著模擬電路及其性能已衰退,而是說數(shù)字電路的數(shù)量已大幅增加,與模擬性能互為補充。這些增加的特性使得ADC能夠在ADC芯片中快速執(zhí)行大量數(shù)字處理,分擔(dān)FPGA的一些數(shù)字處理負(fù)荷。這就為系統(tǒng)設(shè)計人員開啟了許多其它可能性?,F(xiàn)在,采用這些先進的新型GSPS ADC,系統(tǒng)設(shè)計人員針對各種各樣的平臺只需設(shè)計一種硬件,然后高效率地利用軟件重新配置該硬件,便可適應(yīng)新的應(yīng)用。

增強的高速數(shù)字處理

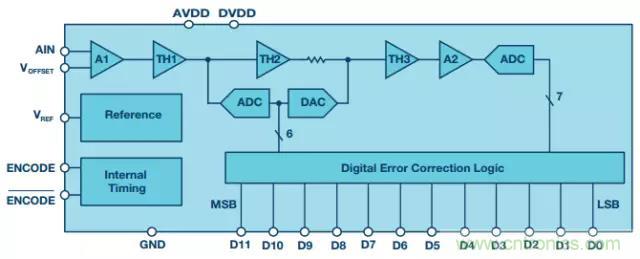

不斷縮小的CMOS工藝尺寸和先進的設(shè)計架構(gòu)相結(jié)合,意味著ADC終于也能利用數(shù)字處理技術(shù)來改善性能。該突破是在20世紀(jì)90年代早期實現(xiàn)的,自此之后,ADC設(shè)計人員再也沒有回頭。隨著硅工藝的改進(從0.5μm、0.35μm、0.18μm到65nm),轉(zhuǎn)換速度也得到提高。但是,幾何尺寸縮小使得晶體管變小,雖然速度更快(因而帶寬更高),但就模擬設(shè)計性能而言,某些特性變得略差,例如Gm(跨導(dǎo))。以前,這要通過增加更多校正邏輯來補償。然而,那時的硅仍很昂貴,導(dǎo)致ADC內(nèi)部的數(shù)字電路數(shù)量相對較少。圖1所示為一個實例的功能框圖。

圖1:集成極少數(shù)字糾錯邏輯的早期單芯片ADC

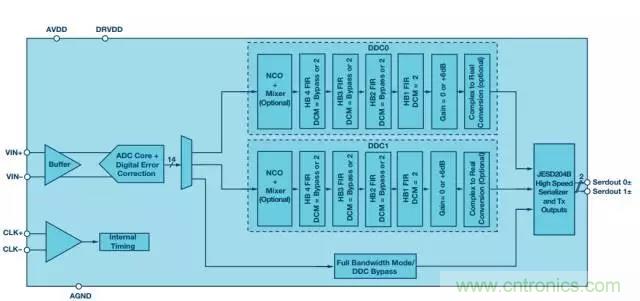

隨著硅技術(shù)發(fā)展到深亞微米尺寸(如65nm),數(shù)據(jù)轉(zhuǎn)換器除了內(nèi)核能夠跑得更快(1GSPS或更高)以外,規(guī)模經(jīng)濟性還使其可以增加大量數(shù)字處理。這是再次審視后發(fā)現(xiàn)的一個突破性進展。通常,根據(jù)系統(tǒng)性能和成本要求,數(shù)字信號處理是由ASIC或FPGA處理。ASIC是專用電路,開發(fā)需要耗費大量資金。因此,設(shè)計人員通常會讓ASIC設(shè)計長期運行,以擴大ASIC開發(fā)的投資回報。FPGA比ASIC便宜,不需要巨額開發(fā)預(yù)算。然而,由于FPGA追求支持所有應(yīng)用,所以其信號處理能力會受到速度和功效的限制。這是可以理解的,因為它具備ASIC所不具備的靈活性和重新配置能力。圖2所示為一個具有可配置數(shù)字處理模塊的RF采樣ADC(也稱為GSPS ADC)的功能框圖。

圖2:集成數(shù)字處理模塊的GSPS ADC

新一代GSPS ADC將徹底改變無線電設(shè)計,因為其為設(shè)計提供了極大的靈活性,下面將討論其中幾點。

高速數(shù)字處理

早先的無線電利用模擬混頻器和級聯(lián)數(shù)字下變頻器(DDC)的混合結(jié)構(gòu)來將信號降頻至基帶以供處理,這涉及到大量硬件(模擬混頻)和電源(模擬域和ASIC/FPGA中的DDC域)。新一代RF采樣ADC的出現(xiàn),使得DDC可以在充斥定制數(shù)字邏輯的ADC內(nèi)部高速運行,這意味著處理的功效要高得多。

通過JESD204B提供I/O靈活性

新一代RF采樣ADC不僅具有GSPS采樣能力,而且拋棄了過時的LVDS輸出,轉(zhuǎn)而采用高速串行接口。新的JEDEC JESD204B規(guī)范允許數(shù)字輸出數(shù)據(jù)通過CML(電流模式邏輯)以每通道最高12.5Gbps的高通道速率傳輸,這就提供了高水平的I/O靈活性。例如,ADC既可在全帶寬模式下工作并在多個通道上傳輸數(shù)字?jǐn)?shù)據(jù),也可使用其中一個可用DDC并在一個通道上傳輸抽取的/經(jīng)處理的數(shù)據(jù),只要輸出通道速率低于每通道12.5Gbps即可。

可擴展的硬件設(shè)計

在硬件設(shè)計方面,DDC的使用提供了更高的靈活性。系統(tǒng)設(shè)計人員現(xiàn)在可以凍結(jié)ADC和FPGA的硬件設(shè)計,然后只需進行細(xì)微的變更,重新配置系統(tǒng)便可適應(yīng)不同的帶寬,只要ADC能夠支持。例如,利用所提供的DDC,一個無線電既可設(shè)計為全帶寬ADC(RF采樣ADC),也可設(shè)計為IF采樣ADC(中頻ADC)。唯一的系統(tǒng)變更將是在RF側(cè),針對IF ADC可能需要增加極少的混頻。絕大部分變更將是在軟件中進行,配置ADC以支持新的帶寬。不過,ADC+FPGA硬件設(shè)計可以基本保持不變。這就形成了一個基準(zhǔn)硬件設(shè)計,其可以適用于許多平臺,軟件要求是其唯一變數(shù)。

更多其他特性

深亞微米CMOS工藝帶來的高集成度開創(chuàng)了ADC的新時代——越來越多的特性被內(nèi)置于ADC中。其中包括支持高效AGC(自動增益控制)的快速檢測CMOS輸出,以及信號監(jiān)控(如峰值檢波器)。所有這些特性都有助于系統(tǒng)設(shè)計,減少外部器件,縮短設(shè)計時間。

通信接收機設(shè)計更加靈活

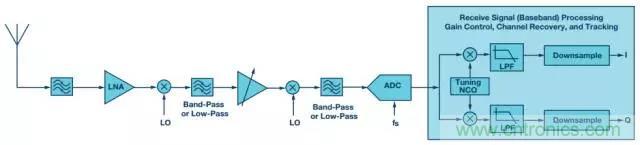

一個非常常見的ADC使用案例是通信接收機系統(tǒng)設(shè)計。圖3所示為較早一代無線電接收機的功能框圖。

圖3:用于蜂窩無線電的寬帶數(shù)字接收機

GSM無線電接收機的一般規(guī)格要求ADC的噪聲頻譜密度(NSD)至少為153 dBFS/Hz或更佳。眾所周知,NSD與ADC的SNR存在如下關(guān)系:

NSD = SNR + 10 log10 (fs ÷ 2)

其中:SNR的單位為dBFS

fs=ADC采樣速率

常規(guī)軟件無線電設(shè)計

在寬帶無線電應(yīng)用中,對高達50MHz的頻段同時進行采樣和轉(zhuǎn)換并不是罕見的事。為了正確地對50MHz頻段進行數(shù)字化,ADC將需要至少5倍的采樣帶寬,即至少約250 MHz。將這些數(shù)值代入上式,ADC達到–153dBFS/Hz NSD要求所需的SNR約為72dBFS。

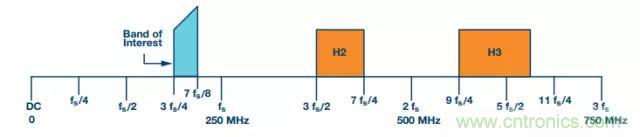

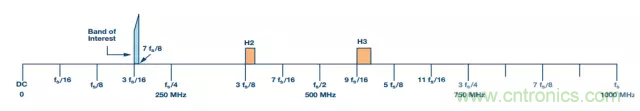

圖4顯示了利用250MSPS ADC對50MHz頻段有效采樣所采用的頻率規(guī)劃。該圖還顯示了二次和三次諧波頻段的位置。

圖4:采用250 MSPS ADC的50MHz寬帶無線電的頻率規(guī)劃

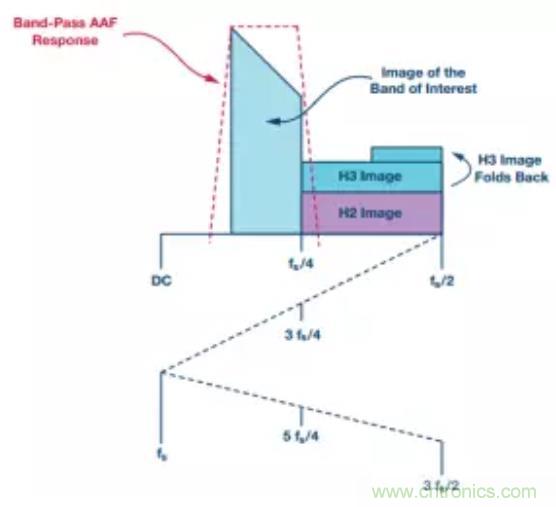

ADC采樣的頻率都會落在ADC的第一奈奎斯特(DC—125MHz)頻段。這種現(xiàn)象稱為混疊,因此這些頻率包括目標(biāo)頻段、折回或混疊到第一奈奎斯特頻段的二次和三次諧波,如圖5所示,說明如下:

圖5:顯示在第一奈奎斯特區(qū)中的可用頻段,含二次和三次諧波

除NSD規(guī)格外,GSM、LTE和LTE-A等蜂窩通信標(biāo)準(zhǔn)還對SFDR(無雜散動態(tài)范圍)有其它嚴(yán)格要求。這給前端設(shè)計帶來了很大壓力;對目標(biāo)頻段中的信號進行采樣時,前端能夠衰減干擾信號。

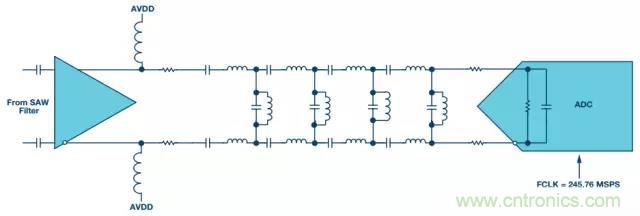

注意,常規(guī)無線電前端設(shè)計的SFDR規(guī)格,即抗混疊濾波器要求很難達到。滿足SFDR要求的最佳抗混疊濾波器(AAF)解決方案是采用帶通濾波器。通常,此類帶通濾波器為五階或更高階。一款可以滿足此類應(yīng)用的SNR(或NSD)和SFDR要求的合適ADC是16位250 MSPS模數(shù)轉(zhuǎn)換器AD9467,采用AD9467的蜂窩無線電應(yīng)用前端設(shè)計將類似圖6所示。

圖6:包括放大器、抗混疊濾波器和250 MSPS ADC的前端設(shè)計

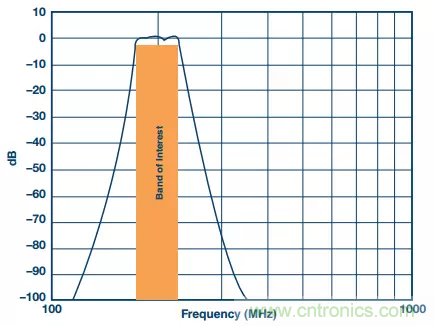

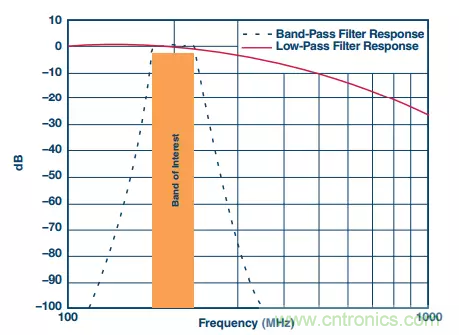

滿足SFDR要求的AAF的頻率響應(yīng)如圖7所示。此系統(tǒng)的實現(xiàn)不是不可能,但存在很多設(shè)計難題。帶通濾波器涉及到大量器件,是最難實現(xiàn)的濾波器之一。器件選擇非常重要,任何不匹配都會導(dǎo)致ADC輸出中出現(xiàn)不需要的雜散(SFDR)。除了非常復(fù)雜以外,任何阻抗不匹配都會影響濾波器的增益平坦度。為了優(yōu)化該濾波器設(shè)計以滿足帶通平坦度和阻帶抑制要求,需要做相當(dāng)多的設(shè)計工作。

圖7:圖6所示前端的帶通響應(yīng)

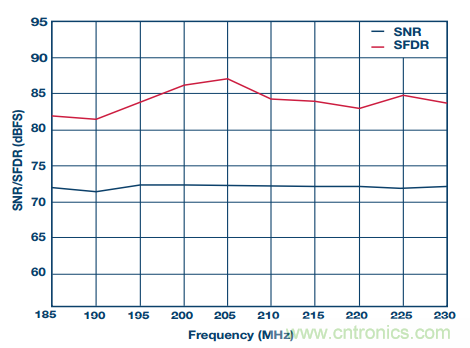

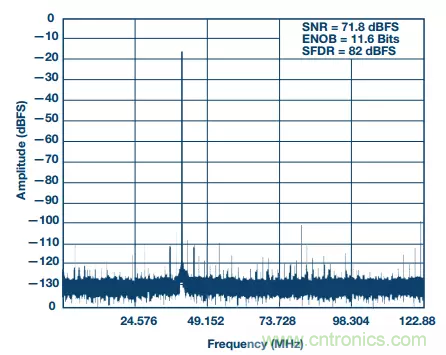

雖然這種無線電設(shè)計的前端實現(xiàn)很復(fù)雜,但它確實有效,如圖8中的SNR/SFDR性能與頻率的關(guān)系曲線所示。

圖8:圖6所示16位250 MSPS ADC設(shè)計的SNR/SFDR與頻率的關(guān)系

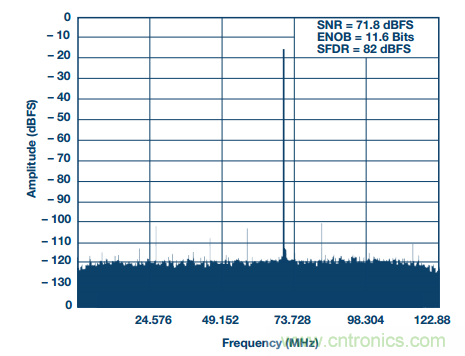

205 MHz時的FFT如圖9所示。然而,系統(tǒng)實現(xiàn)因為下列原因而變得復(fù)雜:

1、濾波器設(shè)計。

2、FPGA必須提供專用I/O端口來捕捉LVDS數(shù)據(jù)(16對),這會使PCB設(shè)計復(fù)雜化。

3、FPGA還需要留出一些處理能力來進行數(shù)字信號處理。

圖9:圖6所示16位250 MSPS ADC設(shè)計在205MHz時的FFT

RF采樣ADC簡化并加速設(shè)計

RF采樣ADC方法采用過采樣技術(shù),然后抽取數(shù)據(jù)以改善動態(tài)范圍。深亞微米CMOS技術(shù)提供的速度優(yōu)勢與高數(shù)字集成度能力相結(jié)合,開創(chuàng)了RF采樣ADC的新紀(jì)元,它現(xiàn)在能執(zhí)行大量重要處理,而不只是簡單的模數(shù)轉(zhuǎn)換。這些ADC擁有更多的數(shù)字電路,支持高速信號處理。

對系統(tǒng)設(shè)計人員來說,這意味著實現(xiàn)起來很簡單,并可獲得其它靈活性,而這在以前一直屬于ASIC/FPGA領(lǐng)域。上面的無線電設(shè)計示例也可以利用RF采樣ADC實現(xiàn)。AD9680(14位、1GSPS JESD204B、雙通道ADC)是一款新型RF采樣ADC,而且還有其它數(shù)字處理能力。此ADC在全速率(1GSPS)時的NSD約為67dBFS。現(xiàn)在還不用擔(dān)心SNR,因為稍后就會知道。目標(biāo)頻段與之前相同,但關(guān)于RF采樣ADC奈奎斯特區(qū)的頻率規(guī)劃要簡單得多,如圖10所示。這是因為該ADC的采樣頻率(1GHz)是上述例子(250MHz)的4倍。

圖10:采用1GSPS ADC的50MHz寬帶無線電的頻率規(guī)劃

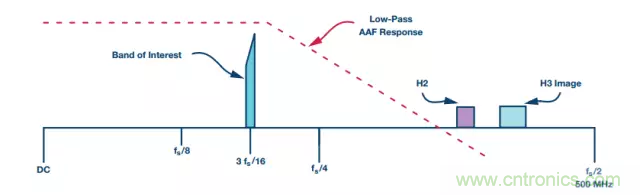

從頻率規(guī)劃可知,它實現(xiàn)起來要比圖4所示簡單得多。AAF要求也有所降低,如圖11所示。這種方法的思想是使用簡單的模擬前端設(shè)計,而把數(shù)字處理模塊留在RF采樣ADC內(nèi)以執(zhí)行繁重的信號處理。

圖11:1GSPS ADC的AAF移植

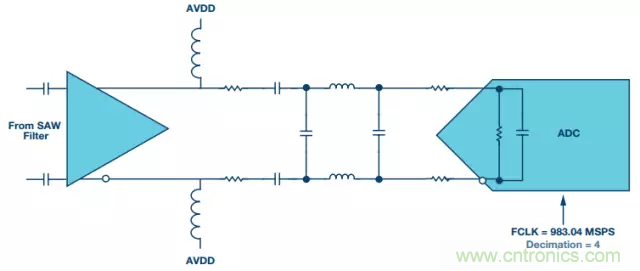

過采樣的好處是將該頻率規(guī)劃擴展到整個奈奎斯特區(qū),即比250 MSPS奈奎斯特區(qū)大4倍的區(qū)域。這樣就大大降低了濾波要求,一個簡單的三階低通濾波器就足夠,而無需250MSPS ADC方案所用的帶通濾波器。采用RF采樣ADC的簡化AAF實現(xiàn)方案如圖12所示。

圖12:包括放大器、抗混疊濾波器和1GSPS ADC的前端設(shè)計

圖13所示為低通濾波器響應(yīng)性能。同時顯示了帶通濾波器以作比較。低通濾波器的帶通平坦度更佳,而且就器件不匹配而言更容易管理。其阻抗匹配也更容易實現(xiàn)。此外,由于器件數(shù)量更少,系統(tǒng)成本也更低。簡化的前端設(shè)計可縮短設(shè)計時間。

由于現(xiàn)代RF采樣ADC集成了非常多的數(shù)字處理功能,因此數(shù)字處理可以在ADC內(nèi)部高速進行。如上文所述,這樣可以實現(xiàn)高功效和高I/O效率的設(shè)計?,F(xiàn)在,系統(tǒng)設(shè)計人員可以利用其FPGA的未使用JESD204B收發(fā)器來服務(wù)來自其它RF采樣ADC的數(shù)據(jù),這些ADC已對數(shù)據(jù)進行處理(模數(shù)轉(zhuǎn)換、濾波和抽?。?。這樣就可以高效使用FPGA資源,同時提高無線電設(shè)計的通道數(shù)。

圖13:250 MSPS ADC和1GSPS ADC的AAF比較

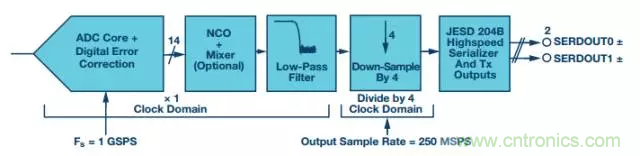

利用DDC,ADC可以用作數(shù)字混頻器來調(diào)諧至設(shè)計需要的任何中頻。本例同樣使用上述頻率規(guī)劃。采用¼抽取選項和實數(shù)混頻來演示ADC性能,如圖14所示。

圖14:RF采樣速率為1GSPS,DDC設(shè)置為1/4抽取

在正?;蛉珟捘J较拢珹D9680的SNR約為66dBFS至67dBFS。當(dāng)DDC處于工作狀態(tài)且抽取比為¼時,還可以獲得6dB的額外處理增益[3]。這樣可以確保動態(tài)范圍性能保持不變。由于RF采樣ADC以4倍原始采樣速率采樣,因此諧波會擴展(如圖10所示)。RF采樣ADC中的DDC確保抽取濾波器以數(shù)字方式衰減干擾信號。然而,屬于目標(biāo)頻段內(nèi)的諧波(更高階或其它)仍會顯示,因為DDC允許其通過。引起它的原因可以是放大器偽像或低通濾波器沒有足夠的衰減能力。低通濾波器可以根據(jù)系統(tǒng)要求重新設(shè)計,以滿足其它雜散性能要求。

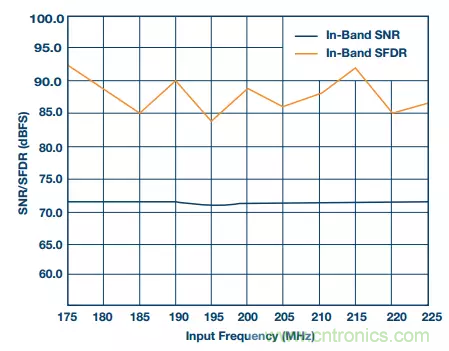

圖15顯示了1GSPS ADC的SNR/SFDR與輸入頻率的關(guān)系。數(shù)據(jù)清楚地表明,DDC的使用使得SNR提高6dB(原因是處理增益),SFDR也得到改善。在全帶寬模式下運行時,SFDR通常受二次或三次諧波限制,而在DDC模式(¼抽取)下,限制因素為最差其它諧波。

圖15. 圖12所示14位1 GSPS ADC設(shè)計的SNR/SFDR與頻率的關(guān)系

抽取輸出的FFT如圖16所示。使用DDC時,必須采取措施確保目標(biāo)頻段得到正確處理。本例中,NCO調(diào)諧至200MHz,使得目標(biāo)頻段落在抽取奈奎斯特區(qū)的中央。DDC可以方便地消除頻譜中不需要的頻率。因此,F(xiàn)PGA的處理開銷更低。

圖16:1/4抽取時1GSPS ADC的205MHz FFT;NCO調(diào)諧至200 MHz

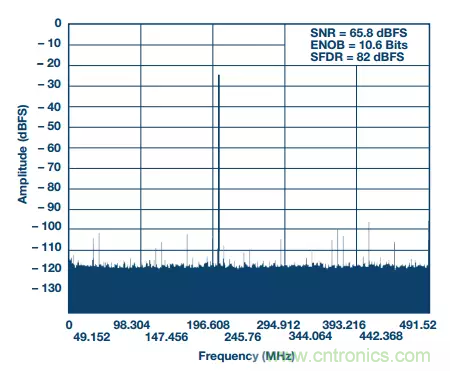

作為對比,圖17顯示了AD9680在正常(全帶寬)工作模式下的FFT。

圖17:全帶寬模式下1 GSPS ADC的205 MHz FFT

通過這些圖形可知,DDC除了能改善帶內(nèi)噪聲性能之外,還能提供無干擾諧波的清潔頻譜。由于DDC對數(shù)據(jù)進行濾波和抽?。ㄖ?50MSPS),因此還會降低輸出通道速率,這使得JESD204B串行接口具有更靈活的選項。系統(tǒng)設(shè)計人員可以選擇高通道速率(較昂貴)、低I/O數(shù)FPGA或低通道速率(較便宜)、高I/O數(shù)FPGA。

結(jié)論

RF采樣ADC為系統(tǒng)設(shè)計提供了獨特的優(yōu)勢,而在幾年前,這是無法實現(xiàn)的。業(yè)界期望加速基礎(chǔ)設(shè)施的設(shè)計和實現(xiàn),以便應(yīng)對更高的帶寬需求。設(shè)計時間和預(yù)算不斷縮減,對可擴展、可重新配置、更多由軟件驅(qū)動的架構(gòu)的需求催生出新的設(shè)計范式。更高帶寬的需求伴隨著更高容量的需求。這就給FPGA I/O帶來了更大的壓力,而RF采樣ADC可以利用內(nèi)部DDC予以化解。