【導讀】在使用同一時鐘源產(chǎn)生多個時鐘時,一個常見的問題是噪聲,通常表現(xiàn)為存在于噪底之上的雜散,這是因為單一時鐘源被倍頻或分頻為多個時鐘。那么使用多個時鐘時,該如何改善系統(tǒng)性能?

在使用同一時鐘源產(chǎn)生多個時鐘時,一個常見的問題是噪聲,通常表現(xiàn)為存在于噪底之上的雜散,這是因為單一時鐘源被倍頻或分頻為多個時鐘。偏移各時鐘的相鄰沿可以降低噪聲雜散,或者完全消除雜散,這具體取決于系統(tǒng)的時序裕量。這一現(xiàn)象是一個時間變量系統(tǒng),其中時鐘信號的破壞與時域中的干擾位置相關。干擾位置是固定的,因此時鐘的破壞程度與干擾的幅度成比例,就像在線性系統(tǒng)中一樣。

來,送個例子,以時鐘發(fā)生器AD9516的兩路輸出為例加以說明吧~

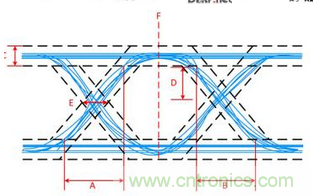

一路100MHz輸出連接到一個ADC,另一路2 5 M H z 輸出(1/4&TImes;fSAMPLE)為一個FPGA提供時鐘信號。兩路輸出時鐘的上升沿和下降沿幾乎是同時的,其結(jié)果是發(fā)生耦合效應,因為兩個快速運動的高帶寬時鐘沿每隔10ns出現(xiàn)一次,而不是所需要的一個時鐘沿。在此躍遷期間,內(nèi)部或外部的噪聲必須很低,因為抖動或噪聲存在于時鐘的躍遷區(qū)時會破壞ADC的時序。提高壓擺率以加快時鐘沿(閾值區(qū)相應變?。┎豢杀苊獾貢s短噪聲在閾值期間存在的時間,從而有效降低引入系統(tǒng)的均方根抖動量。在時鐘的穩(wěn)態(tài)期間(高電平和低電平),時鐘噪聲不起作用。因此,只需延遲25MHz或100MHz時鐘便能展開二者的時間,移動干擾的位置。換言之,應將一個時鐘的躍遷沿安排在另一個時鐘的穩(wěn)態(tài)期間出現(xiàn)。

本質(zhì)上,這里涉及到一條走線與另一條相鄰走線由于串擾而引起的抖動(噪聲)。如果一條走線攜帶一個信號,而相鄰的并行走線攜帶一個變化電流,則信號走線中將產(chǎn)生一個電壓;如果它是時鐘信號,則時鐘沿出現(xiàn)的時間將被調(diào)制。如果這些時鐘沿出現(xiàn)在幾乎同一時間,就會發(fā)生問題。