【導讀】電源噪聲是一種常見且不受歡迎的電氣現(xiàn)象。如果不降低噪聲,其會對敏感的醫(yī)療、測試測量、航空航天和國防系統(tǒng)的應用性能產(chǎn)生不利影響。

當今的高精度模擬信號鏈系統(tǒng)需要直流/直流開關穩(wěn)壓器產(chǎn)生穩(wěn)壓電源軌,為低噪聲應用中的模數(shù)轉(zhuǎn)換器(ADC)、數(shù)模轉(zhuǎn)換器(DAC)、現(xiàn)場可編程門陣列(FPGA)及其子系統(tǒng)供電。盡管直流/直流開關穩(wěn)壓器具有高工作效率,它們的開關操作會導致較大的不連續(xù)電流,從而產(chǎn)生較高的輸入和輸出電壓紋波、頻率尖峰和寬帶噪聲。如果不將這些不連續(xù)電流控制在ADC或DAC的最低有效位毫伏范圍內(nèi),它會影響系統(tǒng)精度。

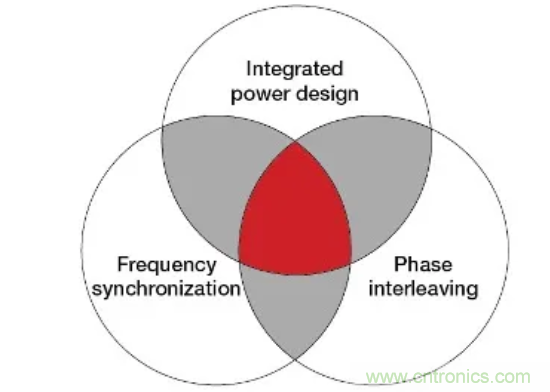

本文主要介紹降壓電源模塊降低噪聲的三種方法:通過集成模塊設計消除寄生效應,通過頻率同步降低不良拍頻和誤差,以及通過相位交錯降低輸入紋波電流和輸出電壓紋波。如圖1所示,具有所有三種功能的直流/直流降壓電源模塊可以顯著降低低噪聲應用中電源的噪聲。

圖1: 用于降低噪聲的直流/直流降壓模塊理想特性維恩圖

通過集成模塊設計消除寄生效應

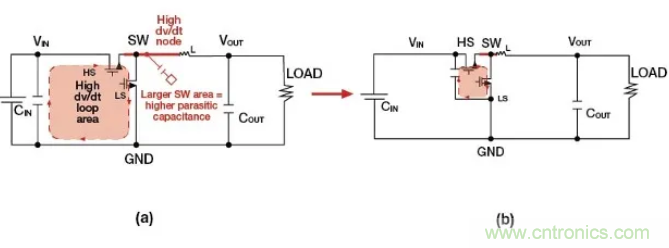

開關電源的大多數(shù)噪聲問題都與設計中的寄生元件有關。使用直流/直流開關穩(wěn)壓器時,必須添加外部元件(例如輸入電容器、電感器和輸出電容器)來形成閉環(huán)。將這些外部元件放在電路板上遠離開關穩(wěn)壓器的位置時,會導致VIN和SW節(jié)點上產(chǎn)生電路板寄生效應。這類寄生效應會產(chǎn)生一個高瞬態(tài)電流(di/dt)環(huán)路,如圖2所示。如果開關期間電流突然接通或斷開,環(huán)路中會產(chǎn)生高頻振鈴(開關噪聲)。

集成控制器、FET、電感和旁路電容的降壓電源模塊采用優(yōu)化布局設計,可幫助更大程度減少此類電路板寄生效應。降壓電源模塊的高級封裝結(jié)構使集成的旁路電容器更接近VIN和VOUT引腳,而且電感的位置更接近SW節(jié)點(在某些情況下,以3D結(jié)構樣式放置在轉(zhuǎn)換器頂部)。內(nèi)部元件的總體布局和布線設計可以減少高di/dt環(huán)路面積和瞬態(tài)電壓(dv/dt)節(jié)點面積,從而更大程度減小輸入和輸出紋波電壓。

圖2:分立式轉(zhuǎn)換器(a)與降壓電源模塊(b)的di/dt環(huán)路

通過頻率同步降低不良拍頻和誤差

在同一應用中設計多個開關轉(zhuǎn)換器時,如何降低輸入和輸出噪聲是一項挑戰(zhàn)。當轉(zhuǎn)換器的開關頻率隨輸入電壓和輸出負載變化時,情況更加復雜。即使每個轉(zhuǎn)換器都在固定頻率下工作,不同轉(zhuǎn)換器的頻率容差也會導致不良拍頻(開關頻率之差)。

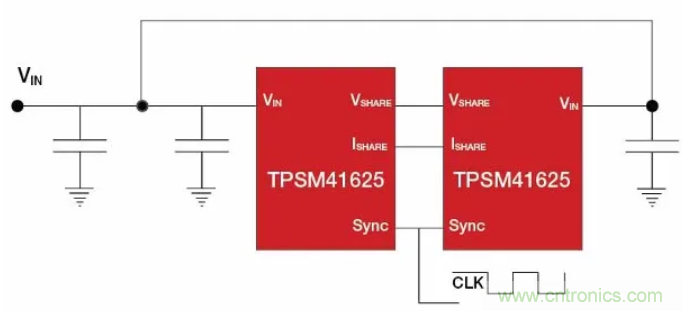

為了克服開關頻率誤差和拍頻的問題,一些降壓電源模塊提供了一個外部SYNC引腳,可將一個或多個穩(wěn)壓器同步到一個共同的系統(tǒng)時鐘來協(xié)同工作。如圖3所示,將所有模塊與外部時鐘同步可以降低特定系統(tǒng)時鐘頻率下的輸入電流和電壓紋波,從而進一步減少對噪聲濾波的需要,并降低模塊的總電容值。將所有降壓電源模塊與中央系統(tǒng)時鐘同步,也可以防止該模塊干擾整個系統(tǒng)的敏感模擬或數(shù)字部分。

圖3:與系統(tǒng)時鐘同步的兩個降壓電源模塊

通過相位交錯降低輸入紋波電流和輸出電壓紋波

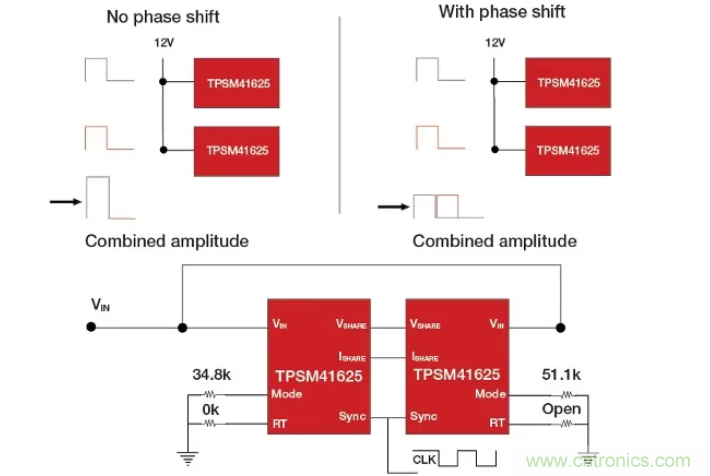

同步所有降壓電源模塊有助于降低噪聲并避免拍頻,但有時會對輸入電容器產(chǎn)生應力。在同步系統(tǒng)中,所有降壓穩(wěn)壓器都會在系統(tǒng)時鐘開始時產(chǎn)生脈沖電流,這會導致較大的均方根電流,從而對輸入電容器產(chǎn)生熱應力。它也會導致系統(tǒng)中的噪聲峰值。

為了解決這個問題,可以考慮相位交錯,即在系統(tǒng)時鐘周期內(nèi),使時鐘沿在不同時間延遲到達不同的降壓電源模塊。這樣一來,在無相移和有相移兩種配置下(如圖4所示),輸入端對脈沖電流的需求會發(fā)生時間上的偏移。這一措施可降低特定頻率下的輸入電流和輸出電壓紋波,從而減少噪聲濾波的工作量。

圖4:具有180度相移的同步TPSM41625模塊

結(jié)束語

低噪聲開關電源有很多種。如果您喜歡使用模塊并知道需要哪一種,則可以有效地降低電源噪聲。在為ADC、DAC和FPGA設計下一代低噪聲多軌電源時,請考慮選擇具有頻率同步和相位交錯的降壓電源模塊。

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯(lián)系小編進行處理。

推薦閱讀: