【導(dǎo)讀】對(duì)于機(jī)器人而言�����,什么才最重要?能夠暴力彈跳的復(fù)雜機(jī)械裝置�����?各類價(jià)格昂貴的傳感器����?不對(duì),最重要的是能在復(fù)雜的環(huán)境中完成特定工作���,為了實(shí)現(xiàn)這目標(biāo)�����,機(jī)器人要眼觀六路�����,耳聽八方�,行走天下。而這一切都離不開一顆強(qiáng)勁的大腦——高性能計(jì)算平臺(tái)和高效算法��。

通用處理器在計(jì)算性能和能效上越來(lái)越難以滿足日益龐大��、多樣化的數(shù)據(jù)處理需求���。 借助由GPU�、FPGA和其他智能引擎等協(xié)處理器與CPU一起組成的異構(gòu)計(jì)算平臺(tái)來(lái)提升計(jì)算性能���,已成為當(dāng)下學(xué)術(shù)界和工業(yè)界的研究熱點(diǎn)��。 異構(gòu)計(jì)算作為一種特殊的并行計(jì)算方式�,能夠根據(jù)每個(gè)計(jì)算子系統(tǒng)的結(jié)構(gòu)特點(diǎn)為其分配不同的計(jì)算任務(wù)���,在提高計(jì)算性能����、能效比和實(shí)時(shí)性保障方面體現(xiàn)出傳統(tǒng)架構(gòu)所不具備的優(yōu)勢(shì),逐漸在各種計(jì)算需求量較大的場(chǎng)合得到應(yīng)用����。針對(duì)數(shù)據(jù)中心場(chǎng)景,英特爾已經(jīng)宣布要通過(guò)Xeon+FPGA平臺(tái)和Xeon Phi系列產(chǎn)品來(lái)推動(dòng)異構(gòu)計(jì)算的實(shí)施��。

那么��,在我們所關(guān)心的機(jī)器人領(lǐng)域�����,情況又是如何�����?

一����、機(jī)器人需要怎樣的計(jì)算平臺(tái)

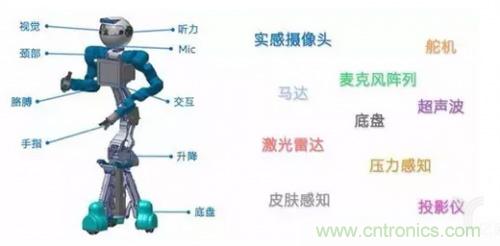

機(jī)器人是復(fù)雜的機(jī)電一體化裝置�,綜合運(yùn)用了機(jī)械與精密機(jī)械、微電子與計(jì)算機(jī)�、自動(dòng)控制與驅(qū)動(dòng)����、傳感器與信息處理以及人工智能等多學(xué)科的最新研究成果�。

機(jī)器人系統(tǒng)和系統(tǒng)中的傳感器

為了將這些成果融合起來(lái),真正形成認(rèn)知�����、感受和行動(dòng)的能力����,使機(jī)器人能夠理解并應(yīng)對(duì)真實(shí)的世界,準(zhǔn)確完成操作任務(wù)���,其搭載的計(jì)算平臺(tái)需滿足多種要求�,包括:

1)感知能力:具備豐富的I/O接口�����,支持USB 3�����、UART、I2C等多種I/O協(xié)議�,用以接收各類傳感器數(shù)據(jù)。

2)控制能力:能夠控制各個(gè)運(yùn)動(dòng)部位�,如底盤、手臂���、手指和頭部����,完成多個(gè)維度的動(dòng)作��,并且具備實(shí)時(shí)性和安全性方面的保障����。

3)計(jì)算能力:既要應(yīng)對(duì)大量數(shù)據(jù)的處理開銷,更要滿足各類智能算法巨大的計(jì)算需求����。

4)功耗控制:要在滿足以上能力的同時(shí)盡可能降低功耗�����,避免成為電池殺手���。

5)易用性:必須提供友好的編程模型���,使機(jī)器人的應(yīng)用開發(fā)快速���、準(zhǔn)確。

現(xiàn)有的計(jì)算平臺(tái)很難滿足以上需求���,搭建適用于機(jī)器人的異構(gòu)計(jì)算平臺(tái)已經(jīng)迫在眉睫����!CPU+FPGA的方案以其獨(dú)特的優(yōu)勢(shì)進(jìn)入我們眼簾����。

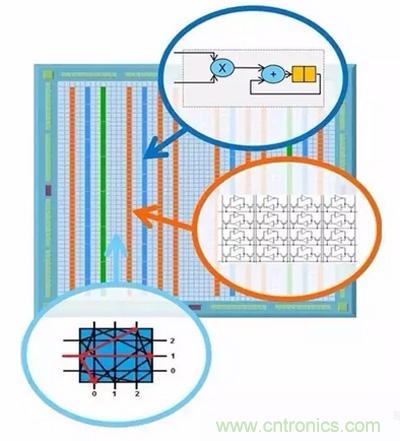

二、什么是FPGA

自1985年問(wèn)世以來(lái)����,F(xiàn)PGA這種可編程邏輯器件憑借在性能、上市時(shí)間����、成本、穩(wěn)定性和長(zhǎng)期維護(hù)方面的優(yōu)勢(shì)����,在通信�����、醫(yī)療����、工控和安防等領(lǐng)域占有一席之地���。特別是近兩年���,隨著云計(jì)算、高性能計(jì)算和人工智能的繁榮����,擁有先天優(yōu)勢(shì)的FPGA更是得到了前所未有的關(guān)注。

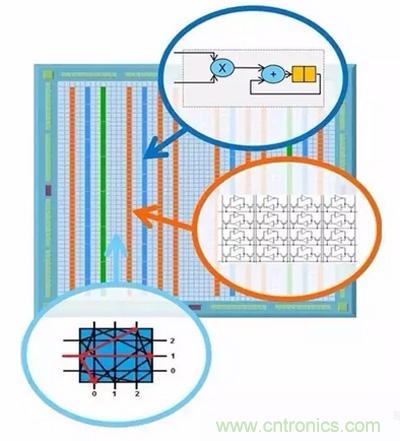

FPGA由六部分組成:可編程輸入/輸出單元�����、基本可編程邏輯單元�����、嵌入式塊RAM����、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核����。 英特爾首席執(zhí)行官科再奇曾這樣描述:“你可以把FPGA想象成一堆gate,能夠隨時(shí)編程��。FPGA可以用作多個(gè)領(lǐng)域的加速器�,例如在加密的同時(shí)進(jìn)行面部搜索,并能在微秒內(nèi)重新編程�����。其成本遠(yuǎn)低于大規(guī)模單個(gè)定制部件�,并具有更高的靈活性。”

隨著工藝的發(fā)展�,技術(shù)的進(jìn)步,F(xiàn)PGA的性能��、指標(biāo)都達(dá)到了新高度�。新的Arria10系列FPGA和SoC功耗比前一代FPGA和SoC低40%,具有業(yè)界唯一的硬核浮點(diǎn)數(shù)字信號(hào)處理(DSP)模塊����,其速率高達(dá)每秒1.5萬(wàn)億次浮點(diǎn)運(yùn)算(1.5 TFLOPS)����。

FPGA的結(jié)構(gòu)

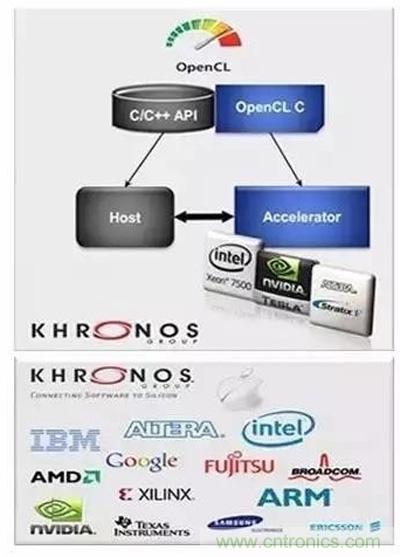

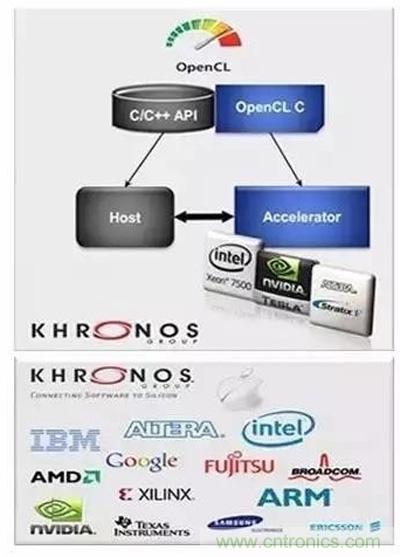

即便擁有上述優(yōu)勢(shì)�,傳統(tǒng)上FPGA的開發(fā)難度還是令諸多程序員望而卻步。然而����,隨著OpenCL標(biāo)準(zhǔn)的出現(xiàn),F(xiàn)PGA的應(yīng)用門檻正在大幅降低��?�;贠penCL的開發(fā)框架���,用戶可以擺脫傳統(tǒng)的基于硬件描述語(yǔ)言(HDL)的開發(fā)流程����,轉(zhuǎn)而采用更高效����、也更符合廣大程序員背景的軟件開發(fā)流程。

OpenCL標(biāo)準(zhǔn)是第一個(gè)開放�����、免版稅�����、統(tǒng)一的編程模型�����,能夠在異構(gòu)系統(tǒng)上加速算法實(shí)現(xiàn)��,支持使用基于C的編程語(yǔ)言進(jìn)行跨平臺(tái)開發(fā) �����,例如CPU���、GPU�����、DSP和FPGA��。支持OpenCL的異構(gòu)系統(tǒng)一般通過(guò)PCle總線實(shí)現(xiàn)主機(jī)與硬件加速器(或者一個(gè)內(nèi)核與另一個(gè)沒(méi)有主機(jī)控制的內(nèi)核)之間的通信�����,而這一切并不需要程序開發(fā)者的關(guān)注����。相反,開發(fā)者只需了解OpenCL定義的標(biāo)準(zhǔn)化的應(yīng)用程序接口(API)����。如今,各個(gè)主流的深度學(xué)習(xí)框架都提供OpenCL的支持����。英特爾正計(jì)劃推出基于FPGA的CNN的多種網(wǎng)絡(luò)實(shí)現(xiàn)。

OpenCL的編程模型

三�����、基于CPU+FPGA的異構(gòu)計(jì)算平臺(tái)

我們機(jī)器人系統(tǒng)實(shí)驗(yàn)室今年的工作重點(diǎn)便是為機(jī)器人搭建基于CPU+FPGA的異構(gòu)計(jì)算平臺(tái)���。根據(jù)我們的經(jīng)驗(yàn)����,F(xiàn)PGA能夠在一些關(guān)鍵的機(jī)器人應(yīng)用中發(fā)揮極大的價(jià)值�。例如�����,我們將機(jī)器人自身定位的算法(SLAM)移植到FPGA中執(zhí)行��,實(shí)現(xiàn)了比CPU高出十多倍的定位頻率,從而允許機(jī)器人以雙倍的速度運(yùn)動(dòng)�,而不會(huì)“迷失方向”。

為了打造通用的機(jī)器人計(jì)算平臺(tái)�����,我們選用了英特爾提供給移動(dòng)平臺(tái)使用的CPU和Arria 10系列的FPGA���。 兩者通過(guò)高帶寬��,低延遲的I/O接口(如PCIe)進(jìn)行通信���。 FPGA中可以包含多種加速模塊。我們會(huì)提供一套通用接口�����,便于模塊開發(fā)者包裝����、發(fā)布已有的設(shè)計(jì)�����。

機(jī)器人的異構(gòu)計(jì)算平臺(tái)

在軟件層面�,我們會(huì)構(gòu)建加速模塊的配置��、安裝和消息傳遞機(jī)制�����,便于第三方將所需的加速模塊集成到應(yīng)用中���,并設(shè)計(jì)一些定位��、控制����、視覺(jué)識(shí)別和物體建模的常用模塊��,以及軟件的集成包��,供用戶作為參考設(shè)計(jì)或直接選用。

有了如此智慧的大腦�����,機(jī)器人將變得更加耳聰�����,眼明��,腿快����,手穩(wěn)�����,融入我們的日常生活����,為人類提供更好的服務(wù)。