【導讀】芯片封裝早已不再僅限于傳統(tǒng)意義上為獨立芯片提供保護和I/O擴展接口,如今有越來越多的封裝技術(shù)能夠?qū)崿F(xiàn)多種不同芯片之間的互聯(lián)。先進封裝工藝能提高器件密度并由此減小空間占用,這一點對于手機和自動駕駛汽車等電子設(shè)備的功能疊加來說至關(guān)重要。芯片封裝行業(yè)的發(fā)展使國際電氣電子工程師協(xié)會電子元件封裝和生產(chǎn)技術(shù)學會(IEEE-CPMT)意識到必須要拓展自身的技術(shù)范疇,并于2017年正式更名為國際電氣電子工程師協(xié)會電子封裝學會(IEEE- EPS)。

芯片封裝早已不再僅限于傳統(tǒng)意義上為獨立芯片提供保護和I/O擴展接口,如今有越來越多的封裝技術(shù)能夠?qū)崿F(xiàn)多種不同芯片之間的互聯(lián)。先進封裝工藝能提高器件密度并由此減小空間占用,這一點對于手機和自動駕駛汽車等電子設(shè)備的功能疊加來說至關(guān)重要。芯片封裝行業(yè)的發(fā)展使國際電氣電子工程師協(xié)會電子元件封裝和生產(chǎn)技術(shù)學會(IEEE-CPMT)意識到必須要拓展自身的技術(shù)范疇,并于2017年正式更名為國際電氣電子工程師協(xié)會電子封裝學會(IEEE- EPS)。

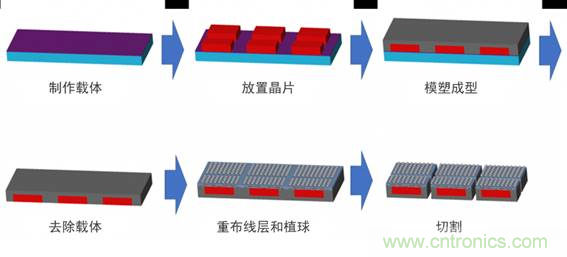

有一種先進封裝技術(shù)被稱為“晶圓級封裝”(WLP),即直接在晶圓上完成集成電路的封裝程序。通過該工藝進行封裝,可以制成與原裸片大小近乎相同的晶圓。早在2000年代末,英飛凌開發(fā)的嵌入式晶圓級球柵陣列(eWLB)就是一種晶圓級封裝技術(shù)。目前有許多封測代工廠(OSAT)都在使用eWLB的變種工藝。具體來說,eWLB封裝是指將檢驗合格的晶片正面朝下,放置在載體晶圓上并將兩者作為整體嵌入環(huán)氧樹脂模具。在模鑄重構(gòu)晶片結(jié)構(gòu)之后進行“扇出型”封裝,在暴露的晶圓表面進行重布線層工藝(RDLs)并植球,之后再將其切割成小塊即可獲得可供使用的芯片(圖1)。

圖1:eWLB封裝流程

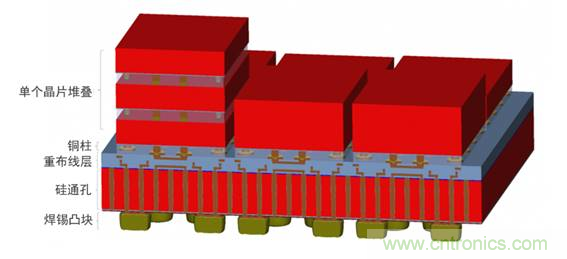

圖2展示的是其他結(jié)合晶圓級封裝的綜合性先進封裝技術(shù)。

硅通孔技術(shù)(TSV)是指完全穿透硅基底的垂直互連。圖2展示的是基于硅中介層的硅通孔技術(shù),即通過硅中介層實現(xiàn)高密度晶片與封裝層之間的電氣連接。該技術(shù)起初作為打線接合的替代方法而備受推廣,能夠在減小互聯(lián)長度來優(yōu)化電阻的同時,通過多個晶片堆疊實現(xiàn)3D集成。

圖2:器件封裝示意圖

作為導電互聯(lián)技術(shù)的應(yīng)用,重布線層的作用是重新分布連接至晶片焊盤I/O點位的電子線路,并且可以放置在單個晶片的一側(cè)或兩側(cè)。隨著對帶寬和I/O點位需求的提升,重布線層的線寬和間距也需要不斷縮小。為了滿足這些要求,目前工藝上已采用類似后段制程的銅鑲嵌技術(shù)來減小線寬,并通過銅柱代替?zhèn)鹘y(tǒng)焊接凸點的方法來減小晶片間連接的間距。

先進封裝技術(shù)還在持續(xù)發(fā)展,以滿足不斷提升的器件密度和I/O連接性能要求。近幾年出現(xiàn)的銅混合鍵合技術(shù)就是很好的例子,它的作用是直接將一個表面的銅凸點和電介質(zhì)連接至另一個主動表面的相應(yīng)區(qū)域,由此規(guī)避對凸點間距的限制。我們非常期待這些封裝技術(shù)上的創(chuàng)新能夠引領(lǐng)新一代電子產(chǎn)品的穩(wěn)步發(fā)展。

(作者:泛林集團)

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請電話或者郵箱聯(lián)系小編進行侵刪。