【導讀】 越來越多的數(shù)據(jù)中心和其他高性能計算環(huán)境開始使用GPU,因為GPU能夠快速處理深度學習和機器學習應(yīng)用中生成的大量數(shù)據(jù)。不過,就像許多可提高應(yīng)用性能的新型數(shù)據(jù)中心創(chuàng)新一樣,這項創(chuàng)新也暴露出新的系統(tǒng)瓶頸。

越來越多的數(shù)據(jù)中心和其他高性能計算環(huán)境開始使用GPU,因為GPU能夠快速處理深度學習和機器學習應(yīng)用中生成的大量數(shù)據(jù)。不過,就像許多可提高應(yīng)用性能的新型數(shù)據(jù)中心創(chuàng)新一樣,這項創(chuàng)新也暴露出新的系統(tǒng)瓶頸。在這些應(yīng)用中,用于提高系統(tǒng)性能的新興架構(gòu)涉及通過一個PCIe®結(jié)構(gòu)在多個主機之間共享系統(tǒng)資源。

PCIe標準(特別是其基于樹的傳統(tǒng)層級)會限制資源共享的實現(xiàn)方式(和實現(xiàn)程度)。不過,可以實現(xiàn)一種低延時的高速結(jié)構(gòu)方法,這種方法允許在多個主機之間共享大量GPU和NVMe SSD,同時仍支持標準系統(tǒng)驅(qū)動程序。

PCIe結(jié)構(gòu)方法采用動態(tài)分區(qū)和多主機單根I/O虛擬化(SR-IOV)共享。各PCIe結(jié)構(gòu)之間可直接路由點對點傳輸。這樣便可為點對點傳輸提供最佳路由,減少根端口擁塞,并且更有效地平衡CPU資源的負載。

傳統(tǒng)上,GPU傳輸必須訪問CPU的系統(tǒng)存儲器,這會導致端點之間發(fā)生存儲器共享爭用。 當GPU使用其共享的存儲器映射資源而不是CPU存儲器時,它可以在本地提取數(shù)據(jù),無需先通過CPU傳遞數(shù)據(jù)。這消除了跳線和鏈路以及由此產(chǎn)生的延時,從而使GPU能夠更高效地處理數(shù)據(jù)。

PCIe的固有限制

PCIe主層級是一個樹形結(jié)構(gòu),其中的每個域都有一個根聯(lián)合體,從該點可擴展到“葉子”,這些“葉子”通過交換網(wǎng)和橋接器到達端點。鏈路的嚴格層級和方向性給多主機、多交換網(wǎng)系統(tǒng)帶來了成本高昂的設(shè)計要求。

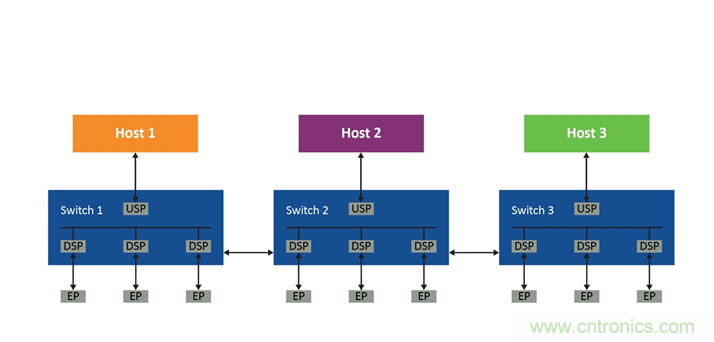

圖1——多主機拓撲

以圖1所示的系統(tǒng)為例。要符合PCIe的層級,主機1必須在交換網(wǎng)1中有一個專用的下行端口,該端口連接到交換網(wǎng)2中的專用上行端口。它還需要在交換網(wǎng)2中有一個專用的下行端口,該端口連接到交換網(wǎng)3中的專用上行端口,依此類推。主機2和主機3也有類似的要求,如圖2所示。

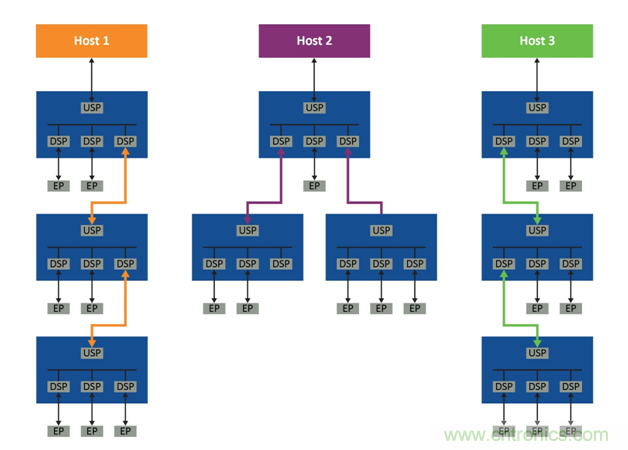

圖2——每個主機的層級要求

即使是基于PCIe樹形結(jié)構(gòu)的最基本系統(tǒng),也需要各交換網(wǎng)之間有三個鏈路專用于每個主機的PCIe拓撲。而且,由于主機之間無法共享這些鏈路,因此系統(tǒng)會很快變得極為低效。

此外,符合PCIe的典型層級只有一個根端口,而且盡管“多根I/O虛擬化和共享”規(guī)范中支持多個根,但它會使設(shè)計更復(fù)雜,并且當前不受主流CPU支持。結(jié)果會造成未使用的PCIe設(shè)備(即端點)滯留在其分配到的主機中。不難想象,這在采用多個GPU、存儲設(shè)備及其控制器以及交換網(wǎng)的大型系統(tǒng)中會變得多么低效。

例如,如果第一個主機(主機1)已經(jīng)消耗了所有計算資源,而主機2和3未充分利用資源,則顯然希望主機1訪問這些資源。但主機1無法這樣做,因為這些資源在它的層級域之外,因此會發(fā)生滯留。非透明橋接(NTB)是這種問題的一個潛在解決方案,但由于每種類型的共享PCIe設(shè)備都需要非標準驅(qū)動程序和軟件,因此這同樣會使系統(tǒng)變得復(fù)雜。更好的方法是使用PCIe結(jié)構(gòu),這種結(jié)構(gòu)允許標準PCIe拓撲容納多個可訪問每個端點的主機。

實施方法

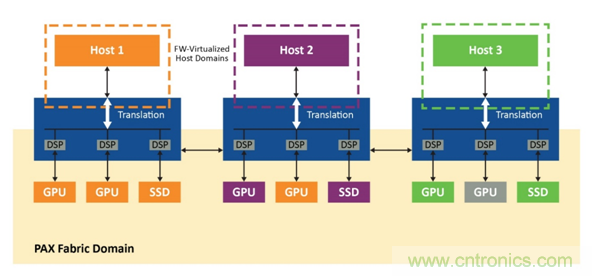

系統(tǒng)使用一個PCIe結(jié)構(gòu)交換網(wǎng)(本例中為Microchip Switchtec® PAX系列的成員)在兩個獨立但可透明互操作的域中實現(xiàn):即包含所有端點和結(jié)構(gòu)鏈路的結(jié)構(gòu)域以及每個主機專用的主機域(圖3)。主機通過在嵌入式CPU上運行的PAX交換網(wǎng)固件保留在單獨的虛擬域中,因此,交換網(wǎng)將始終顯示為具有直連端點的標準單層PCIe設(shè)備,而與這些端點出現(xiàn)在結(jié)構(gòu)中的位置無關(guān)。

圖3——每個結(jié)構(gòu)的獨立域

來自主機域的事務(wù)會在結(jié)構(gòu)域中轉(zhuǎn)換為ID和地址,反之,結(jié)構(gòu)域中通信的非分層路由也是如此。這樣,系統(tǒng)中的所有主機便可共享連接交換網(wǎng)和端點的結(jié)構(gòu)鏈路。交換網(wǎng)固件會攔截來自主機的所有配置平面通信(包括PCIe枚舉過程),并使用數(shù)量可配置的下行端口虛擬化一個符合PCIe規(guī)范的簡單交換網(wǎng)。

當所有控制平面通信都路由到交換網(wǎng)固件進行處理時,數(shù)據(jù)平面通信直接路由到端點。其他主機域中未使用的GPU不再滯留,因為它們可以根據(jù)每個主機的需求動態(tài)分配。結(jié)構(gòu)內(nèi)支持點對點通信,這使其能夠適應(yīng)機器學習應(yīng)用。當以符合PCIe規(guī)范的方式向每個主機提供功能時,可以使用標準驅(qū)動程序。

操作方法

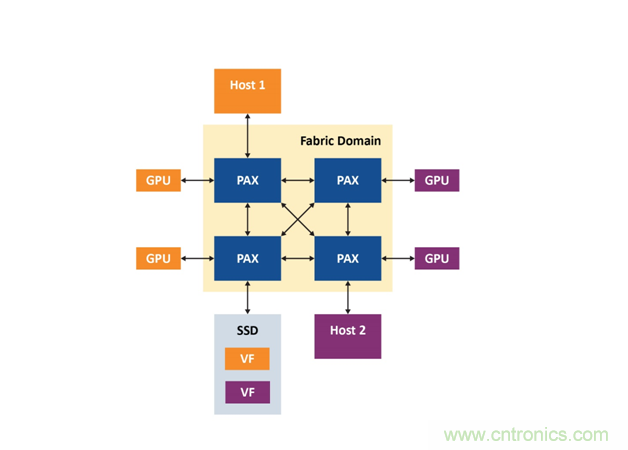

為了解這種方法的工作原理,我們以圖4中的系統(tǒng)為例,該系統(tǒng)由兩個主機(主機1采用Windows®系統(tǒng),主機2采用Linux®系統(tǒng))、四個PAX PCIe結(jié)構(gòu)交換網(wǎng)、四個Nvidia M40 GPGPU和一個支持SR-IOV的Samsung NVMe SSD組成。在本實驗中,主機運行代表實際機器學習工作負載的通信,包括Nvidia的CUDA點對點通信基準測試實用程序和訓練cifar10圖像分類的TensorFlow模型。嵌入式交換網(wǎng)固件處理交換網(wǎng)的低級配置和管理,系統(tǒng)由Microchip的ChipLink調(diào)試和診斷實用程序管理。

圖4:雙主機PCIe結(jié)構(gòu)引擎

四個GPU最初分配給主機1,PAX結(jié)構(gòu)管理器顯示在結(jié)構(gòu)中發(fā)現(xiàn)的所有設(shè)備,其中GPU綁定到Windows主機。但是,主機上的結(jié)構(gòu)不再復(fù)雜,所有GPU就像直接連接到虛擬交換網(wǎng)一樣。隨后,結(jié)構(gòu)管理器將綁定所有設(shè)備,Windows設(shè)備管理器將顯示GPU。主機將交換網(wǎng)視為下行端口數(shù)量可配置的簡單物理PCIe交換網(wǎng)。

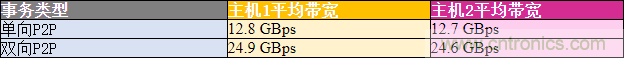

一旦CUDA發(fā)現(xiàn)了四個GPU,點對點帶寬測試就會顯示單向傳輸速率為12.8 GBps,雙向傳輸速率為24.9 GBps。這些傳輸直接跨過PCIe結(jié)構(gòu),而無需通過主機。如果運行用于訓練Cifar10圖像分類算法的TensorFlow模型并使工作負載分布在全部四個GPU上,則可以將兩個GPU釋放回結(jié)構(gòu)池中,將它們與主機解除綁定。這樣可以釋放其余兩個GPU來執(zhí)行其他工作負載。與Windows主機一樣,Linux主機也將交換網(wǎng)視為簡單的PCIe交換網(wǎng),無需自定義驅(qū)動程序,而CUDA也可以發(fā)現(xiàn)GPU,并在Linux主機上運行P2P傳輸。性能類似于使用Windows主機實現(xiàn)的性能,如表1所示。

表1:GPU點對點傳輸帶寬

下一步是將SR-IOV虛擬功能連接到Windows主機,PAX將此類功能以標準物理NVM設(shè)備的形式提供,以便主機可以使用標準NVMe驅(qū)動程序。此后,虛擬功能將與Linux主機結(jié)合,并且新的NVMe設(shè)備將出現(xiàn)在模塊設(shè)備列表中。本實驗的結(jié)果是,兩個主機現(xiàn)在都可以獨立使用其虛擬功能。

務(wù)必注意的是,虛擬PCIe交換網(wǎng)和所有動態(tài)分配操作都以完全符合PCIe規(guī)范的方式呈現(xiàn)給主機,以便主機能夠使用標準驅(qū)動程序。嵌入式交換網(wǎng)固件提供了一個簡單的管理接口,這樣便可通過成本低廉的外部處理器來配置和管理PCIe結(jié)構(gòu)。設(shè)備點對點事務(wù)默認情況下處于使能狀態(tài),不需要外部結(jié)構(gòu)管理器進行額外配置或管理。

總結(jié)

PCIe交換網(wǎng)結(jié)構(gòu)是一種能夠充分利用CPU巨大性能的絕佳方法,但PCIe標準本身存在一些障礙。不過,可以通過使用動態(tài)分區(qū)和多主機單根I/O虛擬化共享技術(shù)來解決這些難題,以便可以將GPU和NVMe資源實時動態(tài)分配給多主機系統(tǒng)中的任何主機,從而滿足機器學習工作負載不斷變化的需求。

(來源:Microchip Technology Inc.,作者:固件工程技術(shù)顧問 Vincent Haché)

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請電話或者郵箱聯(lián)系小編進行侵刪。