【導(dǎo)讀】時(shí)序一直都是相對(duì)復(fù)雜的�����,而DDR2和DDR3時(shí)序設(shè)計(jì)時(shí)還有個(gè)叫derating的東西�,暈�!什么是derating呢����?簡(jiǎn)而言之就是對(duì)建立保持時(shí)間基準(zhǔn)值的修正��。

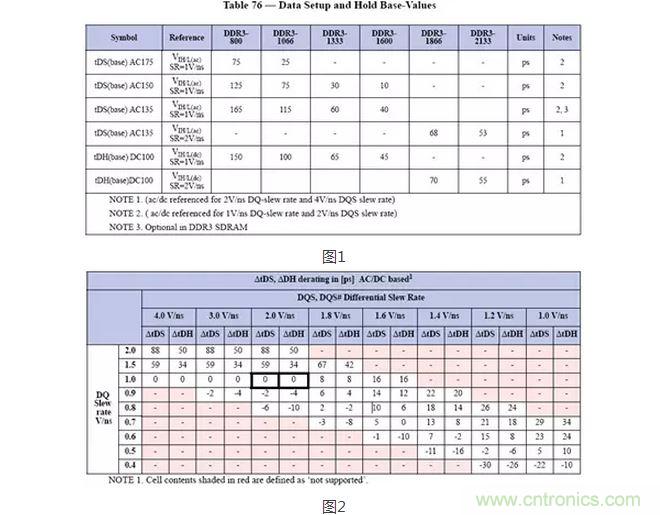

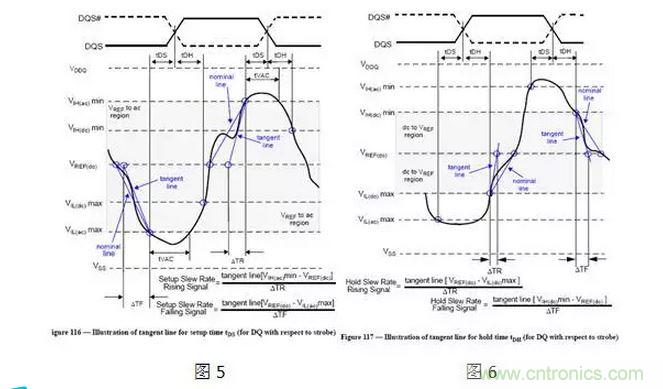

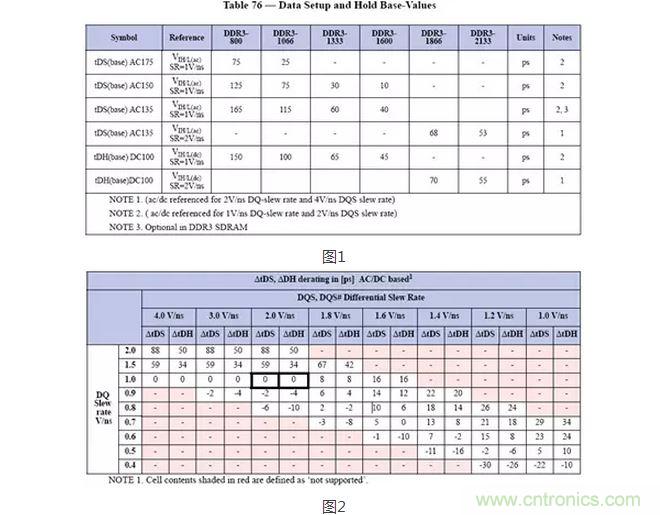

以DDR3信號(hào)為例�����,在JEDEC規(guī)范中規(guī)定了一個(gè)建立保持時(shí)間的基準(zhǔn)值(圖1)���,還有就是derating值(圖2)�,兩者之和就是所需的建立保持時(shí)間���。

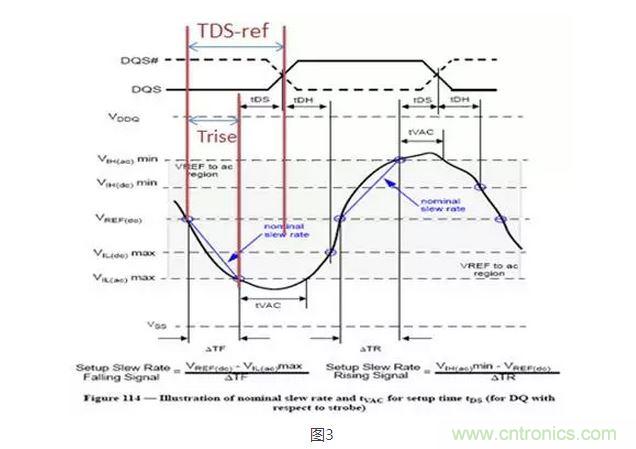

由圖2表格中可以看到derating的取值是與data,strobe的slew rate有關(guān)�����,還和判斷門限有關(guān)的����。這個(gè)怎么理解呢?

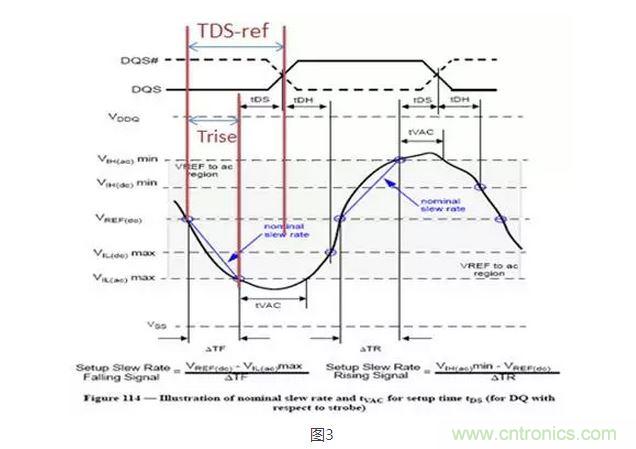

如圖3�,建立時(shí)間等于TDS-ref(在ref處的建立時(shí)間)減去Trise(Vref到VIH AC的時(shí)間)��。規(guī)范中的基準(zhǔn)值是預(yù)減去了這個(gè)Trise的����,這個(gè)預(yù)減去的值是特定slew rate為1V/ns時(shí)的值��,若判斷門限是AC175�����,則預(yù)減去175ps�。請(qǐng)?jiān)倏磮D2,當(dāng)slew rate等于1V/ns時(shí)�����,derating為0����,不需要調(diào)整;當(dāng)slew rate大于1V/ns(更快)時(shí)��,從Vref到Vih(ac)所需的時(shí)間就少�,預(yù)減多了,要補(bǔ)回來(lái)�����,所以取值為正;當(dāng)slew rate小于1V/ns(更慢)時(shí)就預(yù)減少了�,所以取值為負(fù)。從圖2中的取值關(guān)系推導(dǎo)出取值公式為Derating @AC175 = 175ps - 175mV/SR����,大家可以代入計(jì)算一下試試。如果判斷門限是AC150或其他都可以套用��。而保持時(shí)間是DC門限�,其公式為Derating @DC100 = 100ps - 100mV/SR。

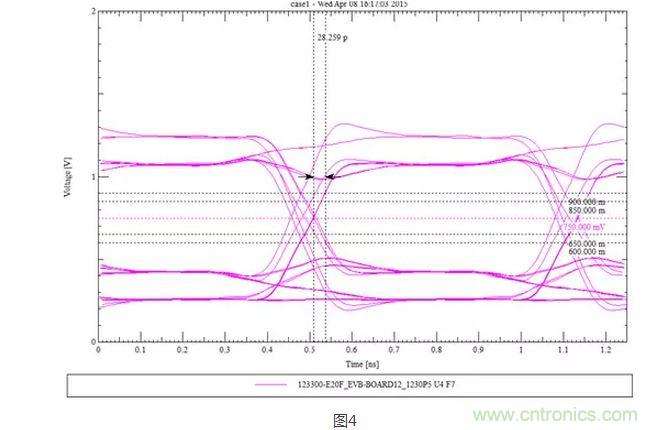

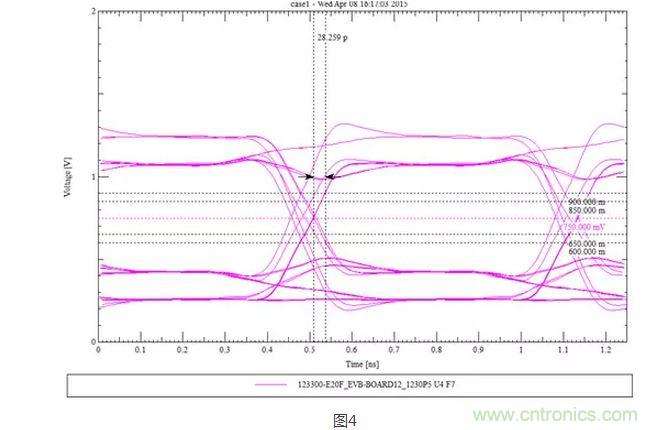

下圖是1600Mbps的DDR3信號(hào)�����,判斷門限AC150�����,跑出來(lái)的波形一量5V/ns����。JEDEC的derating表最大到2v/ns,咋辦���?

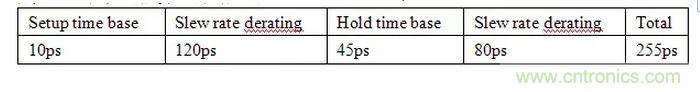

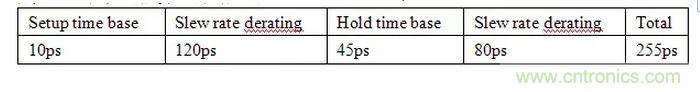

簡(jiǎn)單��,可以用上面的公式計(jì)算出derating值���,但上述公式只適用于>1v/ns的情況��。然后和基準(zhǔn)值相加得到總的建立保持時(shí)間�����,如下表����,總共所需的建立保持時(shí)間的總和是255ps�����。這樣就可以準(zhǔn)確的估算時(shí)序裕量了�。

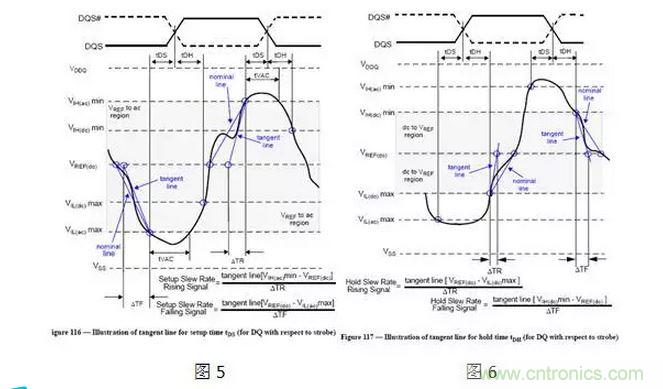

當(dāng)我們的上升沿,下降沿單調(diào)性差時(shí)�����,我們?cè)撊绾未_定slew rate呢?JEDEC規(guī)范中定義了normal slew rate和tangent slew rate����,如圖5,圖6�����。

問(wèn)題來(lái)了:到底是選normal slew rate還是tangent slew rate�,為什么?