【導讀】隨著電路設計高速高密的發(fā)展趨勢,QFN封裝已經有0.5mm pitch甚至更小pitch的應用。由小間距QFN封裝的器件引入的PCB走線扇出區(qū)域的串擾問題也隨著傳輸速率的升高而越來越突出。

隨著電路設計高速高密的發(fā)展趨勢,QFN封裝已經有0.5mm pitch甚至更小pitch的應用。由小間距QFN封裝的器件引入的PCB走線扇出區(qū)域的串擾問題也隨著傳輸速率的升高而越來越突出。對于8Gbps及以上的高速應用更應該注意避免此類問題,為高速數(shù)字傳輸鏈路提供更多裕量。本文針對PCB設計中由小間距QFN封裝引入串擾的抑制方法進行了仿真分析,為此類設計提供參考。

問題分析

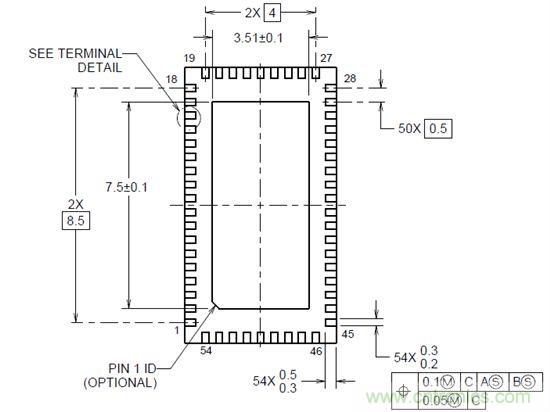

在PCB設計中,QFN封裝的器件通常使用微帶線從TOP或者BOTTOM層扇出。對于小間距的QFN封裝,需要在扇出區(qū)域注意微帶線之間的距離以及并行走線的長度。圖一是一個0.5 pitch QFN封裝的尺寸標注圖。

圖一:0.5 pitch QFN封裝尺寸標注圖

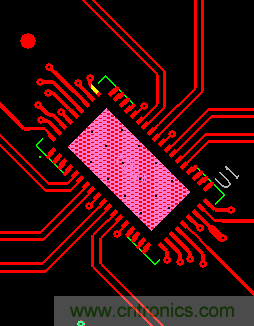

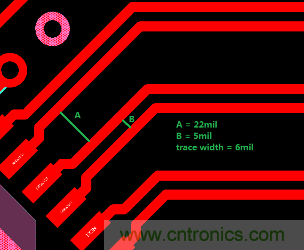

圖二是一個使用0.5mm pitch QFN封裝的典型的1.6mm 板厚的6層板PCB設計:

圖二:QFN封裝PCB設計TOP層走線

差分線走線線寬/線距為:8/10, 走線距離參考層7mil,板材為FR4.

圖三:PCB差分走線間距與疊層

從上述設計我們可以看出,在扇出區(qū)域差分對間間距和差分對內的線間距相當,會使差分 對間的串擾增大。

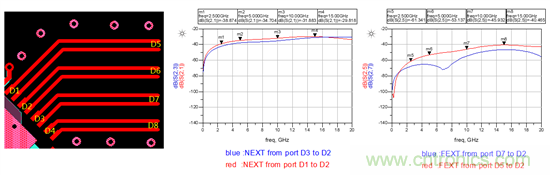

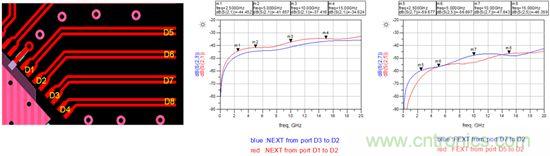

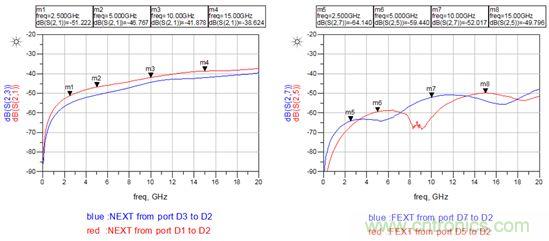

圖四是上述設計的差分模式的近端串擾和遠端串擾的仿真結果,圖中D1~D6是差分端口。

圖四:差分模式端口定義及串擾仿真結果

從仿真結果可以看出,即使在并行走線較短的情況下,差分端口D1對D2的近端串擾在5GHz超過了-40dB,在10GHz達到了-32dB,遠端串擾在15GHz達到了-40dB。對于10Gbps及以上的應用而言,需要對此處的串擾進行優(yōu)化,將串擾控制到-40dB以下。

優(yōu)化方案分析

對于PCB設計來說,比較直接的優(yōu)化方法是采用緊耦合的差分走線,增加差分對間的走線間距,并減小差分對之間的并行走線距離。

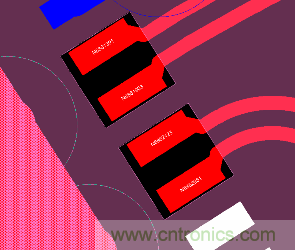

圖五是針對上述設計使用緊耦合差分線進行串擾優(yōu)化的一個實例:

圖五 緊耦合差分布線圖

圖六是上述設計的差分模式的近端串擾和遠端串擾的仿真結果:

圖六 緊耦合差分端口定義及串擾仿真結果

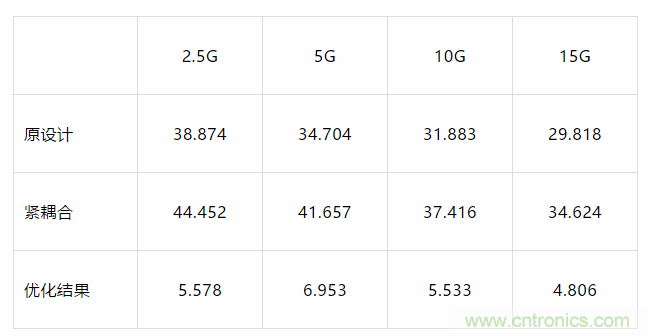

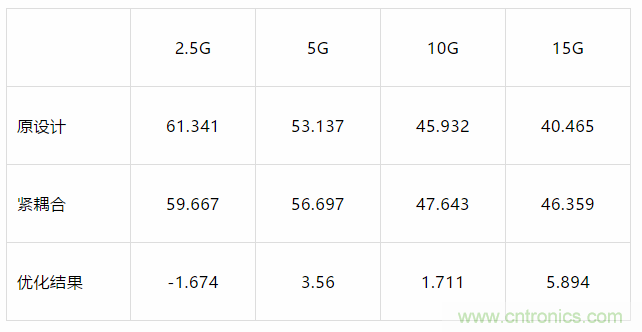

從優(yōu)化后的仿真結果可以看出,使用緊耦合并增加差分對之間的間距可以使差分對間的近端串擾在0~20G的頻率范圍內減小4.8~6.95dB。遠端串擾在5G~20G的頻率范圍內減小約1.7~5.9dB。

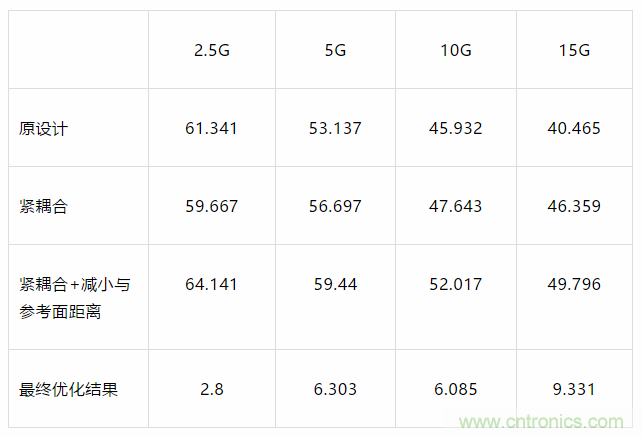

表一 近端串擾優(yōu)化統(tǒng)計

表二 遠端串擾優(yōu)化統(tǒng)計

除了在布線時拉開差分對之間的間距并減小并行距離之外,我們還可以調整差分線走線層和參考平面的距離來抑制串擾。距離參考層越近,越有利于抑制串擾。在采用緊耦合走線方式的基礎上,我們將TOP層與其參考層之間的距離由7mil調整到4mil。

圖七 疊層調整示意圖

根據(jù)上述優(yōu)化進行仿真,仿真結果如下圖:

圖八 疊層調整后串擾仿真結果

值得注意的是,當我們調整了走線與參考平面的距離之后,差分線的阻抗也隨之發(fā)生變化,需要調整差分走線滿足目標阻抗的要求。芯片的SMT焊盤距離參考平面距離變小之后阻抗也會變低,需要在SMT焊盤的參考平面上進行挖空處理來優(yōu)化SMT焊盤的阻抗。具體挖空的尺寸需要根據(jù)疊層情況進行仿真來確定。

圖九 疊層調整后QFN焊盤阻抗優(yōu)化示意圖

從仿真結果可以看出,調整走線與參考平面的距離后,使用緊耦合并增加差分對之間的間距可以使差分對間的近端串擾在0~20G的頻率范圍內減小8.8~12.3dB。遠端串擾在0~20G范圍內減小了2.8~9.3dB。

表三 近端串擾優(yōu)化統(tǒng)計

表四 遠端串擾優(yōu)化統(tǒng)計

結論

通過仿真優(yōu)化我們可以將由小間距QFN封裝在PCB上引起的近端差分串擾減小8~12dB,遠端串擾減小3~9dB,為高速數(shù)據(jù)傳輸通道提供更多裕量。本文涉及的串擾抑制方法可以在制定PCB布線規(guī)則和疊層時綜合考慮,在PCB設計初期避免由小間距QFN封裝帶來的串擾風險。

(來源:志博PCB,作者: 楊多多)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯(lián)系小編進行處理。