【導讀】隨著數模轉換器的轉換速率越來越高,JESD204B 串行接口已經越來越多地廣泛用在數模轉換器上,其對器件時鐘和同步時鐘之間的時序關系有著嚴格需求。本文就重點講解了JESD204B 數模轉換器的時鐘規(guī)范,以及利用TI 公司的芯片實現其時序要求。

1. JESD204B 介紹

1.1 JESD204B 規(guī)范及其優(yōu)勢

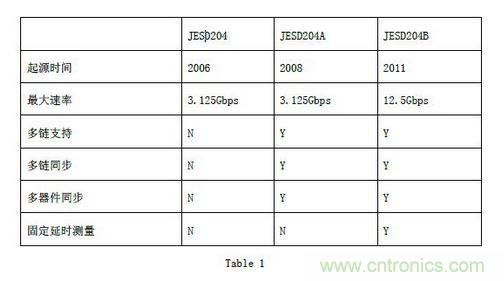

JESD204 是基于SerDes($174.9800) 的串行接口標準,主要用于數模轉換器和邏輯器件之間的數據傳輸,其最早的版本是JESD204A, 現在是JESD204Bsubclass0, subclass1, subclass2。區(qū)別主要在于其對同步和鏈路間固定時差的測量。目前市場上比較多地數模轉換器接口是JESD204B subclass1。其最大傳輸速率可達12.5Gbps,支持多鏈路和多器件的同步以及固定時差的測量。下表是各版本之間的差異:

在JESD204 接口出現以前,數模轉換器的數字接口絕大多數是差分LVDS 的接口,這就造成了布板的困難,當PCB 的密度很大的時候就需要增加板層從而造成印制板的成本上升。而JESD204B 接口是串行接口,能有效減少數據輸出的差分對,能最大限度的簡化Layout。因此JESD204B 是高密度板不可或缺的接口。但因其需要進行嚴格的同步和以及時延的測量,與之接口的邏輯會比LVDS 接口復雜很多,幸運的是現在邏輯廠商都集成了專用的JESD204IPCore 在他們的軟件里,從而簡化了邏輯的設計。

1.2 JESD204B 時鐘的需求

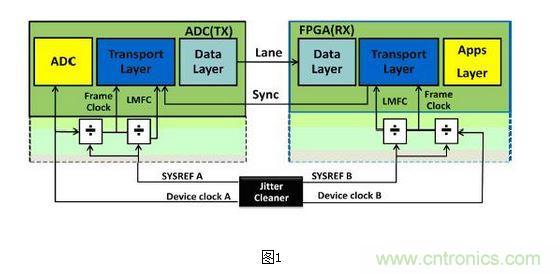

盡管JESD204B 也有不同的版本,但越來越多的廠商選擇Subclass1,因此市面上絕大多數的數模轉換器都是基于這個版本設計的。本文就以JESD204B subclass1 來討論時鐘的時序需要以及TI 時鐘芯片方案的實現。任何一個串行協議都離不開幀和同步,JESD204B 也不例外,也需要收發(fā)雙方有相同的幀結構,然后以一種方式來同步,即辨別起始。JESD204B是以時鐘信號的沿來辨別同步的開始,以及通過一定的握手信號使得收發(fā)雙方能夠正確識別幀的長度和邊界,因此時鐘信號及其時序關系對于JESD204B 就顯得極其重要。下圖是典型的JESD204B 系統的系統連接,Device Clock 是器件工作的主時鐘,一般在數模轉換器里為

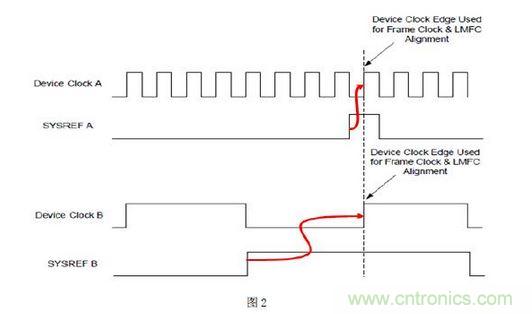

其采樣時鐘或者整數倍頻的時鐘,其協議本身的幀和多幀的時鐘也是基于Device Clock。SYSREF 是用于指示不同轉換器或者邏輯的Device Clock 的沿,或者不同器件間Deterministic latency 的參考。如下圖所示,Device Clock 和SYSREF 必須滿足的時序關系。

SYSREF 的第一個上升沿要非常容易的能被Device Clock 捕捉到,這樣就需要SYSREF和Device Clock 滿足上圖的時序關系。通常會因為PCB 的線長以及時鐘器件不同通道輸出時的Skew,會帶來一定的誤差,Device Clock 的上升沿不一定正好在SYSREF 的脈沖的正中間,工程上只要在一定范圍內就能保證JESD204 收發(fā)正常工作。

[page]

2.JESD204B 時鐘的實現

2.1 專用的JESD204B 時鐘芯片

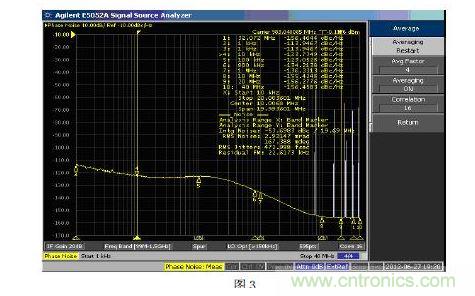

LMK04820 系列的時鐘芯片是一款專用的JESD204B 時鐘芯片,Device Clock 和SYSREF是成對輸出的,其輸出的時序滿足其時序要求,應用較為簡單,但當用戶需要連續(xù)模式的SYSREF 時,會引起一定串擾如下圖所示(983.04MDevclk and 7.68MSysREF),可能會造成數模轉換器的性能下降。當然SYSREF 工作在脈沖模式,LMK04820 是一個完美選擇。如果板上JESD204B 時鐘路數較多,LMK04820 的輸出不能滿足要求,可以用LMK1802 擴展得到更多的時鐘輸出。

2.2 通用的LVDS 時鐘芯片

在某些應用中客戶的系統上既有JESD204B 的數模轉換器,也有LVDS 接口的數模轉換器,或者客戶需要用到連續(xù)模式的SYSREF,這時LMK04800 系列的時鐘芯片是理想選擇。LMK04800 是帶有輸出延時調整的去抖芯片,我們調整其輸出的延時,使得兩路不同通道的輸出的時序滿足JESD204B 時序的要求,分別作為Device Clock 和 SYSREF。因此延時調整是LVDS 時鐘芯片實現JESD204B 時鐘的核心。

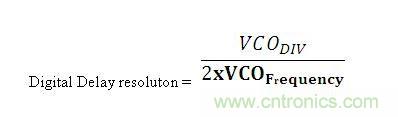

LMK04800 的輸出有數字延時和模擬延時,在多數應用時數字延時的調整精度已經能滿足了,因此不推薦模擬延時調整,另外模擬延時會帶來輸出時鐘噪底的惡化,一般會惡化3-5db。數字延時的精度取決于第二級集成VCO。

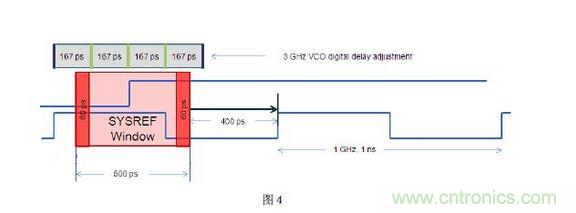

如果VCO_DIV 沒有用或者用外部的VCO,則分子必須等于1 。當延時設置完成后,必須有同步事件才能使得設置生效,同步可以通過寄存器,硬件管腳去觸發(fā)。當明白了數字延時的調整精度,再結合PCB 傳輸延時就可以計算出最大的調整誤差。如果Device Clock 是1GHz,而此時VCO 的頻率是3GHz,則根據上面公式調整精度是167ps,另外我們需要考慮到器件不同輸出通道的Skew,這里假設±30ps, 另外還需要考慮到SYSREF和Device Clock 的PCB 長度不等長,這里假設0.5cm,約±30ps,則我們可以得到SYSREF 可調整的窗口:

圖中400ps 是LMK04800 LVDS 的輸出的上升沿和下降沿所用時間(上升沿和下降沿都是200ps)。 圖中我們可以根據以上的條件計算得到調整精度是167ps, Device Clock 的周期是1000ps,則可調整的窗口為1000-400-120=480ps,即為紅色的的影映區(qū)域,當SYSREF 的上升沿在紅色的區(qū)域調整時,Device clock 可以容易的檢測到SYSREF 的上升沿,否則需要等到下一個Device clock 周期才能檢測到SYSREF 上升沿。

[page]

3 結論及其測試驗證

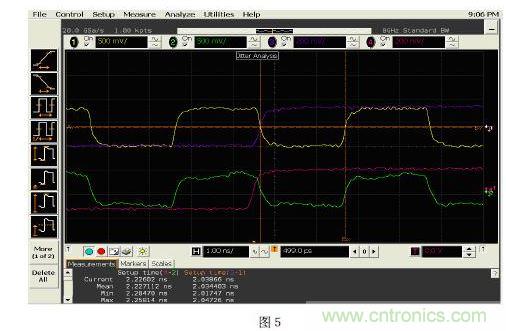

相比LMK04828($12.6000),我們用LMK04800 和LMK01010($7.7512) 產生JESD204B 的時鐘,既能滿足全是JESD204B 的器件的要求,也能很好的用在有LVDS 接口需要的系統中。另外LMK04800是一款非常成熟的具有高延時精度的時鐘芯片,其性能被用戶廣泛接受,同時在某些需要用延時調整去適應DPD 算法的應用中也能很好提供完美時鐘解決方案。如下圖所示,這是通過調整LMK04800 的輸出延時,用示波器采集的JESD204B 的時鐘,其時序能很好的滿足其標準。