【導(dǎo)讀】精密模數(shù)轉(zhuǎn)換器應(yīng)用廣泛�,如儀器儀表和測(cè)量����、電力線(xiàn)繼電保 護(hù)�、過(guò)程控制���、電機(jī)控制等�。目前��,SAR 型ADC的分辨率可達(dá)18 位甚至更高���,采樣速率為數(shù)MSPS;Σ-Δ 型ADC 的分辨率則達(dá)到24位甚至32位�����,采樣速率為數(shù)百kSPS�����。為了充分利用高性能ADC而不限制其能力�����,用戶(hù)在降低信號(hào)鏈噪聲方面(例如實(shí)現(xiàn)濾波器)面臨的困難越來(lái)越多����。

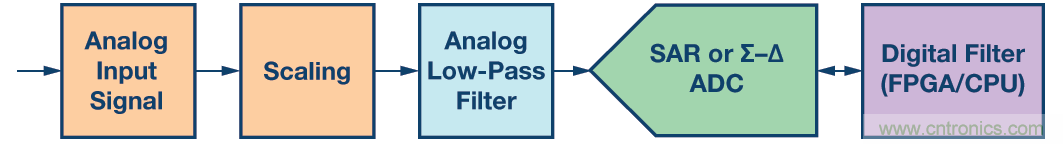

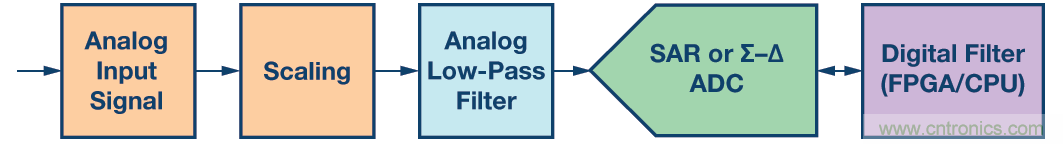

本文討論在ADC信號(hào)鏈中實(shí)現(xiàn)模擬和數(shù)字濾波器以便達(dá)到最佳性能所涉及到的設(shè)計(jì)挑戰(zhàn)和考慮。如圖1 所示�����,數(shù)據(jù)采集信號(hào)鏈可以使用模擬或數(shù)字濾波技術(shù),或兩者的結(jié)合���。精密SAR型和Σ-Δ型ADC一般在第一奈奎斯特區(qū)進(jìn)行采樣�,因此�,本文將著重討論低通濾波器。本文的意圖不是討論低通濾波器的具體設(shè)計(jì)技術(shù)�,而是討論其在ADC電路中的應(yīng)用。

圖1.一般數(shù)據(jù)采集信號(hào)鏈

理想濾波器和實(shí)際濾波器

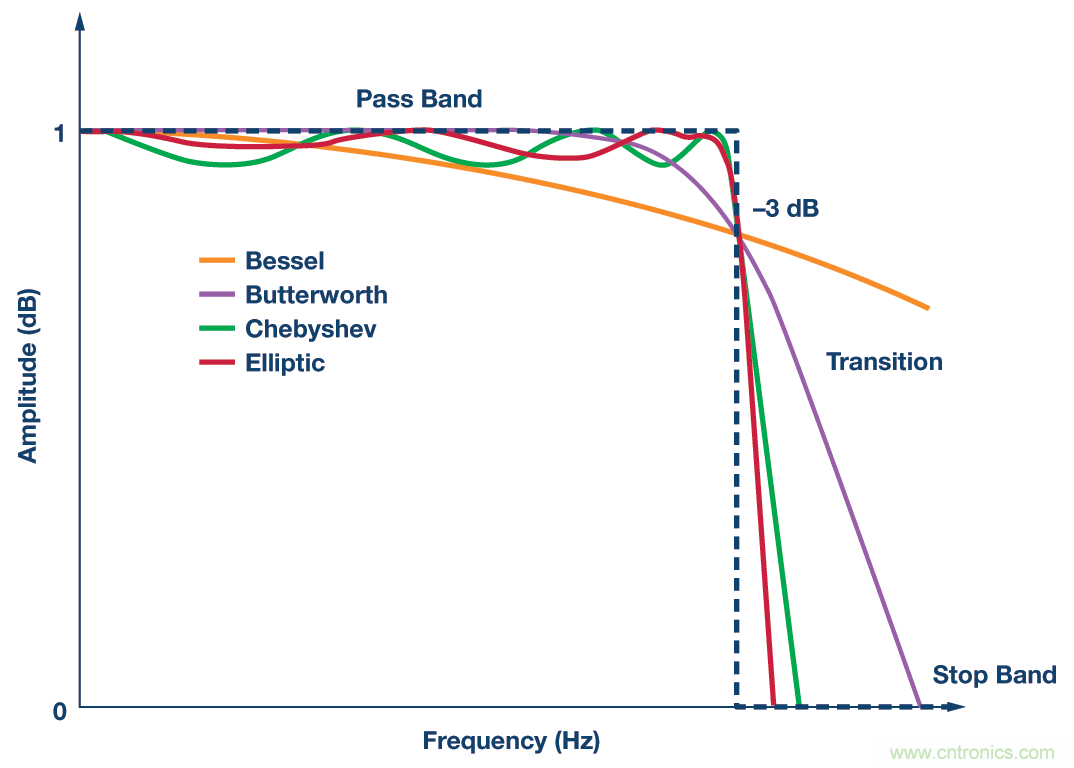

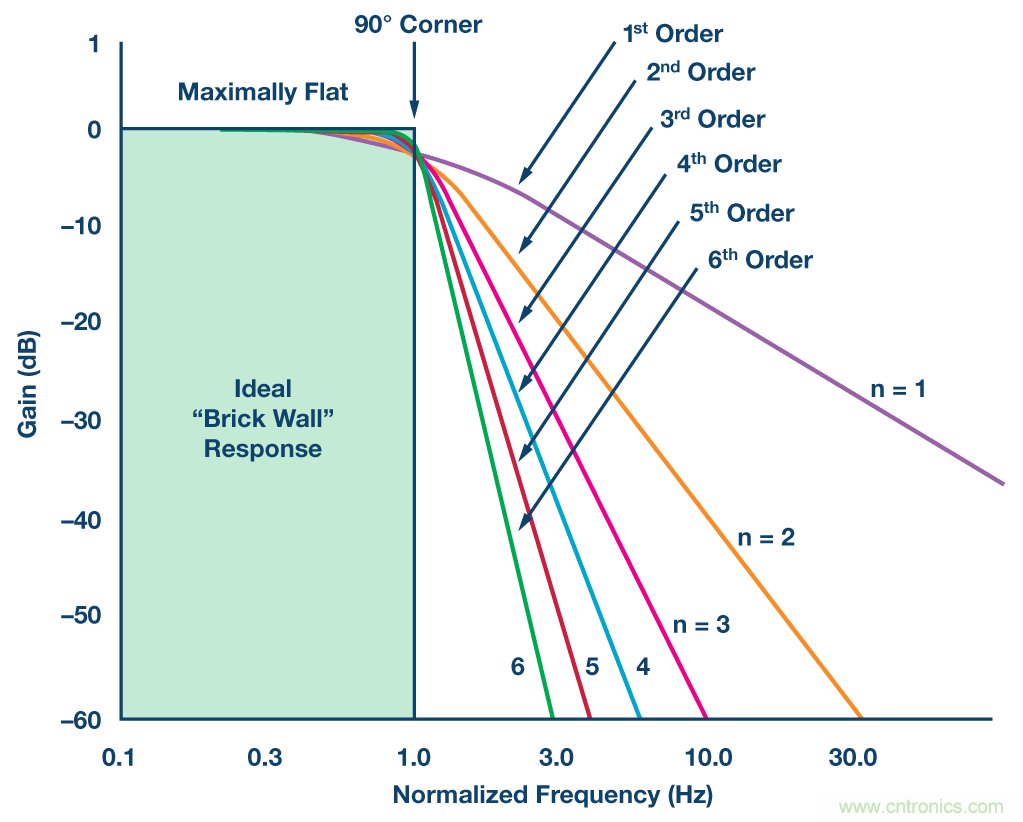

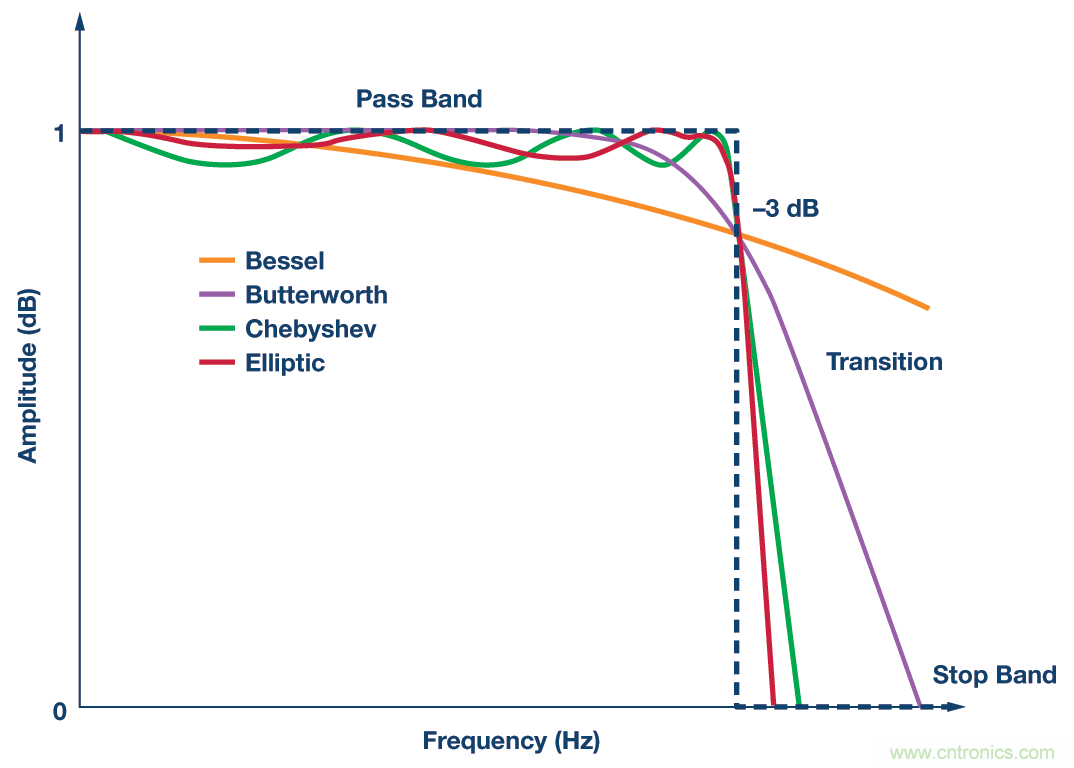

理想低通濾波器應(yīng)當(dāng)具有很陡的過(guò)渡帶���,其通帶應(yīng)具有出色的 增益平坦度���,如圖2 中的磚墻虛線(xiàn)所示。此外����,阻帶衰減應(yīng)將 任何殘余帶外信號(hào)降低至0。某些常用實(shí)際濾波器的響應(yīng)如圖2 中的彩色線(xiàn)條所示��。如果通帶增益不平坦或有紋波����,這種響應(yīng) 可能會(huì)影響基頻信號(hào)。阻帶衰減不是無(wú)限的,會(huì)限制對(duì)帶外噪 聲的篩選�。過(guò)渡帶也可能沒(méi)有陡峭的滾降,導(dǎo)致對(duì)截止頻率周 圍的噪聲衰減不佳��。另外����,所有非理想濾波器都會(huì)引入相位延 遲或群延遲。

圖2.理想濾波器與實(shí)際濾波器的幅度響應(yīng)對(duì)比

模擬濾波器與數(shù)字濾波器

模擬低通濾波器可以在ADC 轉(zhuǎn)換之前消除信號(hào)路徑中的高頻 噪聲和干擾���,幫助避免混疊噪聲污染信號(hào)。它還能消除濾波器 帶寬之外的過(guò)驅(qū)信號(hào)的影響���,避免調(diào)制器飽和��。發(fā)生輸入過(guò)壓 時(shí)����,模擬濾波器還能限制輸入電流���,衰減輸入電壓���。因此,它 能保護(hù)ADC 輸入電路。疊加于接近滿(mǎn)量程信號(hào)上的噪聲尖峰 可能會(huì)讓ADC 的模擬調(diào)制器飽和�����,必須利用模擬濾波器將其 衰減��。

由于數(shù)字濾波發(fā)生在轉(zhuǎn)換之后����,因而可以移除轉(zhuǎn)換過(guò)程中注入 的噪聲。在實(shí)際應(yīng)用中�,采樣速率遠(yuǎn)高于奈奎斯特理論指出的 兩倍基頻信號(hào)頻率。因此��,后置數(shù)字濾波器可以利用針對(duì)更高 信噪比和更高分辨率的濾波技術(shù)來(lái)降低轉(zhuǎn)換過(guò)程中注入的噪 聲��,例如:信號(hào)帶寬之外的輸入噪聲����、電源噪聲、基準(zhǔn)源噪聲�����、 數(shù)字接口饋通噪聲���、ADC 芯片熱噪聲或量化噪聲�。

表1簡(jiǎn)要列出了模擬濾波器與數(shù)字濾波器的優(yōu)點(diǎn)和缺點(diǎn)。

表1.模擬濾波器與數(shù)字濾波器

模擬濾波器考慮

抗混疊濾波器放在ADC 之前�,因此這些濾波器必須為模擬濾 波器。理想抗混疊濾波器具有如下特性:通帶內(nèi)具有單位增益�, 無(wú)增益變化,混疊衰減水平與所用數(shù)據(jù)轉(zhuǎn)換系統(tǒng)的理論動(dòng)態(tài)范 圍一致���。

根據(jù)架構(gòu)不同�����,ADC 會(huì)有不同的輸入電阻��,這會(huì)影響輸入濾 波器設(shè)計(jì)���。以下考慮關(guān)系到ADC 模擬輸入濾波器的設(shè)計(jì)���。

與ADC 前端接口的RC 抗混疊濾波器的限制

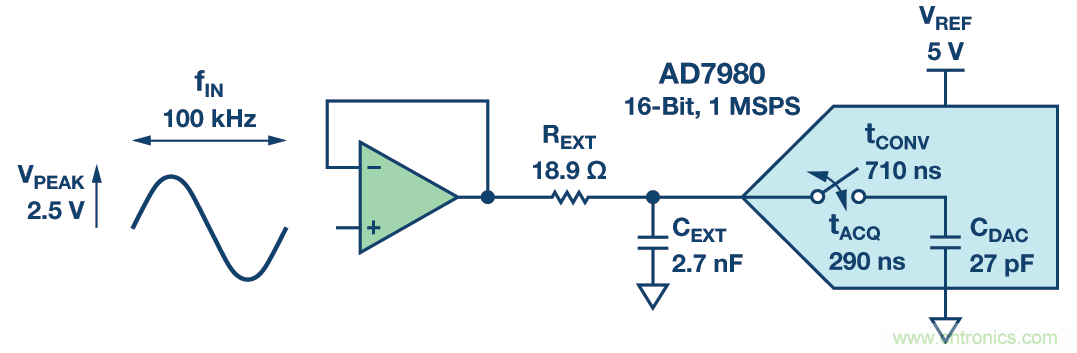

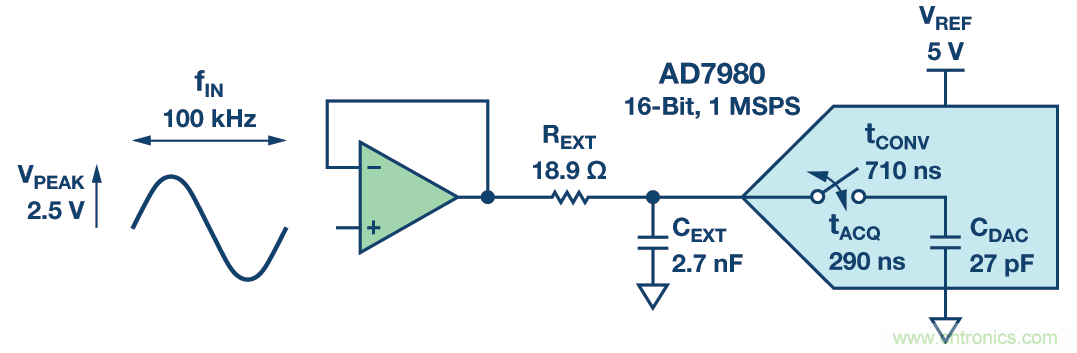

在Alan Walsh 為Analog Dialogue 雜志撰寫(xiě)的文章"精密SAR 型模數(shù)轉(zhuǎn)換器的前端和放大器和RC 濾波器設(shè)計(jì)" 中��,有一個(gè)針對(duì)AD7980ADC 的RC 濾波器應(yīng)用示例�����,如圖3 所示��。

算出的RC 濾波器是一個(gè)低通濾波器�,截止帶寬為3.11 MHz。 但是��,某些設(shè)計(jì)人員可能會(huì)意識(shí)到���,3.11 MHz 遠(yuǎn)大于100 kHz 的輸入信號(hào)頻率���,因此,該濾波器無(wú)法有效降低帶外噪聲���。為 實(shí)現(xiàn)更高動(dòng)態(tài)范圍�����,可以換用590 Ω 電阻��,以獲得100 kHz 的 –3 dB 帶寬��。這種方法主要有兩個(gè)問(wèn)題�。由于通帶中會(huì)有更多 衰減�,對(duì)于AD7980 ADC 示例�,100 kHz 附近的幅度衰減最高 可達(dá)30%��,因此��,信號(hào)鏈精度會(huì)大大降低�。帶寬越小,則建立 時(shí)間越長(zhǎng)�,這使得AD7980 的內(nèi)部采樣保持電容無(wú)法在指定的 采集時(shí)間內(nèi)完成充電,因而無(wú)法執(zhí)行下一次有效轉(zhuǎn)換����。這導(dǎo)致 ADC 轉(zhuǎn)換精度降低。

設(shè)計(jì)人員應(yīng)當(dāng)確保ADC 之前的RC 濾波器能在目標(biāo)采集時(shí)間內(nèi) 完全建立���。這對(duì)需要較大輸入電流或具有等效的較小輸入阻抗 的精密ADC 來(lái)說(shuō)異常重要���。某些Σ-Δ 型ADC 在無(wú)緩沖輸入模 式下對(duì)輸入RC 值的要求最高?��?梢詫⒕哂休^大電阻或電容的超 窄低通濾波器放在一般具有較大輸入阻抗的輸入放大器之前。 或者可以選擇具有極高輸入阻抗的ADC�,例如ADAS3022其 輸入阻抗為500 MΩ。

圖3.采用16 位1 MSPS ADC AD7980 的RC 濾波器

1. 多路復(fù)用采樣信號(hào)鏈的濾波器建立時(shí)間

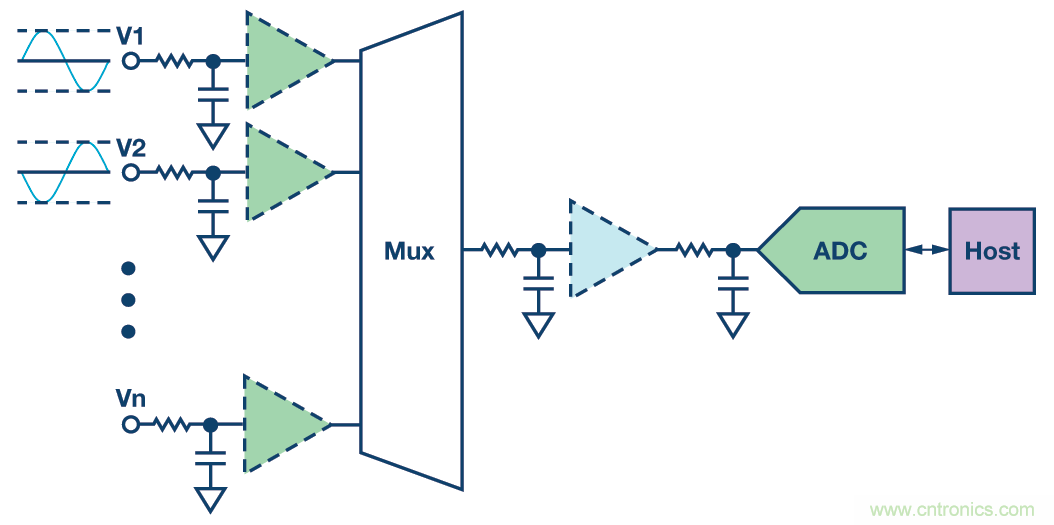

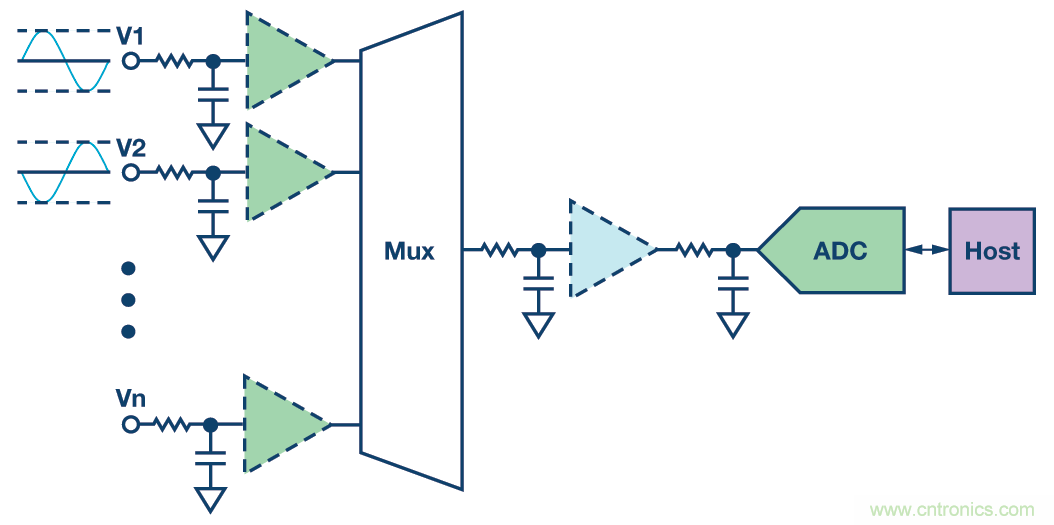

在通道間切換時(shí)��,多路復(fù)用輸入信號(hào)通常含有較大的階躍。最 差情況下����,一個(gè)通道處于負(fù)滿(mǎn)量程,而下一個(gè)通道則處于正滿(mǎn) 量程(見(jiàn)圖4)����。這種情況下,當(dāng)多路復(fù)用器切換通道時(shí)���,輸入 階躍大小將是ADC 的滿(mǎn)量程�。

對(duì)于這些通道�����,可以在多路復(fù)用器之后使用一個(gè)單通道濾波 器�,使得設(shè)計(jì)更簡(jiǎn)單,成本更低����。如上所述,模擬濾波器必定 會(huì)引入建立時(shí)間���。每次多路復(fù)用器在通道間切換時(shí)�����,該單通道 濾波器都必須充電到所選通道的值����,因而會(huì)限制吞吐速率。為 提高吞吐速率�,可以在多路復(fù)用器之前為每個(gè)通道添加一個(gè)濾 波器,但這樣做會(huì)提高成本�。

圖4.多路復(fù)用輸入信號(hào)鏈

2. 通帶平坦度和過(guò)渡帶限制與噪聲的關(guān)系

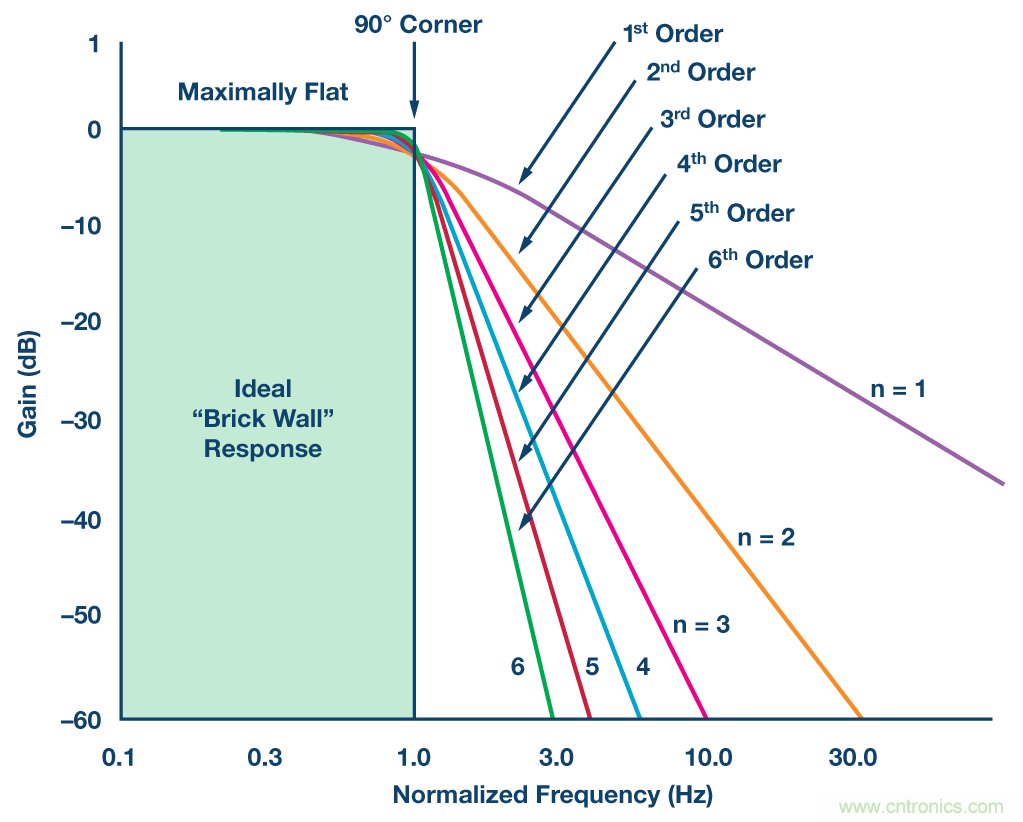

遭遇高噪聲的應(yīng)用,尤其是在接近第一奈奎斯特區(qū)邊緣處發(fā)生 很高干擾的應(yīng)用�����,需要滾降厲害的濾波器���。然而����,人們已從實(shí)際模擬低通濾波器得知:從低頻到高頻��,幅 度會(huì)滾下來(lái)��,并有一個(gè)過(guò)渡帶���。增加濾波器級(jí)數(shù)或階數(shù)可以改 善帶內(nèi)信號(hào)的平坦度����,并使過(guò)渡帶收窄�����。然而��,這些濾波器的 設(shè)計(jì)很復(fù)雜����,因?yàn)樗鼈儗?duì)增益匹配非常敏感,以至于無(wú)法實(shí)現(xiàn) 數(shù)階的衰減幅度����。此外��,在信號(hào)鏈中增加任何元件(如電阻或 放大器)都會(huì)引入帶內(nèi)噪聲�����。

圖5.不同階數(shù)的理想巴特沃茲濾波器過(guò)渡帶

對(duì)于某些具體應(yīng)用�����,模擬濾波器設(shè)計(jì)的復(fù)雜度和性能需要進(jìn)行 取舍。例如�����,在采用AD7606的電力線(xiàn)繼電器保護(hù)應(yīng)用中�����,對(duì) 于50 Hz/60 Hz 基頻輸入信號(hào)及其相關(guān)前五次諧波�,保護(hù)通道 的精度要求低于測(cè)量通道。保護(hù)通道可以使用一個(gè)一階RC 濾 波器�,而測(cè)量通道使用二階RC 濾波器,以便提供更好的帶內(nèi) 平坦度和更急劇的滾落過(guò)渡����。

3. 同步采樣的相位延遲和匹配誤差

濾波器設(shè)計(jì)不僅僅關(guān)系到頻率設(shè)計(jì),用戶(hù)可能還需要考慮模擬 濾波器的時(shí)域特性和相位響應(yīng)��。在某些實(shí)時(shí)應(yīng)用中��,相位延遲 可能非常重要��。如果相位隨輸入頻率而變化,那么相位變動(dòng)將 更糟糕���。濾波器的相位變化一般用群延遲來(lái)衡量�����。對(duì)于非常數(shù) 群延遲,信號(hào)會(huì)在時(shí)間中擴(kuò)散�����,導(dǎo)致脈沖響應(yīng)變得很差�。

對(duì)于多通道同步采樣應(yīng)用,例如電機(jī)控制或電力線(xiàn)監(jiān)控中的相 電流測(cè)量�����,還應(yīng)考慮相位延遲匹配誤差�。確保濾波器在多個(gè)通 道上引起的額外相位延遲匹配誤差可以忽略不計(jì),或者在工作 溫度范圍的信號(hào)鏈誤差預(yù)算范圍內(nèi)����。

4.低失真和低噪聲應(yīng)用的元件選擇挑戰(zhàn)

對(duì)于低諧波失真和低噪聲應(yīng)用,用戶(hù)必須為信號(hào)鏈設(shè)計(jì)選擇合 乎要求的元件�����。模擬電子元件不是完全線(xiàn)性的,會(huì)引起諧波失 真�。Walsh 的文章中討論了如何選擇低失真放大器和如何計(jì)算 放大器噪聲。放大器等有源元件需要低THD + N��,同時(shí)也要考 慮普通電阻和電容等無(wú)源元件的失真和噪聲��。

電阻的非線(xiàn)性有兩個(gè)來(lái)源:電壓系數(shù)和功率系數(shù)��。根據(jù)具體應(yīng) 用��,高性能信號(hào)鏈可能需要使用由特定技術(shù)制造的電阻����,如薄 膜或金屬電阻。如果選擇不當(dāng)�����,輸入濾波電容可能會(huì)造成顯著 失真��。如果成本預(yù)算允許�����,聚苯乙烯和NP0/C0G 陶瓷電容是 很好的備選元件,可以改善THD���。

除放大器噪聲外��,電阻和電容也會(huì)有電子噪聲�,后者是由處于 均衡態(tài)的電導(dǎo)體內(nèi)部的電荷載子的熱擾動(dòng)產(chǎn)生的����。RC 電路的 熱噪聲有一個(gè)簡(jiǎn)單的表達(dá)式�����,電阻R 是滿(mǎn)足濾波要求所需要 的�����,同時(shí)R 越高��,相應(yīng)的熱噪聲也越大����。RC 電路的噪聲帶寬 為1/(4RC)。

除放大器噪聲外�����,電阻和電容也會(huì)有電子噪聲,后者是由處于 均衡態(tài)的電導(dǎo)體內(nèi)部的電荷載子的熱擾動(dòng)產(chǎn)生的��。RC 電路的 熱噪聲有一個(gè)簡(jiǎn)單的表達(dá)式�,電阻R 是滿(mǎn)足濾波要求所需要 的,同時(shí)R 越高��,相應(yīng)的熱噪聲也越大��。RC 電路的噪聲帶寬 為1/(4RC)�����。

kB (玻爾茲曼常數(shù)) = 1.38065 × 10–23m2kgs–2K–1

T 為溫度 (K)

f 為磚墻濾波器近似帶寬

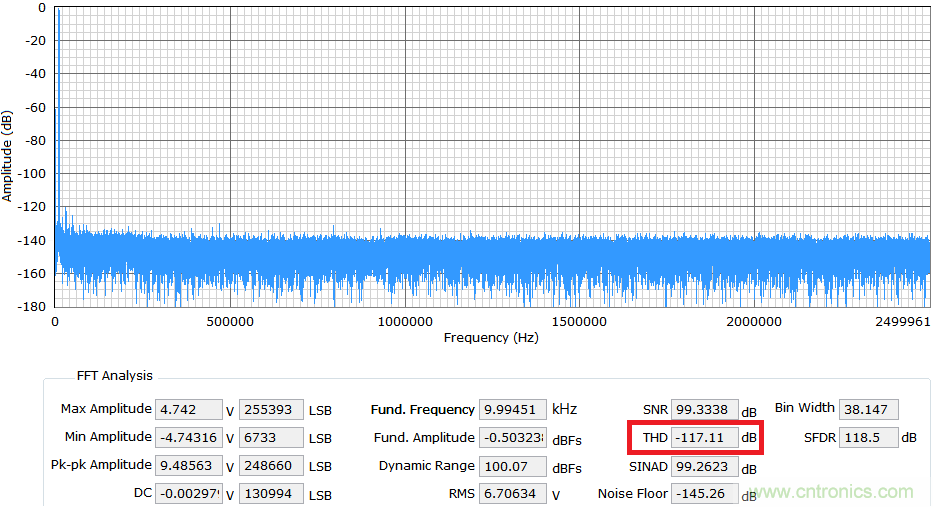

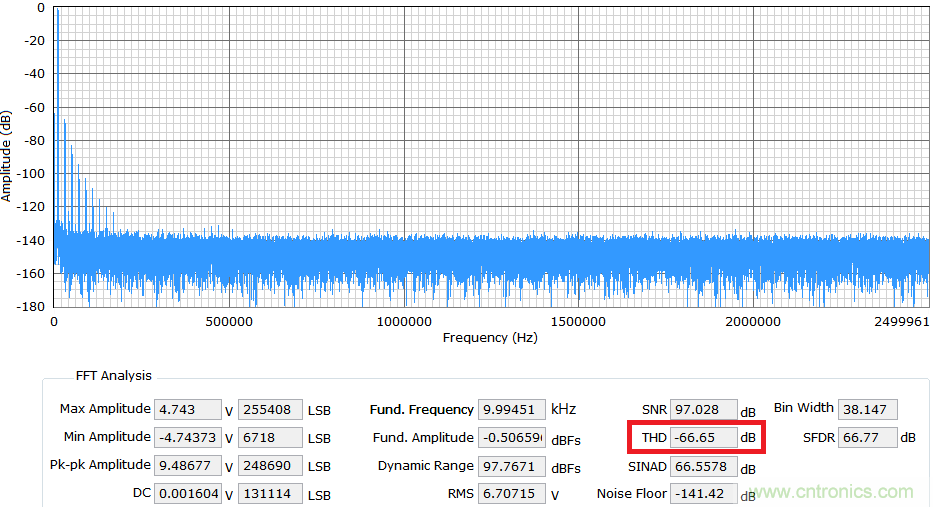

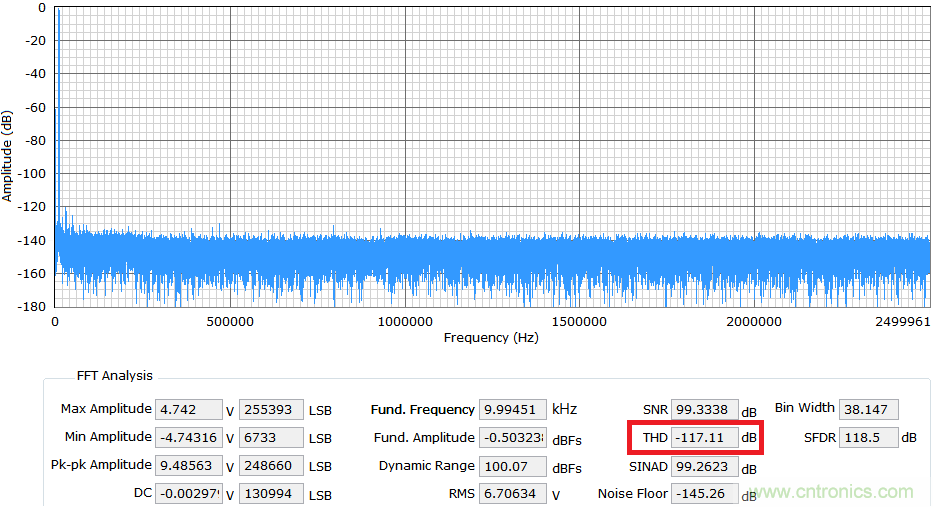

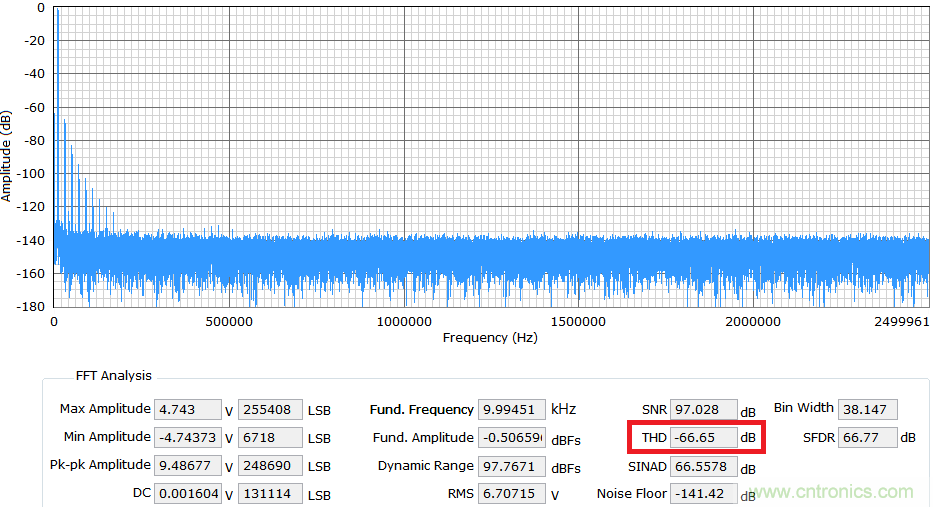

圖6 顯示在EVAL-AD7960FMCZ評(píng)估板上��,NP0 電容和X7R 電容對(duì)THD 性能的影響:(a) 顯示一個(gè)10 kHz 正弦波信號(hào)音 的頻譜�����,C76 和C77 為1 nF 0603 NP0 電容��,而 (b) 顯示使用 1 nF 0603 X7R 電容時(shí)的頻譜�����。

(a) 0603 1nF NP0 電容

(b) 0603 1nF X7R 電容

圖6.在EVAL-AD7960FMCZ 評(píng)估板上NP0 和X7R 電容對(duì)THD 的影響

了解前面的設(shè)計(jì)考慮之后,便可利用ADI 公司的模擬濾波器向?qū)гO(shè)計(jì)有源模擬濾波器�����。它會(huì)根據(jù)應(yīng)用要求計(jì)算電容和電阻值��,并選擇合適的放大器����。

數(shù)字濾波器考慮

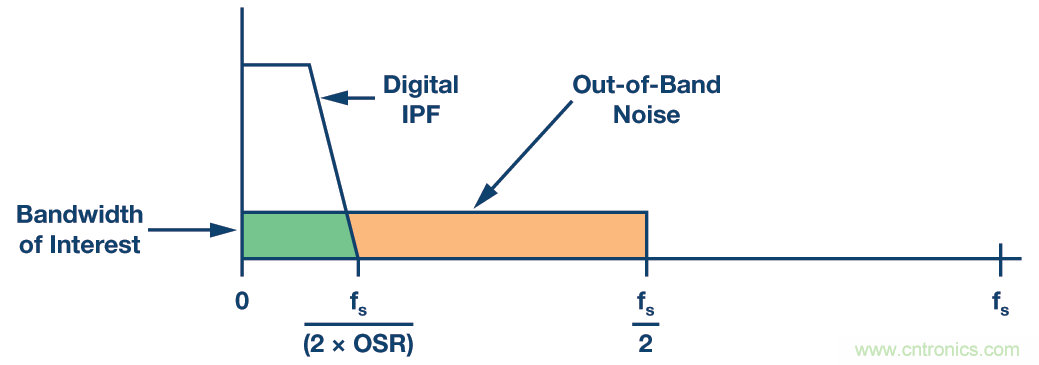

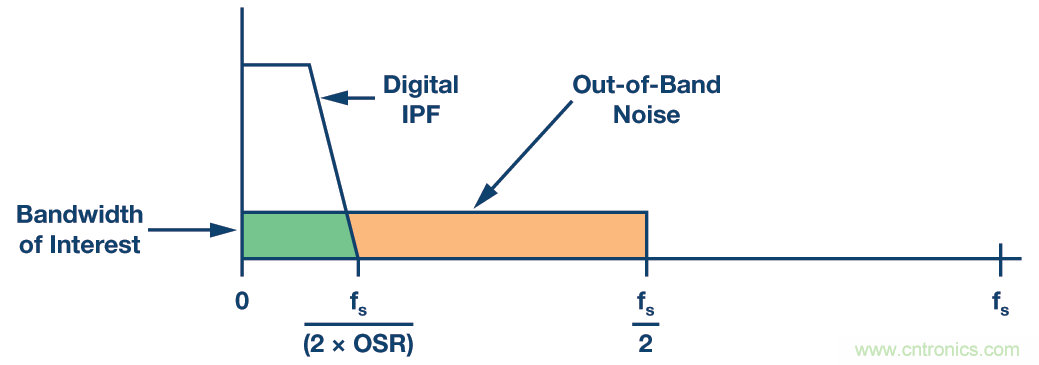

SAR 型和Σ-Δ 型ADC 正在穩(wěn)步實(shí)現(xiàn)更高的采樣速率和輸入帶 寬。以?xún)杀赌慰固厮俾蕦?duì)一個(gè)信號(hào)過(guò)采樣�,會(huì)將ADC 量化 噪聲能量均勻擴(kuò)散到兩倍頻段中����。這樣便很容易設(shè)計(jì)數(shù)字濾波 器來(lái)限制數(shù)字化信號(hào)的頻帶,然后通過(guò)抽取來(lái)提供所需的最終 采樣速率���。這種技術(shù)可降低帶內(nèi)量化誤差并提高ADC SNR��。 它還能放寬濾波器滾降要求�����,從而減輕抗混疊濾波器的壓力�����。 過(guò)采樣降低了對(duì)濾波器的要求�����,但需要更高采樣速率ADC 和 更快的數(shù)字處理����。

1. 對(duì)ADC 使用過(guò)采樣速率所取得的實(shí)際SNR 改善

利用過(guò)采樣和抽取濾波器所取得的SNR 改善,可從N 位ADC 的 理論SNR 求得:SNR = 6.02 × N + 1.76 dB + 10 × log10[OSR]���, OSR = fs/(2 × BW)�。注意:此公式僅適用于只存在量化噪聲的 理想ADC�。

圖7.奈奎斯特轉(zhuǎn)換器過(guò)采樣

還有很多其他因素會(huì)將噪聲引入ADC 轉(zhuǎn)換代碼中。例如:信 號(hào)源和信號(hào)鏈器件的噪聲���,芯片熱噪聲����,散粒噪聲�����,電源噪聲, 基準(zhǔn)電壓噪聲����,數(shù)字饋通噪聲,以及采樣時(shí)鐘抖動(dòng)引起的相位 噪聲�。這種噪聲可能會(huì)均勻分布在信號(hào)頻段中,表現(xiàn)為閃爍噪 聲����。因此,實(shí)際實(shí)現(xiàn)的ADC SNR 改善幅度一般低于用公式計(jì) 算出的值�����。

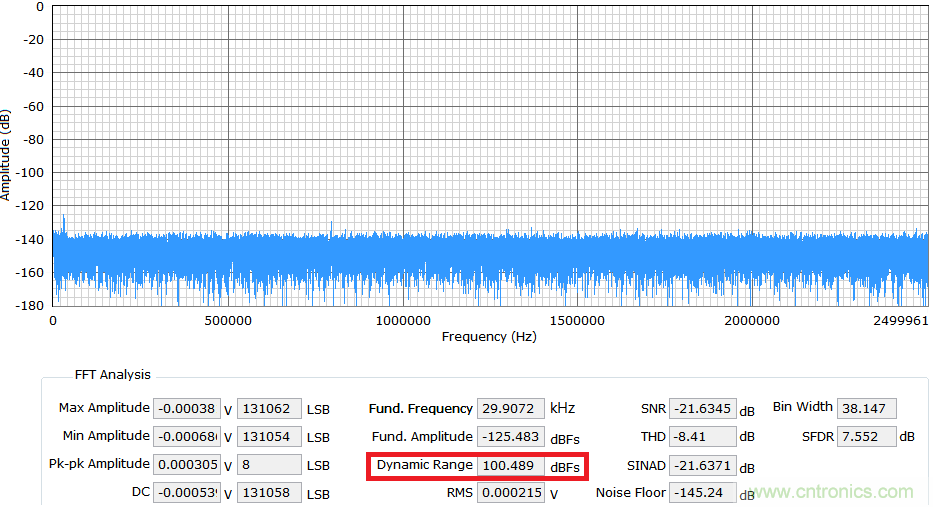

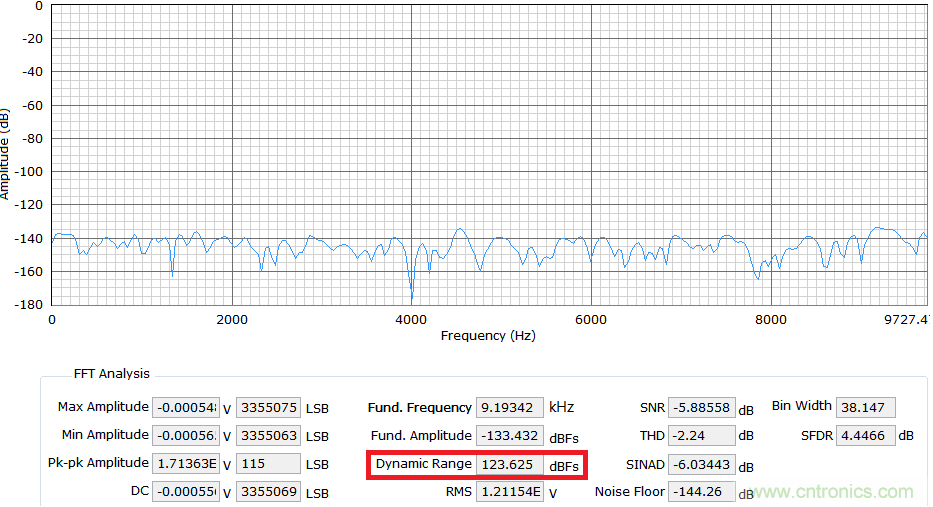

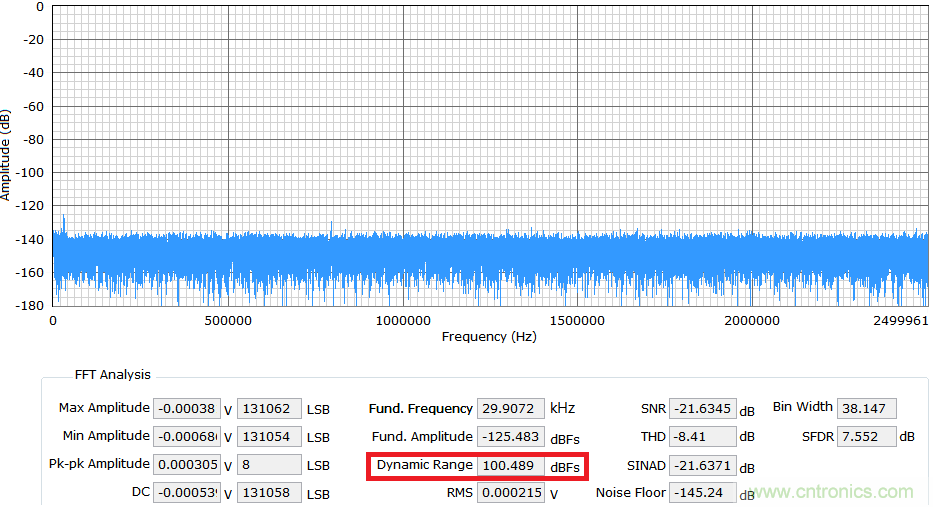

2. EVAL-AD7960FMCZ 評(píng)估板上利用過(guò)采樣實(shí)現(xiàn)的動(dòng)態(tài)改善

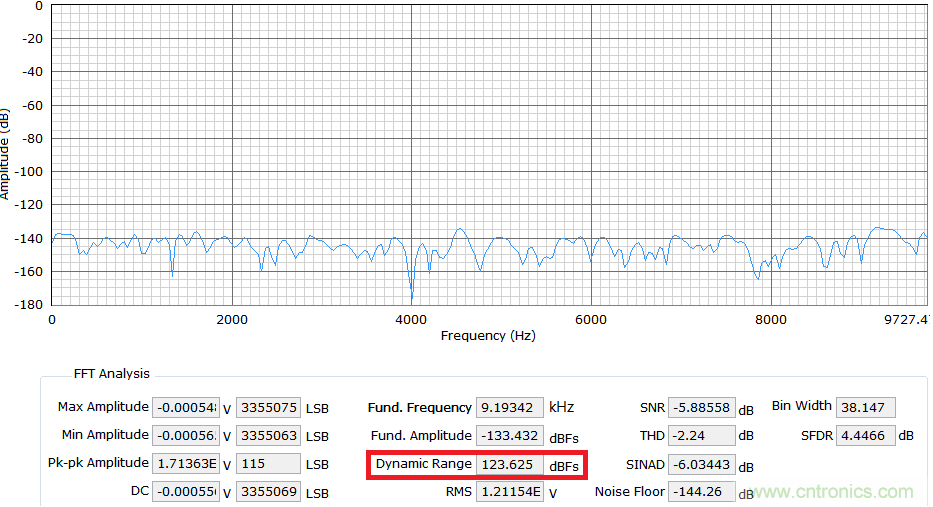

在應(yīng)用筆記AN-1279 中�����,256×過(guò)采樣下18 位AD7960 ADC 的 實(shí)測(cè)動(dòng)態(tài)范圍為123 dB�����。這是用于高性能數(shù)據(jù)采集信號(hào)鏈���,如 光譜分析����、磁共振成像 (MRI)���、氣相色譜分析��、振動(dòng)��、石油/ 天然氣勘探和地震系統(tǒng)等��。

如圖8 所示�����,與理論SNR 改善幅度計(jì)算相比���,測(cè)得的過(guò)采樣 動(dòng)態(tài)范圍低1 dB 至2 dB。原因是來(lái)自信號(hào)鏈器件的低頻噪聲 限制了總體動(dòng)態(tài)范圍性能��。

(a) 無(wú)OSR 的動(dòng)態(tài)范圍

(b) OSR = 256 的動(dòng)態(tài)范圍

圖8.OSR 256 時(shí)的動(dòng)態(tài)范圍改善

3. 充分利用SAR 型和Σ-Δ 型ADC 中的集成數(shù)字濾波器

數(shù)字濾波器通常位于FPGA��、DSP 或處理器中�。為了減少系統(tǒng) 設(shè)計(jì)工作,ADI 公司提供了一些集成后置數(shù)字濾波器的精密 ADC。例如���,AD7606 集成了一個(gè)一階后置數(shù)字sinc 濾波器用 于過(guò)采樣����。它很容易配置����,只需上拉或下拉OS 引腳。Σ-Δ 型 ADC AD7175-x 不僅有傳統(tǒng)sinc3 濾波器���,還有sinc5 + sinc1 和增強(qiáng)型50 Hz/60 Hz 抑制濾波器�����。AD7124-x 提供快速建立模 式(sinc4 + sinc1 或sinc3 + sinc1 濾波器)功能�。

4.多路復(fù)用采樣ADC 的延遲取舍

延遲是數(shù)字濾波器的一個(gè)缺點(diǎn)����,它取決于數(shù)字濾波器階數(shù)和主 時(shí)鐘速率。對(duì)于實(shí)時(shí)應(yīng)用和環(huán)路響應(yīng)時(shí)間���,應(yīng)當(dāng)限制延遲。數(shù) 據(jù)手冊(cè)所列的輸出數(shù)據(jù)速率是指在單一通道上執(zhí)行連續(xù)轉(zhuǎn)換 時(shí)轉(zhuǎn)換結(jié)果有效的速率��。當(dāng)用戶(hù)切換到另一通道時(shí),建立Σ-Δ 調(diào)制器和數(shù)字濾波器還額外需要些時(shí)間��。與這些轉(zhuǎn)換器相關(guān)的 建立時(shí)間是指通道變更之后輸出數(shù)據(jù)反映輸入電壓所需的時(shí) 間���。通道變更之后����,為精確反映模擬輸入���,必須清除數(shù)字濾波 器中與前一模擬輸入相關(guān)的全部數(shù)據(jù)�。

以前����,Σ-Δ 型ADC 的通道切換速度比數(shù)據(jù)輸出速率要小得多。 因此����,在多路復(fù)用數(shù)據(jù)采集系統(tǒng)等切換應(yīng)用中,必須明白:獲 得轉(zhuǎn)換結(jié)果的速率要比對(duì)單一通道連續(xù)采樣時(shí)可達(dá)到的轉(zhuǎn)換 速率低好幾倍�����。

ADI 公司的某些新型Σ-Δ ADC(如AD7175-x)內(nèi)置優(yōu)化的數(shù)字 濾波器,可減少通道切換時(shí)的建立時(shí)間�。AD7175-x 的sinc5 + sinc1 濾波器主要用于多路復(fù)用應(yīng)用,在10 kSPS 和更低的輸出 數(shù)據(jù)速率時(shí)���,可實(shí)現(xiàn)單周期建立���。

5.數(shù)字濾波器通過(guò)抽取避免混疊

很多文章都討論過(guò),過(guò)采樣頻率越高�����,模擬濾波器設(shè)計(jì)就越容 易����。當(dāng)采樣速率高于滿(mǎn)足奈奎斯特準(zhǔn)則所需的速率時(shí),便可使 用較簡(jiǎn)單的模擬濾波器來(lái)避免受到極高頻率所產(chǎn)生的混疊影 響���。很難設(shè)計(jì)一個(gè)能夠衰減所需頻段而不失真的模擬濾波器����, 但很容易設(shè)計(jì)一個(gè)利用過(guò)采樣抑制較高頻率的模擬濾波器��。這 樣便很容易設(shè)計(jì)數(shù)字濾波器來(lái)限制轉(zhuǎn)換信號(hào)的頻帶�����,然后通過(guò) 抽取來(lái)提供所需的最終采樣速率�����,但又不會(huì)喪失所需信息�。

實(shí)施抽取之前,需要確保這種重新采樣不會(huì)引入新的混疊問(wèn) 題�。抽取之后,確保輸入信號(hào)符合奈奎斯特關(guān)于采樣速率的 理論�����。

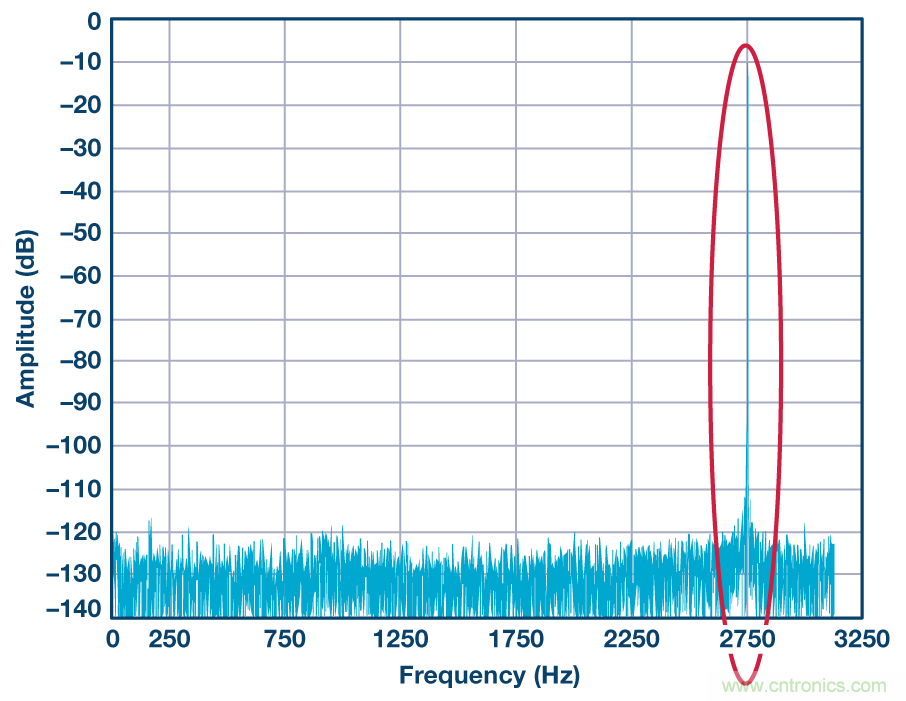

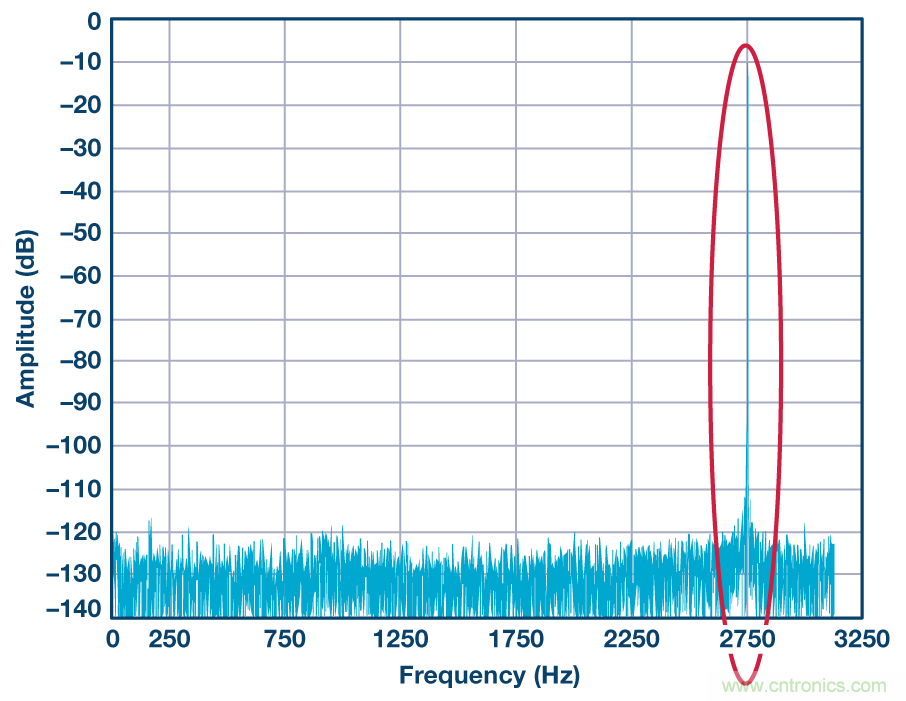

EVAL-AD7606/EVAL-AD7607/EVAL-AD7608EDZ 評(píng)估板可以每 通道200 kSPS 的速率運(yùn)行���。在下面的測(cè)試中����,配置其采樣速率為 6.25 kSPS�����,過(guò)采樣比為32����。然后�����,將一個(gè)3.5 kHz –6 dBFS 正弦 波施加于AD7606�。圖9 顯示2.75 kHz (6.25 kHz – 3.5 kHz) 處有 一個(gè)–10 dBFS 混疊鏡像�����。因此����,若ADC 之前沒(méi)有合格的抗混疊 模擬濾波器,當(dāng)使用過(guò)采樣時(shí)�����,數(shù)字濾波器就可能會(huì)因?yàn)槌槿《?引起混疊鏡像�����。應(yīng)使用模擬抗混疊濾波器來(lái)消除這種疊加于模擬 信號(hào)上的噪聲尖峰�。

圖9.OSR 抽取采樣率小于奈奎斯特頻率時(shí)的混疊

結(jié)論

本文討論的挑戰(zhàn)和考慮可幫助設(shè)計(jì)人員設(shè)計(jì)出實(shí)用的濾波器 以實(shí)現(xiàn)精密采集系統(tǒng)的目標(biāo)。模擬濾波器必須在不違反系統(tǒng)誤 差預(yù)算的條件下與SAR 型或Σ-Δ 型ADC 的非理想輸入結(jié)構(gòu)接 口�����,數(shù)字濾波器不應(yīng)在處理器端引起誤差。這不是簡(jiǎn)單的任務(wù)����, 必須在系統(tǒng)規(guī)格�、響應(yīng)時(shí)間、成本��、設(shè)計(jì)工作量和資源等方面 做出權(quán)衡���。

推薦閱讀: