【導(dǎo)讀】在測(cè)試和驗(yàn)證分辨率高于16位的高精度快速模數(shù)轉(zhuǎn)換器(ADC)的交流性能時(shí),需要用到近乎完美的正弦波生成器,該生成器至少支持0 kHz至20 kHz音頻帶寬。通常會(huì)使用價(jià)格高昂的實(shí)驗(yàn)室儀器儀表來執(zhí)行這些評(píng)估和特性表征,例如Audio Precision提供的音頻分析儀AP27xx或APx5xx系列。

簡(jiǎn)介

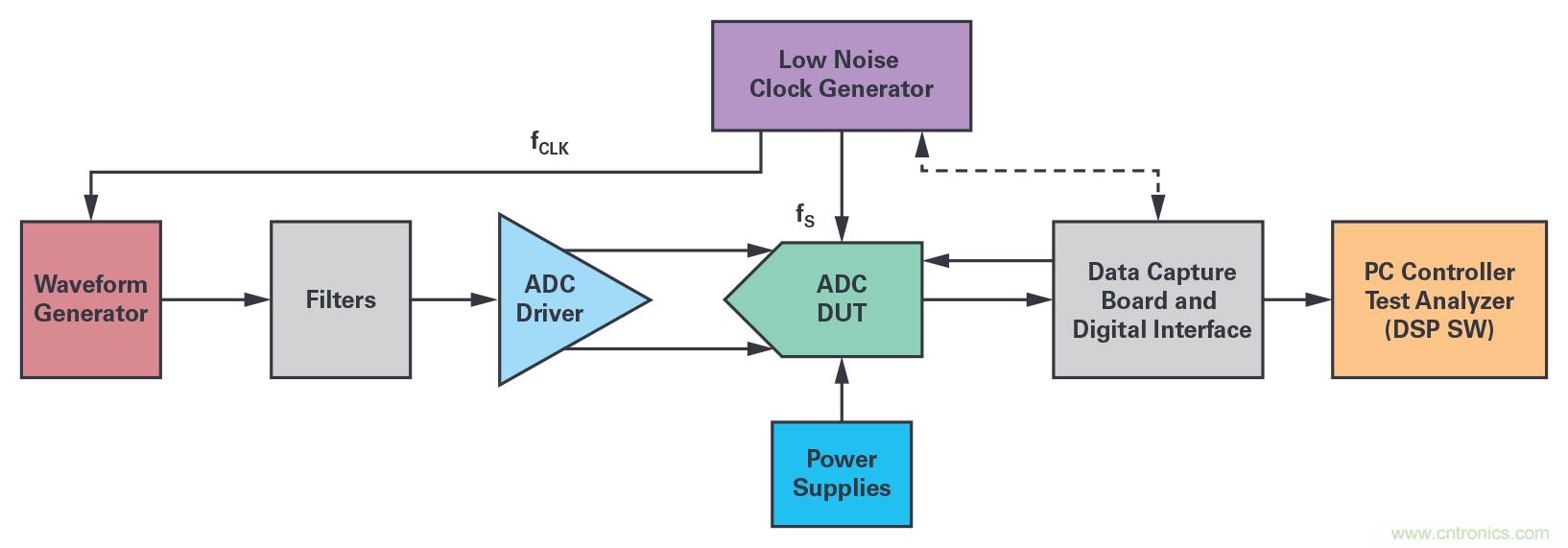

在測(cè)試和驗(yàn)證分辨率高于16位的高精度快速模數(shù)轉(zhuǎn)換器(ADC)的交流性能時(shí),需要用到近乎完美的正弦波生成器,該生成器至少支持0 kHz至20 kHz音頻帶寬。通常會(huì)使用價(jià)格高昂的實(shí)驗(yàn)室儀器儀表來執(zhí)行這些評(píng)估和特性表征,例如Audio Precision提供的音頻分析儀AP27xx或APx5xx系列。大多數(shù)情況下,24位或更高分辨率的現(xiàn)代高速SAR和寬帶Σ-Δ ADC都采用單電源和全差分輸入,因此要求用于DUT的信號(hào)源具備準(zhǔn)確的直流和交流性能,同時(shí)提供全差分輸出(180°錯(cuò)相)。同樣,這款交流生成器的噪聲和失真水平應(yīng)該遠(yuǎn)優(yōu)于這些ADC的規(guī)格,根據(jù)大部分供應(yīng)商提供的規(guī)格,其本底噪聲水平遠(yuǎn)低于–140 dBc,失真水平低于–120 dBc,輸入信號(hào)音頻率為1 kHz或2 kHz,最高可達(dá)20 kHz。有關(guān)適合高分辨率帶寬ADC的典型測(cè)試臺(tái)的典型測(cè)試配置,請(qǐng)參考圖1。最關(guān)鍵的元件就是正弦波生成器(單信號(hào)音或多信號(hào)音),其中基于軟件的直接數(shù)字頻率合成器(DDS)可以提供完全的靈活性、極高的頻率分辨率和時(shí)鐘同步性能,利用數(shù)據(jù)采集系統(tǒng)來執(zhí)行相干取樣,以避免泄漏和FFT窗口濾波。

因?yàn)槌杀局挥幸纛l精密分析儀的幾分之一,所以能夠基于直接數(shù)字頻率合成(DDFS)原理設(shè)計(jì)非常精準(zhǔn)的正弦波生成器,但需要通過軟件在SHARC®處理器等浮點(diǎn)DSP處理器上實(shí)現(xiàn)。一個(gè)相當(dāng)快的浮點(diǎn)DSP將能滿足實(shí)時(shí)性要求,以及所有算法和處理?xiàng)l件,以達(dá)到先進(jìn)的SAR ADC所設(shè)置的失真和噪聲性能水平。通過利用SHARC內(nèi)核架構(gòu)的全字?jǐn)?shù)據(jù)長(zhǎng)度(32位或64位定點(diǎn)格式)來實(shí)施NCO相位累加,利用專有的40位浮點(diǎn)擴(kuò)展精度來執(zhí)行正弦近似函數(shù),以及利用數(shù)字濾波器來確定頻譜形狀,量化效應(yīng)(回轉(zhuǎn)噪聲和截?cái)嘣肼暎┑玫酱蠓档?,與用于信號(hào)重構(gòu)的數(shù)模轉(zhuǎn)換器(DAC)缺點(diǎn)相比,這種效應(yīng)可以忽略不計(jì)。

直接數(shù)字頻率合成

1970年4月,Joseph A. Webb1提出了數(shù)字信號(hào)生成器頻率合成器的專利申請(qǐng),其中描述了有關(guān)DDS生成包括正弦波等各種模擬波形的考慮因素,只需使用數(shù)個(gè)數(shù)字邏輯模塊即可實(shí)現(xiàn)。之后,Tierney等人2在1971年初發(fā)表了論文(后來成為大家頻繁引用的參考文獻(xiàn)),闡述了通過深化DDS操作進(jìn)行正交生成來實(shí)現(xiàn)直接數(shù)字頻率生成,以及采樣系統(tǒng)理論相關(guān)局限性(字詞截?cái)郲HJ1] 和頻率規(guī)劃)問題。隨后出現(xiàn)的實(shí)際應(yīng)用大部分依賴于分立式標(biāo)準(zhǔn)邏輯IC,例如TTL 74xx或ECL 10K系列。后來在不到10年的時(shí)間里,Stanford Telecom、Qualcomm、Plessey和ADI等紛紛推出了完全集成式解決方案,例如ADI的AD9950和AD9955。這些邏輯IC旨在實(shí)現(xiàn)速度、功率[HJ2] 和成本之間的最佳平衡,其架構(gòu)基于查找表(LUT),以確保在有限相位、頻率和幅度分辨率下實(shí)現(xiàn)相位-正弦幅度轉(zhuǎn)換。如今,ADI公司仍然是DDS獨(dú)立集成電路的最大供應(yīng)商,可能也是最獨(dú)特的供應(yīng)商,而當(dāng)前的數(shù)控振蕩器(NCO)往往都集成到AD9164 或AD9174之類RF DAC中。雖然這些器件在多GHz帶寬上具備出色的噪聲和線性度性能,但它們都不適合測(cè)試中等速度、高分辨率ADC,例如LTC2378-20、AD4020或AD7768。

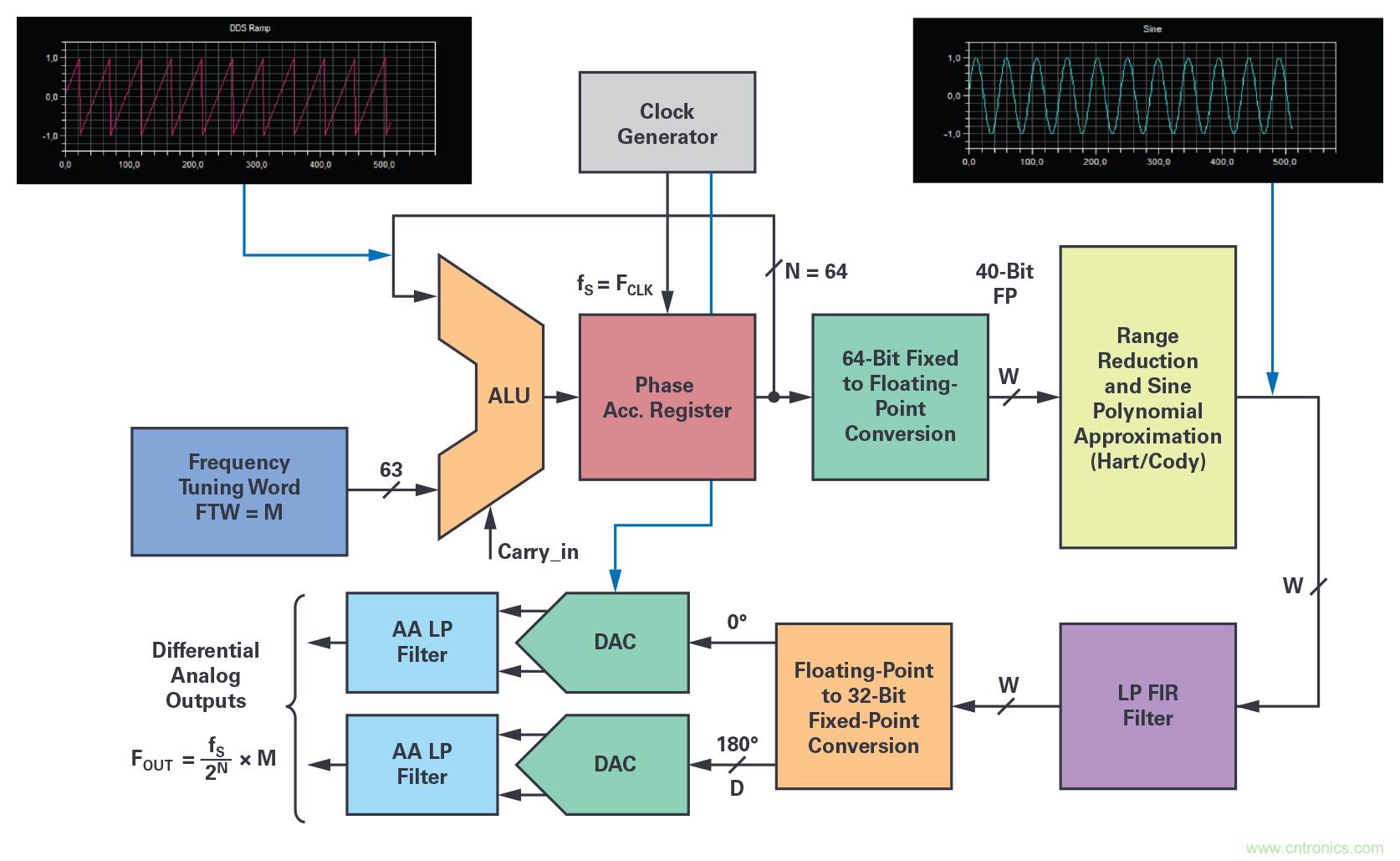

圖1.基于IEEE 1241標(biāo)準(zhǔn)的典型ADC(ac)測(cè)試設(shè)置的處理鏈。DDFS能夠讓整個(gè)測(cè)量系統(tǒng)完全實(shí)現(xiàn)數(shù)字化,具備多種優(yōu)勢(shì),包括完全的靈活性和相干取樣采集

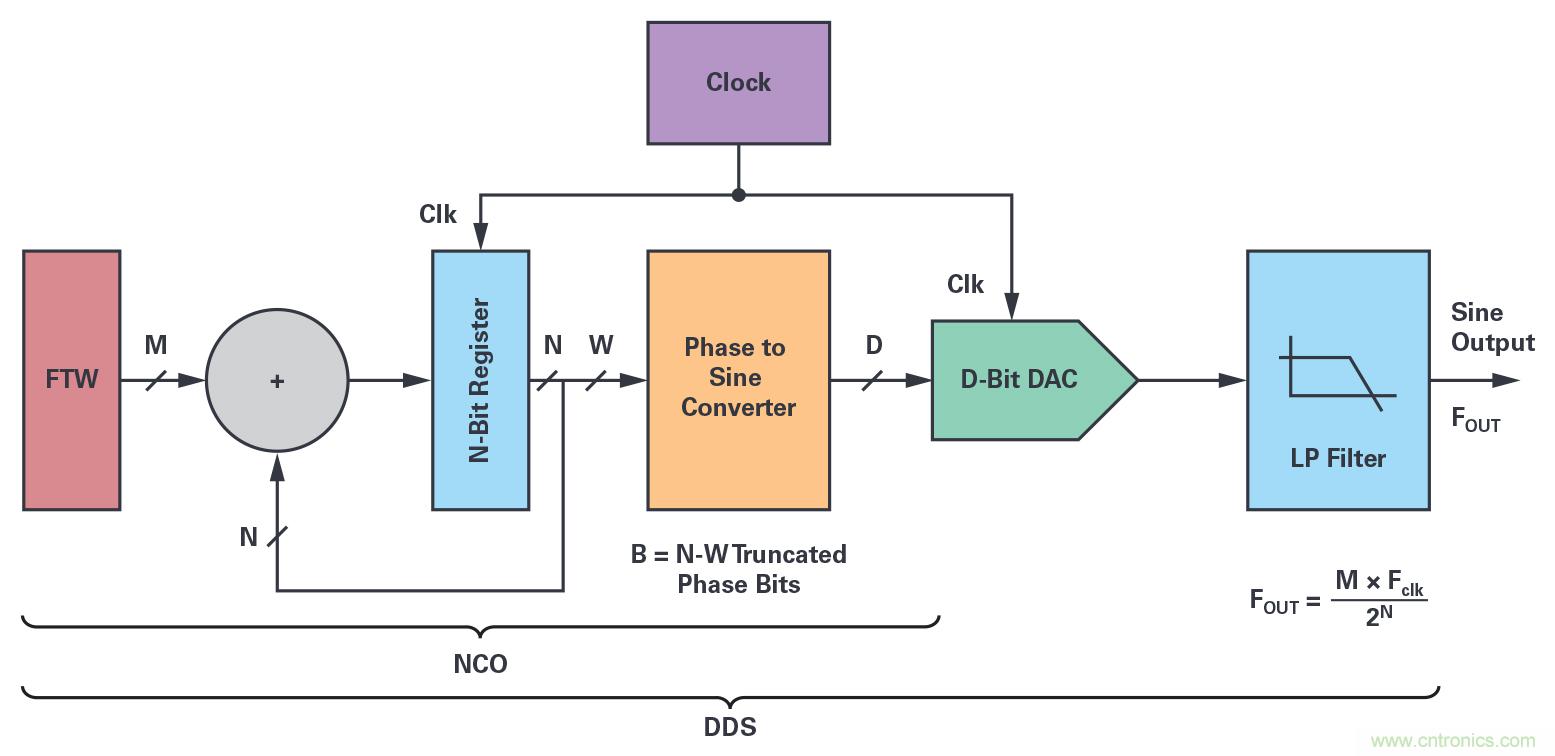

與基于PLL的傳統(tǒng)頻率合成器相比,NCO和DDS的顯著優(yōu)勢(shì)包括:極高的頻率分辨率、快速靈敏性,以及可輕松生成完美正交的正弦/余弦波形。此外,還提供寬帶寬范圍和高直流精度。其工作原理受[HJ3] 數(shù)字信號(hào)處理和采樣系統(tǒng)理論,數(shù)字特性支持對(duì)輸出信號(hào)的相位、頻率和幅度實(shí)施全數(shù)字獨(dú)立控制。圖2所示的框圖顯示傳統(tǒng)DDS的架構(gòu),該DDS由三大功能模塊組成:

u N位相位累加器;

u 相位-正弦幅度轉(zhuǎn)換器,由W位截取相位輸入字表征特性;

u D位DAC及其相關(guān)重構(gòu)濾波器。

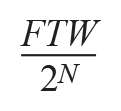

相位累加器由簡(jiǎn)單的N位加法器結(jié)合寄存器構(gòu)成,寄存器的內(nèi)容按照采樣時(shí)鐘FCLK的速率,以輸入相位增量Δθ(通常也稱為頻率調(diào)諧字,F(xiàn)TW)更新。累加器會(huì)定期溢出,在采樣或參考時(shí)鐘FCLK和DDS輸出頻率FOUT之間像小數(shù)分頻器一樣運(yùn)行,或像齒輪箱一樣運(yùn)行,分頻比為:

溢出速率為生成的波形提供輸出頻率,使得:

其中0 ≤ FTW ≤ 2N–1。因?yàn)榉诸l器的原因,NCO輸出端的參考或采樣fS時(shí)鐘相位噪聲的影響會(huì)降低

相位累加器寄存器的輸出表示生成波形的電流相位。每個(gè)分立式累加器輸出相位值然后通過相位-正弦或相位-余弦映射引擎,被轉(zhuǎn)換成幅度正弦或余弦數(shù)據(jù)或樣本。此功能通常利用存儲(chǔ)在LUT(ROM)中的三角函數(shù)值完成,有時(shí)通過執(zhí)行正弦近似算法完成,或兩者組合方式完成。相位-正弦幅度轉(zhuǎn)換器的輸出供DAC使用,在濾波之前生成量化和采樣正弦信號(hào),使信號(hào)平穩(wěn),并避免頻譜混疊。由DAC有限分辨率導(dǎo)致的幅度量化設(shè)定了本底噪聲以及相應(yīng)的頻率合成器信噪比(SNR)的理論限值。此外,DAC作為混合信號(hào)器件,由于其INL、DNL、壓擺率、毛刺和建立時(shí)間等特性,展現(xiàn)出一系列直流和交流非線性,這會(huì)產(chǎn)生雜散信號(hào)音,縮小正弦波生成器的整個(gè)動(dòng)態(tài)范圍。

基于圖2中架構(gòu)實(shí)現(xiàn)的實(shí)際正弦波形生成器,主要是相位-幅度轉(zhuǎn)換模塊不同,受數(shù)字無線電應(yīng)用這一市場(chǎng)導(dǎo)向影響,該模塊通常針對(duì)速度和功耗,而不是高精度而優(yōu)化。實(shí)施相位-正弦幅度轉(zhuǎn)換器最簡(jiǎn)單的方法就是使用ROM,采用一對(duì)一映射的方式來存儲(chǔ)正弦值。遺憾的是,LUT的長(zhǎng)度與相位累加器的寬度N呈指數(shù)增長(zhǎng)(2N),并且與波表數(shù)據(jù)字精度W呈線性增長(zhǎng)。而且,減小累加器的尺寸或截?cái)嗥漭敵鲋g的權(quán)衡和取舍會(huì)導(dǎo)致頻率分辨率降低,并且嚴(yán)重降低SFDR的性能。結(jié)果表明,相位或幅度量化導(dǎo)致的雜散會(huì)降低–6 dB/位。實(shí)現(xiàn)精細(xì)的頻率調(diào)諧通常需要較大的N,已有幾種技術(shù)可用來限制ROM的尺寸,同時(shí)保持足夠的雜散性能。一般會(huì)使用簡(jiǎn)單的壓縮方法,利用正弦或余弦函數(shù)的四分之一波長(zhǎng)對(duì)稱性將相位幅度范圍減小4倍。為了進(jìn)一步縮小范圍,實(shí)際會(huì)使用截?cái)嘞辔焕奂悠鬏敵龅姆椒ǎ贿^這會(huì)導(dǎo)致產(chǎn)生雜散諧波。盡管如此,這種方法也因精準(zhǔn)的頻率分辨率要求、存儲(chǔ)器尺寸和成本考量而得到了廣泛采用。建議采用多種角分解方法,以降低基于LUT的方法對(duì)存儲(chǔ)器的要求。與使用各種分段、線性或多項(xiàng)式內(nèi)插法的幅度壓縮結(jié)合,在進(jìn)行需要正弦和余弦函數(shù)的I/Q合成時(shí),準(zhǔn)確估算正弦函數(shù)的第一象限,或按[0, π/4]間隔估算。同樣,在沒有ROM LUT的情況下,只需要按照逐次逼近的方法調(diào)用位移和添加操作,即可使用基于角旋轉(zhuǎn)的方法有效生成復(fù)雜信號(hào)。這種方法以流行的CORDIC為代表,當(dāng)硬件乘法器不可用時(shí),或者出于速度或成本考慮,應(yīng)最大限度減少實(shí)施函數(shù)所需的柵級(jí)數(shù)量時(shí)(在FPGA或ASIC中),此方法通常比其他方法更快。相反,當(dāng)硬件乘法器可用時(shí)(在DSP微處理器中總是如此),采用插入方法和完整多項(xiàng)式計(jì)算(例如泰勒級(jí)數(shù)展開、切比雪夫多項(xiàng)式)的表查找要比CORDIC更快,尤其是要求高精度時(shí)。

圖2.NCO的主要功能部分,以及與完整的直接數(shù)字頻率合成器的區(qū)別,其中包括重構(gòu)DAC和其相關(guān)的AAF。NCO部分可用于測(cè)試或仿真DAC

在軟件中實(shí)現(xiàn)高精度NCO

如同著名的惠普分析儀,或者如同應(yīng)用筆記AN-1323中描述的那樣,構(gòu)建與最出色的模擬振蕩器具備同等或更出色的失真性能的高精度交流信號(hào)振蕩器并不容易,即使是針對(duì)音頻頻譜(直流至20 kHz范圍)。然而,如前所述,利用嵌入式處理器具有的足夠運(yùn)算精度來執(zhí)行相位計(jì)算(ωt)和正弦函數(shù)(sin(ωt))近似計(jì)算,從而完整實(shí)施軟件,這顯然有助于最大限度減少量化的不利影響、噪聲和由此導(dǎo)致的雜散。這意味著圖2中的所有NCO功能模塊都會(huì)轉(zhuǎn)換成代碼行(不是VHDL!),從而實(shí)現(xiàn)一個(gè)滿足實(shí)時(shí)約束的軟件版本,以確保實(shí)現(xiàn)最小的采樣速率和所需的頻率帶寬。

對(duì)于相位-正弦幅度轉(zhuǎn)換引擎,完整的LUT方案或任何變化都需要用到太多的存儲(chǔ)空間或太多的插值運(yùn)算來實(shí)現(xiàn)完美的正弦一致性。相反,用于計(jì)算正弦近似值的多項(xiàng)式方法允許使用成本極低的通用DSP,在復(fù)雜性與精度之間達(dá)成了不錯(cuò)的平衡。多項(xiàng)式級(jí)數(shù)展開也很有吸引力,因?yàn)樗鄬?duì)簡(jiǎn)單,并且能夠采用選擇的冪級(jí)數(shù)類型提供充分的靈活性,并且調(diào)整算法來實(shí)現(xiàn)給定精度。它不需要很大的存儲(chǔ)空間(可能不到100行SHARC DSP匯編代碼),只需要幾個(gè)RAM位置來存儲(chǔ)多項(xiàng)式系數(shù)和變量,因?yàn)檎抑抵辉诓蓸訒r(shí)刻計(jì)算。

首先,對(duì)于正弦近似值函數(shù),顯然會(huì)選擇使用具有適當(dāng)順序的泰勒/麥克勞林冪級(jí)數(shù)來滿足目標(biāo)精度。但是,由于冪級(jí)數(shù)在端點(diǎn)處往往會(huì)失效,所以在執(zhí)行任何多項(xiàng)式求值之前,必須將參數(shù)輸入范圍縮小到更小的區(qū)間。如果不縮小參數(shù)范圍,只能使用非常高階的多項(xiàng)式來支持在功能域(例如[–π, +π])中實(shí)現(xiàn)高精度。所以,需要對(duì)初等函數(shù)進(jìn)行一些變換,以獲取所需的約化參數(shù),例如sin(|x|) = sin(f + k × π/2)和sin(f) = sin(x – k × π/2),其中0 ≤f<π/2。因此,對(duì)于三角函數(shù),要特別注意不要使用減法相消,以免嚴(yán)重降低精度,并導(dǎo)致災(zāi)難性后果,特別是在運(yùn)算精度極差的情況下。在我們的例子中,當(dāng)相位輸入大于或接近π/2的整數(shù)倍數(shù)時(shí),會(huì)發(fā)生這種情況。

除了周期性和modulo-2π重復(fù)之外,sin(x)函數(shù)的對(duì)稱性可用于進(jìn)一步縮小近似值范圍。鑒于正弦函數(shù)在區(qū)間[0, 2π]內(nèi),關(guān)于點(diǎn)x = π不對(duì)稱,所以能夠使用以下關(guān)系式:

將范圍縮小到[0, π]。采用同樣的方式,sin(x)在區(qū)間[0, π]內(nèi),關(guān)于由x = π/2定義的線對(duì)稱,所以:

x在區(qū)間[0, π/2]以內(nèi),這會(huì)進(jìn)一步縮小角輸入近似值的范圍。通過進(jìn)一步縮小參數(shù)區(qū)間(例如[0, π/4])來提高精度并不是有效方法,因?yàn)檫@需要同時(shí)估算正弦和余弦函數(shù)的值,如常用三角關(guān)系所示:sin(a+b) = sin(a) × cos(b) + cos(a) × sin(b),從生成正交信號(hào)這一角度,這有其價(jià)值。

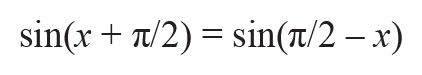

ADI公司的ADSP-21000系列應(yīng)用手冊(cè)第1卷描述了一個(gè)近乎理想的(用于嵌入式系統(tǒng))正弦近似值函數(shù),該函數(shù)基于為第一個(gè)ADI DSP浮點(diǎn)處理器編寫的冪級(jí)數(shù)優(yōu)化,即ADSP-21020,后者基本上屬于SHARC核。這種sin(x)的實(shí)現(xiàn)方法依賴于Hart等人4發(fā)布、由Cody和Waite5完善、適用于浮點(diǎn)運(yùn)算的極大極小逼近多項(xiàng)式,以減少舍入錯(cuò)誤和避免出現(xiàn)前面提到的取消。極大極小方法依賴于切比雪夫多項(xiàng)式和雷米茲交換算法來確定所需的最大相對(duì)誤差的系數(shù)。如圖3中的MATLAB®所示,與第七階泰勒多項(xiàng)式6相比,設(shè)置系數(shù)的微小變化可能會(huì)明顯提高極小極大值的精度。為了實(shí)現(xiàn)精度與速度的最佳平衡,這個(gè)正弦近似值函數(shù)的角輸入范圍應(yīng)該縮小到[–π/2至+π/2]區(qū)間內(nèi),且軟件程序包含一個(gè)有效的范圍縮減濾波器,約占總“正弦”子程序執(zhí)行時(shí)間的30%。

圖3.不同于泰勒-麥克勞林方法圍繞0進(jìn)行定義,極小極大正弦逼近方法在[–π/2至+π/2]區(qū)間內(nèi),會(huì)最小化和均衡最大相對(duì)誤差。

雖然所有計(jì)算都可以使用32位定點(diǎn)算法執(zhí)行,但多年以來,最常見和最方便的數(shù)學(xué)計(jì)算格式是IEEE 754浮點(diǎn)標(biāo)準(zhǔn),特別是在處理長(zhǎng)數(shù)字時(shí)。作為一家DSP VLSI芯片制造商,ADI公司從一開始就率先采用了IEEE 754-1985標(biāo)準(zhǔn)。當(dāng)時(shí)還沒有單芯片浮點(diǎn)DSP處理器,只有簡(jiǎn)單的浮點(diǎn)乘法器和ALU計(jì)算IC,如ADSP-3212和ADSP-3222。這種格式取代了計(jì)算機(jī)行業(yè)的大多數(shù)專有格式,成為所有SHARC DSP處理器的本機(jī)格式,采用單精度32位、擴(kuò)展精度40位,以及最近出現(xiàn)的適用于ADSP-SC589 和ADSP-SC573的雙重精度64位。

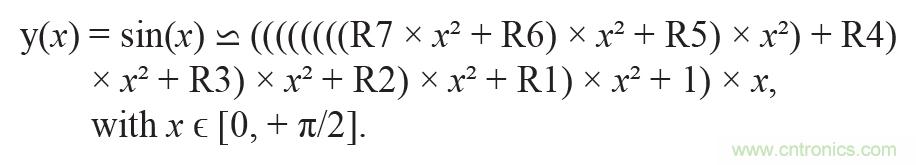

具備32位尾數(shù)的SHARC 40位擴(kuò)展單精度浮點(diǎn)格式為這種正弦波生成應(yīng)用提供了足夠的精度(u 2–32),且有助于保持均等,Cody和Waite表示第15階多項(xiàng)式的總體近似精度為32位,在[0至+π/2]輸入域內(nèi)具有均勻分布的誤差。為了最大限度減少運(yùn)算次數(shù)并保持精度,最后的調(diào)整是對(duì)多項(xiàng)式計(jì)算執(zhí)行霍納法則,這是一種快速求冪的方法,可以求取一個(gè)點(diǎn)的多項(xiàng)式值,所以:

R1至R7是多項(xiàng)式級(jí)數(shù)的Cody和Waite系數(shù),只需要進(jìn)行8次乘法和7次加法即可計(jì)算任何輸入?yún)?shù)ε[0, π/2]的正弦函數(shù)值。以匯編子程序的形式編寫的完整sin(x)近似代碼在SHARC處理器上大約執(zhí)行22個(gè)核心周期。原有的匯編子程序在更改之后,在獲取40位多項(xiàng)式浮點(diǎn)系數(shù)時(shí)執(zhí)行同步雙存儲(chǔ)器訪問,以減少6個(gè)周期。

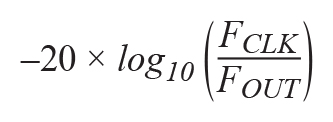

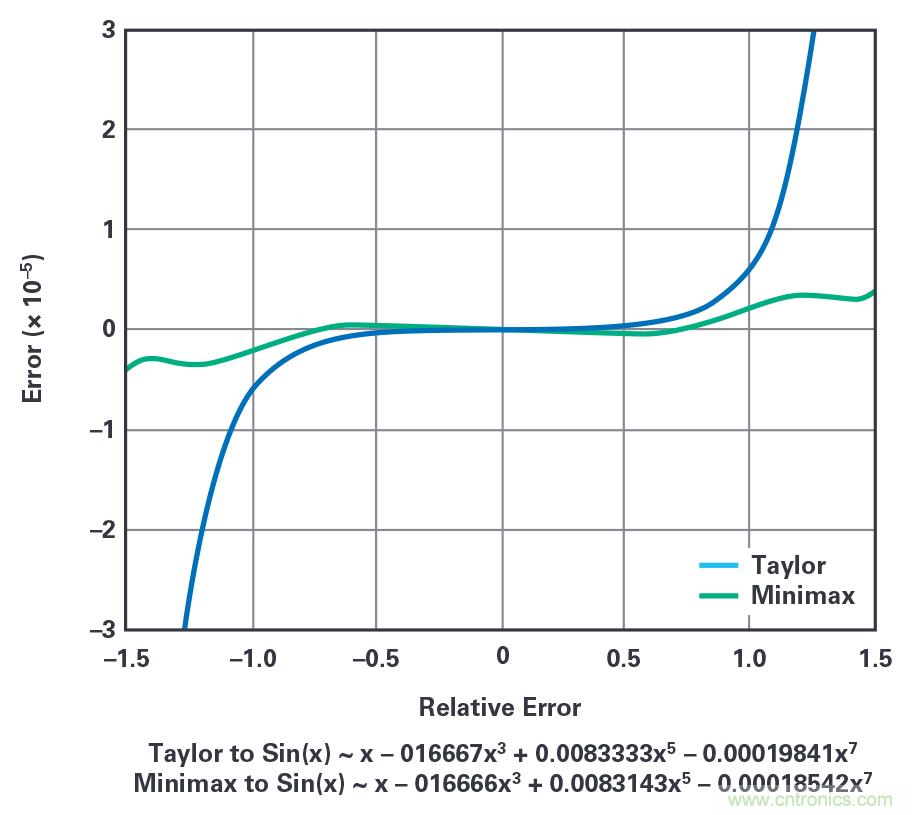

圖4.軟件DDS簡(jiǎn)化框圖給出了處理單元之間的各種量化步驟的數(shù)據(jù)運(yùn)算格式和位置。

NCO 64位相位累加器本身在執(zhí)行時(shí),就用到了雙精度2的小數(shù)格式的SHARC 32位ALU。提供存儲(chǔ)器更新的整個(gè)相位累加器執(zhí)行過程需要11個(gè)核心周期,因此,每個(gè)NCO輸出樣本都在約33個(gè)核心周期內(nèi)生成。

圖4中的框圖顯示了基于軟件DSP的NCO的功能模塊實(shí)現(xiàn)方案,每級(jí)都參考了運(yùn)算格式精度。此外,進(jìn)行信號(hào)模擬重構(gòu)以及實(shí)現(xiàn)完整的DDFS還需要用到一個(gè)或兩個(gè)DAC及其模擬抗混疊濾波器電路。處理鏈的關(guān)鍵元件包括:

u 64位相位累加器(SHARC ALU雙精度,帶溢出);

u 64位小數(shù)定點(diǎn)到40位浮點(diǎn)轉(zhuǎn)換模塊;

u 范圍縮減模塊[0至+ π/2]和象限選擇(Cody和Waite);

u 正弦逼近算法(Hart),用于相位-幅度轉(zhuǎn)換;

u –1.0至+1.0范圍內(nèi)的sin(x)重構(gòu)和歸一化級(jí);

u LP FIR濾波器和sin(x)/x補(bǔ)償(如果必要);

u 以及40位浮點(diǎn)至D位定點(diǎn)轉(zhuǎn)換和標(biāo)度函數(shù),以匹配DAC數(shù)字輸入。

可以在NCO輸出端放置一個(gè)可選的數(shù)字低通濾波器,以去除可能進(jìn)入目標(biāo)頻段的雜散和噪聲。或者,該濾波器可以提供插值和/或逆sin(x)/x頻率響應(yīng)補(bǔ)償,具體由選擇用于模擬重構(gòu)的DAC決定。這種低通FIR濾波器可以使用MATLAB Filter Designer工具設(shè)計(jì)。例如,假設(shè)采樣頻率為48 kSPS,帶寬為DC至20 kHz,帶內(nèi)紋波為0.0001 dB,帶外衰減為-150 dB,則可以實(shí)施具有40位浮點(diǎn)系數(shù)的高質(zhì)量均衡紋波濾波器。它只有99個(gè)濾波系數(shù),在單指令單數(shù)據(jù)(SISD)單計(jì)算單元模式下,總執(zhí)行時(shí)間將消耗約120個(gè)SHARC核心周期。經(jīng)過數(shù)字濾波后,使用其中一個(gè)DSP同步串行端口,由DMA將計(jì)算的樣本對(duì)發(fā)送至DAC。為了獲得更好的速度性能,鏈接DMA操作也可以使用大型乒乓存儲(chǔ)器緩沖區(qū)來支持塊處理操作。例如,塊數(shù)據(jù)大小可以等于FIR數(shù)據(jù)延遲線的長(zhǎng)度。

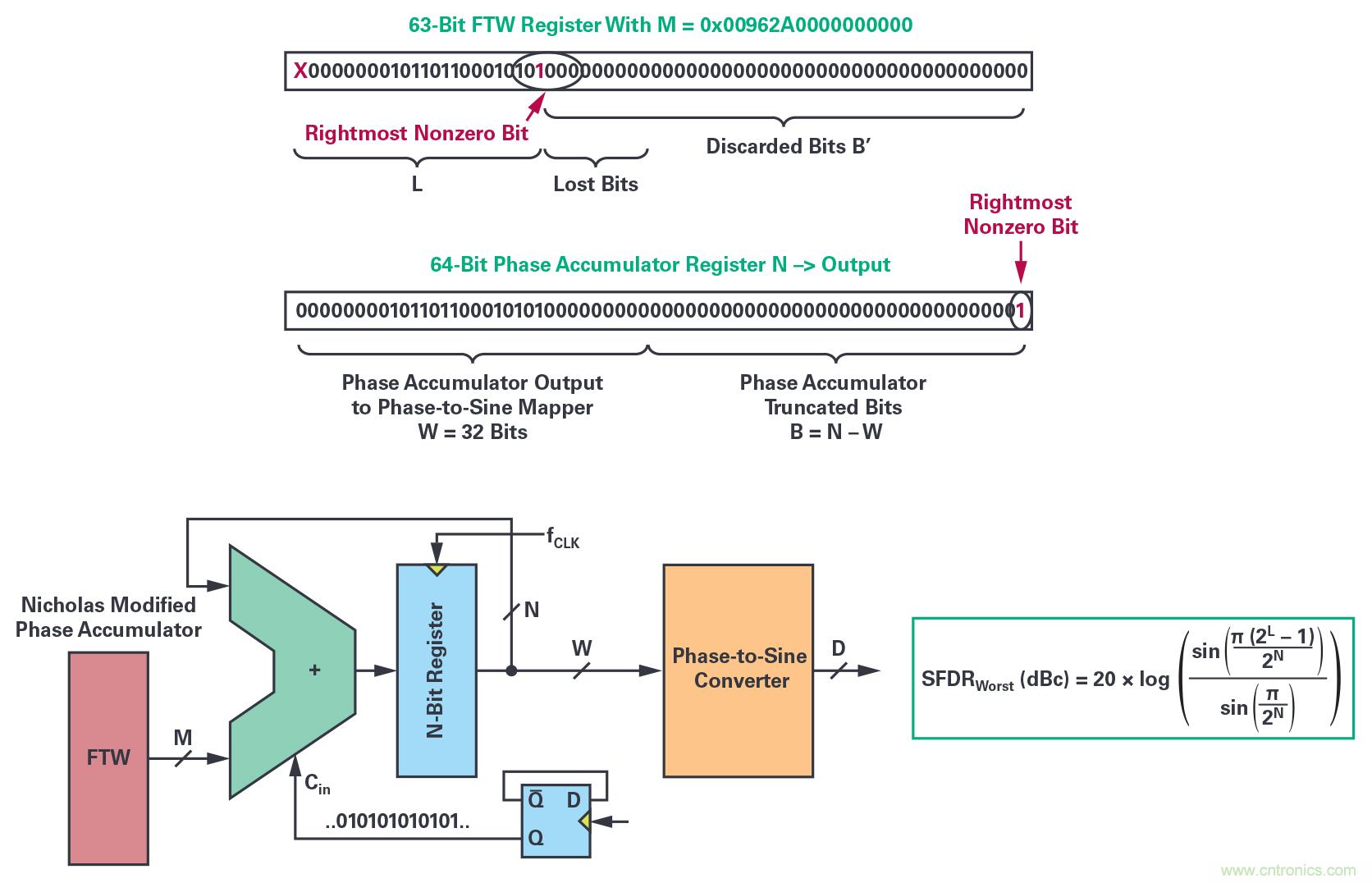

為了實(shí)現(xiàn)最佳SFDR,在NCO上進(jìn)行的最后調(diào)整

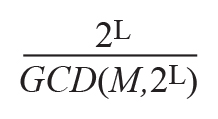

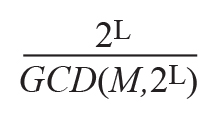

如前所述,NCO遭受雜散的主要原因是對(duì)相位累加器輸出的截?cái)?,其次是針?duì)通過計(jì)算或列表得出的正弦值的幅度量化。相位截?cái)嘁鸬恼`差通過相位調(diào)制(鋸齒形)在載波頻率附近產(chǎn)生雜散,而正弦幅度量化引起與諧波相關(guān)的雜散,不過長(zhǎng)期以來一直被認(rèn)為是隨機(jī)誤差和噪聲。如今,在Henry T. Nicholas和H. Samueli撰寫的技術(shù)論文7中,從數(shù)學(xué)角度深入闡述了相位累加器的操作。在深入分析的基礎(chǔ)上,提出了一種模型,將相位累加器視為分立式相位樣本排列生成器,并據(jù)此預(yù)測(cè)頻率雜散。無論相位累加器參數(shù)(M、N、W)是多少,相序的長(zhǎng)度都等于

(其中GCD是最大公約數(shù)),如圖4所示,由頻率調(diào)諧字M最右邊的位位置L決定。因此,L的值定義序列類別,這些類別彼此共享自己的相位分量集,但根據(jù)

比率重新排序。這些在時(shí)域內(nèi)生成的截?cái)嘞辔粯颖拘蛄斜挥脕硗ㄟ^DFT確定頻率域內(nèi)各雜散線各自的位置和大小。這些序列還表明,M (FTW)的奇數(shù)值顯示最低頻率雜散的幅度,并建議對(duì)相位累加器進(jìn)行簡(jiǎn)單的修改以滿足這些最低程度的條件(只需在FTW中添加1 LSB)。如此,相位累加器的輸出序列必須始終具有相同的2N個(gè)相位元素,無論相位累加器的M值和初始內(nèi)容是什么。之后,最差的雜散信號(hào)音幅度等級(jí)降低3.922 dB,等于SFDR_min (dBc) = 6.02 × W。由Nicholas更改的相位累加器為NCO提供了多種優(yōu)勢(shì),首先,它消除了FTW最右邊的位非常接近MSB(FMCW應(yīng)用中的頻率掃描)的情況,其次,它讓雜散幅度與頻率調(diào)諧字M無關(guān)。這種修改可以通過按采樣速率fS切換ALU LSB來輕松實(shí)現(xiàn),如果FTW LSB置位至邏輯1,則可以仿真與相位累加器相同的行為。相位累加器大小N = 64位時(shí),對(duì)于所需頻率FOUT的精度,可以將½ LSB偏移視為可忽略的誤差。

圖5.FTW最右邊非零位的位置確定了理論上SFDR的最差水平。由Nicholas修改的相位累加器解決了采用任何N值的問題,并且使NCO的SFDR最大。

采用32位輸出相位字W時(shí),由相位截?cái)鄬?dǎo)致的最大雜散幅度會(huì)限制為–192 dBc!正弦采樣值的有限量化也會(huì)導(dǎo)致產(chǎn)生另一組頻率雜散,該雜散通常被認(rèn)為是噪聲,可采用大家熟知的SNRq(dB) = 6.02 × D + 1.76公式進(jìn)行估算。這必須添加到寄生參數(shù)中,因?yàn)橄辔?正弦幅度轉(zhuǎn)換算法階段的近似誤差被認(rèn)為是可以忽略的,但是,必須非常謹(jǐn)慎地選擇相位-正弦近似算法和計(jì)算精度。

這些結(jié)果表明,從理論水平上,我們的軟件正弦NCO的線性和噪聲都遠(yuǎn)遠(yuǎn)超過了測(cè)試市場(chǎng)上大多數(shù)高精度ADC所需的閾值。它仍然需要找到信號(hào)鏈中最后一個(gè)、也是最關(guān)鍵的元件:重構(gòu)DAC及其互補(bǔ)模擬抗混疊濾波器和相關(guān)的驅(qū)動(dòng)電路,以滿足預(yù)期的性能水平要求。

重構(gòu)DAC:關(guān)鍵之處!

首先可能會(huì)選擇具備出色的非線性誤差(INL和DNL)規(guī)格的高精度DAC,例如出色的20位高精度DACAD5791。但是它的分辨率只有20位,而且其R-2R結(jié)構(gòu)不支持實(shí)施信號(hào)重構(gòu),特別是產(chǎn)生非常純的正弦曲線,這是因?yàn)樵谳斎氪a轉(zhuǎn)換期間,它存在很大毛刺。傳統(tǒng)的DAC架構(gòu)基于二進(jìn)制加權(quán)電流發(fā)生器或電阻網(wǎng)絡(luò)構(gòu)建,對(duì)數(shù)字直通和數(shù)字開關(guān)損傷(例如外部或內(nèi)部時(shí)序擺動(dòng)),以及數(shù)字輸入位的其他開關(guān)不對(duì)稱非常敏感,特別是在會(huì)導(dǎo)致能量變化的重大轉(zhuǎn)變期間。這就產(chǎn)生了與代碼相關(guān)的瞬態(tài),從而產(chǎn)生高幅度諧波雜散。

在20位以上的分辨率下,使用外部超線性快速采樣和保持放大器對(duì)DAC輸出去毛刺并無太大幫助,這是因?yàn)樗趲资甃SB下會(huì)生成自己的瞬態(tài),且會(huì)因?yàn)橹夭蓸赢a(chǎn)生組延遲非線性。信號(hào)重構(gòu)主要存在于通信應(yīng)用,通過使用分段架構(gòu)(混合適用于MSB的完全解碼部分和適用于最低有效位的二進(jìn)制加權(quán)元件)來解決毛刺問題。遺憾的是,目前還沒有超過16位精度的商用DAC。與NCO完全可預(yù)測(cè)的行為不同,DAC誤差難以預(yù)測(cè)和準(zhǔn)確仿真,尤其是當(dāng)制造商的動(dòng)態(tài)規(guī)格很小或者不存在時(shí),但專用于音頻應(yīng)用的DAC或ADC除外。插值過采樣和多位∑-? DAC似乎是唯一的解決方案。這些先進(jìn)的轉(zhuǎn)換器具有高達(dá)32位的分辨率、超低失真和高信噪比,是在中低帶寬內(nèi)實(shí)施信號(hào)重構(gòu)的最佳選擇。為了在音頻頻譜或稍寬的頻段(20 kHz或40 kHz帶寬)內(nèi)實(shí)現(xiàn)出色的噪聲和失真性能,可以使用ADI公司產(chǎn)品系列中杰出的∑-? DAC產(chǎn)品,音頻立體聲DACAD1955,雖然分辨率最高為24位,這款DAC仍然是市場(chǎng)上非常受歡迎的音頻DAC。

這款音頻DAC于2004年推出,基于多位Σ-Δ調(diào)制器和過采樣技術(shù),配合各種技巧,用于緩解這種轉(zhuǎn)換本身固有的失真和其他問題。8

即使目前,AD1955采用的插值LP FIR濾波器仍然是同類出色產(chǎn)品。它具有極高的阻帶衰減(≈–120 dB)和極低的帶內(nèi)波紋(≈±0.0001 dB)。它的兩個(gè)(左側(cè)和右側(cè)通道)DAC可以以最高200 kSPS速度運(yùn)行,但在48 kSPS和96 kSPS時(shí)實(shí)現(xiàn)最佳交流性能,其動(dòng)態(tài)范圍以及立體聲模式下的SNR,都支持典型的EIAJ標(biāo)準(zhǔn)、A加權(quán)120 dB系數(shù)。在單聲道模式下,兩個(gè)通道同時(shí)異相組合,性能有望提高3 dB。但是,對(duì)于寬帶應(yīng)用,這些規(guī)格不太實(shí)際,這是因?yàn)樗鼈兪呛铣傻?,帶寬范圍?0 Hz至20 kHz之間。帶外噪聲和雜散不會(huì)超過20 kHz,部分是因?yàn)镋IAJ標(biāo)準(zhǔn)、A加權(quán)濾波器和音頻行業(yè)規(guī)格定義。這種滿足特定音頻測(cè)量要求的帶通濾波器模擬人耳的頻率響應(yīng),與未濾波的測(cè)量值相比,性能提高3 dB。

DDFS硬件演示平臺(tái):采用AD1955實(shí)現(xiàn)正弦波重構(gòu)

整套DDFS使用兩個(gè)評(píng)估板實(shí)現(xiàn),一個(gè)支持DSP處理器,一個(gè)適用于采用AD1955 DAC進(jìn)行模擬信號(hào)重構(gòu)。選擇第2代SHARC ADSP-21161N評(píng)估板的原因在于其可用性、易用性,以及適合任何音頻應(yīng)用的精簡(jiǎn)配置。目前仍在量產(chǎn)的ADSP-21161N于不久之前設(shè)計(jì),支持工業(yè)高端消費(fèi)電子和專業(yè)音頻應(yīng)用,提供高達(dá)110 Mips和660 MFlops,或220 MMACS/s容量。與最新一代的SHARC處理器相比,ADSP-21161N最大的不同在于它采用較短的3級(jí)指令管道、一個(gè)片內(nèi)1 Mb三端口RAM,以及數(shù)量更少的外設(shè)。精準(zhǔn)信號(hào)音生成器的最后和最關(guān)鍵的級(jí)基于AD1955評(píng)估板,該板必須從軟件NCO提供的樣本中,以完全還原的方式重構(gòu)模擬信號(hào)。這個(gè)評(píng)估板帶有一個(gè)抗混疊濾波器(AAF),優(yōu)化音頻帶寬來滿足Nyquist標(biāo)準(zhǔn),除了常用的S/PDIF或AES-EBU接收器外,還配有兩個(gè)串行音頻接口,用于支持PCM/I2S和DSD數(shù)字流。PCM/I2S串行鏈路連接器用于將AD1955 DAC板連接到ADSP-21161N EVB的串行端口1和3連接器(J)。這兩個(gè)板都可以配置為采用I2S PCM或DSP模式,以48 kSPS、96 kSPS或192 kSPS采樣速率運(yùn)行。DSP串行端口1生成左右通道數(shù)據(jù)、字選擇或左/右?guī)?,以及雙頻DAC的數(shù)字輸入接口所需的SCK位時(shí)鐘信號(hào)。串行端口3僅用于生成運(yùn)行DAC內(nèi)插濾波器和Σ-Δ調(diào)制器所需的DAC主時(shí)鐘MCLK,調(diào)制器以比輸入采樣頻率(48 kSPS)快256倍(默認(rèn))的速度運(yùn)行。由于所有DAC時(shí)鐘信號(hào)都由DSP生成,所以使用Crystek提供的超低噪聲振蕩器CCHD-957替代了板原有的低成本愛普生時(shí)鐘振蕩器。其相位噪聲在1 kHz下可能低至–148 dB/Hz,適用于24.576 MHz輸出頻率。

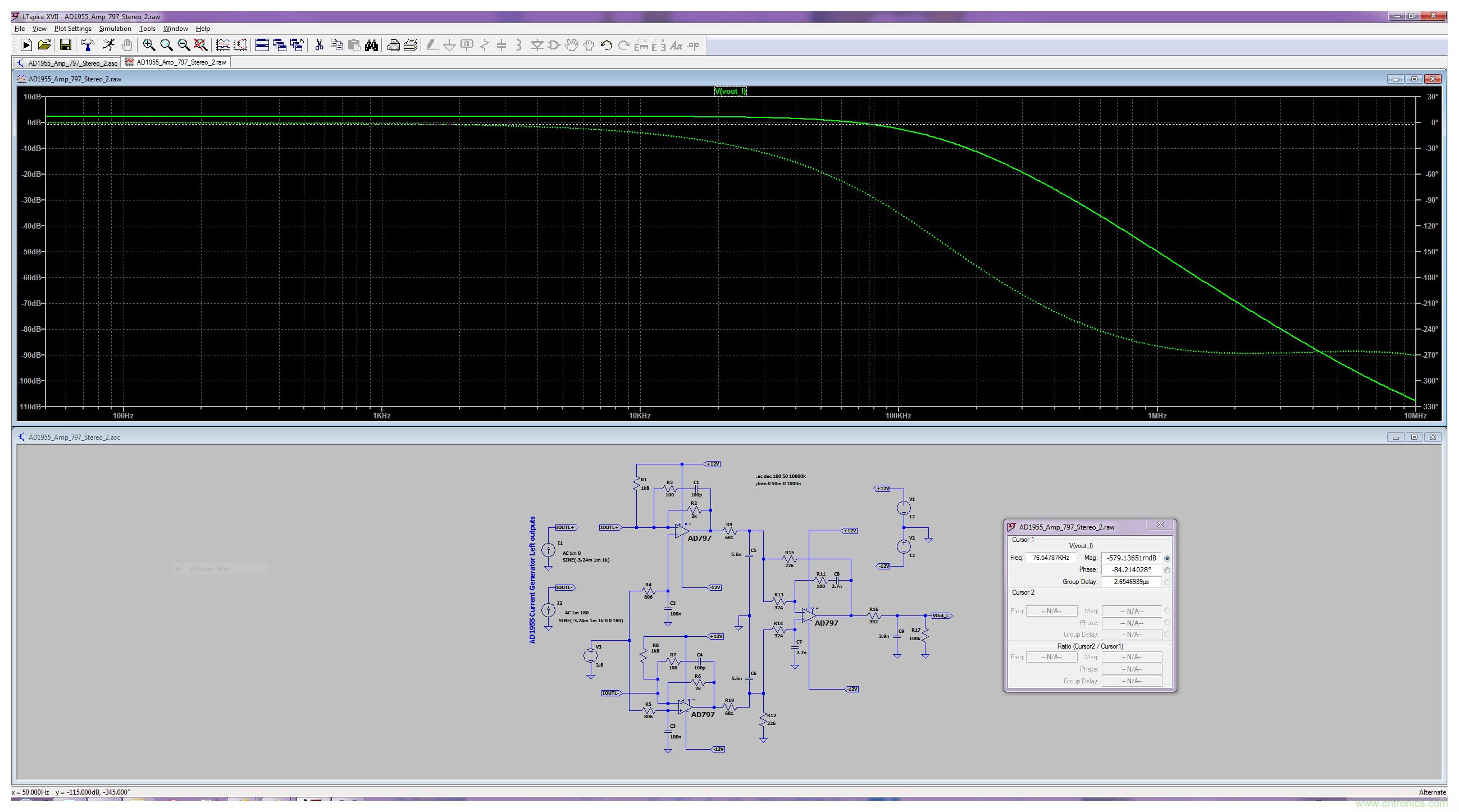

在模擬輸出端,有源I/V轉(zhuǎn)換器必須用于在恒共模電壓下(通常為2.8 V)保持AD1955電流差分輸出,以最大限度減少失真。像AD797 這樣的超低失真和超低噪聲的高精度運(yùn)算放大器能夠滿足此需求,還可用于處理模擬信號(hào)重構(gòu)。由于兩個(gè)差分輸出由DSP分別處理,因此選擇了具有AAF拓?fù)浣Y(jié)構(gòu)的立體聲輸出配置,而不是單聲道模式。這個(gè)AAF使用LTspice® XVII進(jìn)行仿真,結(jié)果如圖6所示。由于濾波器的最后一部分是無源的,所以應(yīng)該像最近推出的ADA4945那樣增加一個(gè)有源差分緩沖級(jí)。這種具備低噪聲、超低失真、快速建立時(shí)間特性的全差分放大器是近乎完美的驅(qū)動(dòng)任何高分辨率SAR和Σ-Δ ADC的DAC配件。ADA4945具有相對(duì)較大的共模輸出電壓范圍和出色的直流特性,可以提供出色的輸出平衡,有助于抑制偶數(shù)階諧波失真產(chǎn)品。

EVB三階濾波器的–3 dB截止頻率為76 kHz,在500 kHz下僅衰減–31 db。這款低通濾波器具備出色的帶內(nèi)平坦性,但帶外衰減必須大幅改善,即使是限于純粹的重構(gòu)音頻應(yīng)用。要抑制DAC成型噪聲和調(diào)制器時(shí)鐘頻率MCLK,就必須滿足這一點(diǎn)。根據(jù)軟件DDS的具體使用,用于單信號(hào)音生成器或任意波形生成器(生成復(fù)雜波形時(shí)為AWG),必須優(yōu)化AAF,以解決帶外衰減或群延遲失真。以大家熟悉的SRS DS360超低失真函數(shù)生成器為例進(jìn)行比較,采用7階Cauer AAF可達(dá)到類似的采樣速率。信號(hào)重構(gòu)由AD1862完成,后者是一款串行輸入20位分段R-2R DAC,適用于數(shù)字音頻應(yīng)用。AD1862在高達(dá)768 kHz (×16 fS)頻率下可以保持20位字采樣速率,且具備出色的噪聲和線性度。它支持單端電流輸出,所以能夠使用最出色的放大器來實(shí)施外部I-V轉(zhuǎn)換。

圖6.LTspice仿真AD1955 EVB三階抗混疊濾波器(立體聲配置)的頻率響應(yīng)。

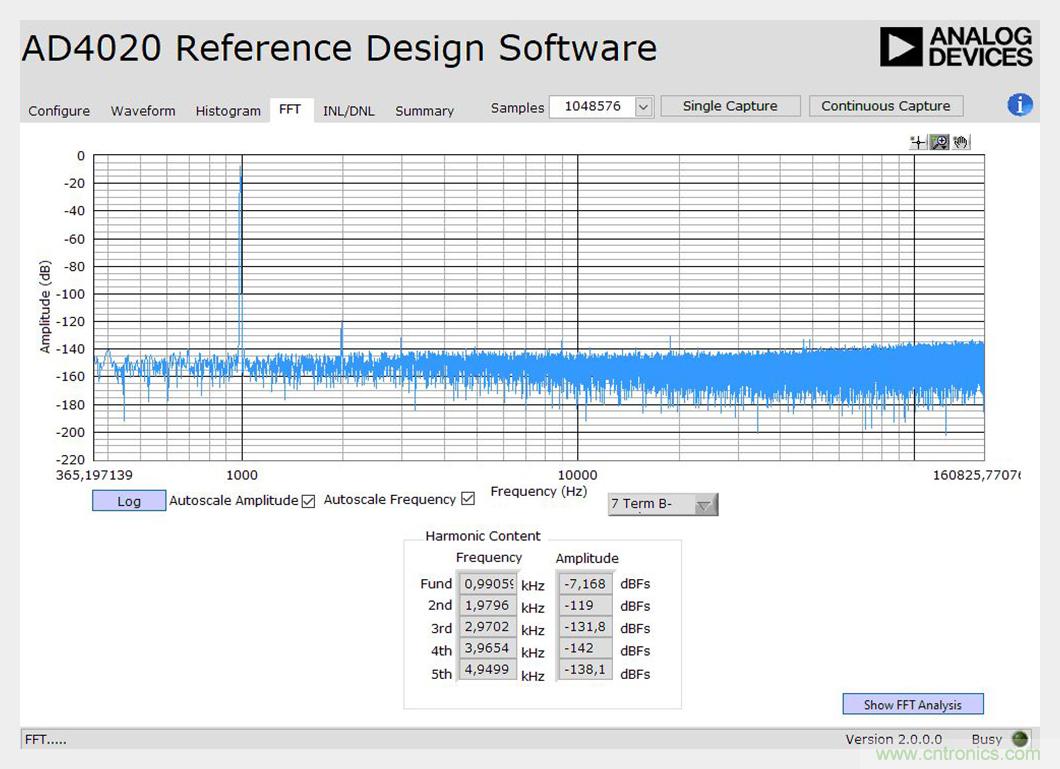

AD1955和SHARC DSP組合針對(duì)多種高分辨率SAR ADC實(shí)施測(cè)試,例如AD4020,其中未設(shè)置外部可選無源濾波器。默認(rèn)情況下,基礎(chǔ)AD4020評(píng)估板除了板載ADA4807驅(qū)動(dòng)器之外,并無其他選項(xiàng)可用。用于在V_REF/2共模電壓下偏置ADC輸入的簡(jiǎn)單電路提供相當(dāng)?shù)偷?00 Ω輸入阻抗,需要使用信號(hào)隔離、交流耦合,或使用外部差分放大器模塊,例如EVAL-ADA4945-1。電路筆記CN-0513中描述的AD4020參考設(shè)計(jì)板就是一項(xiàng)不錯(cuò)的選擇。它包含一個(gè)分立式可編程增益儀表放大器(PGIA),提供高輸入阻抗,支持±5 V差分輸入信號(hào)(G = 1)。雖然這些AD4020板和它們的SDP-H1控制器不支持相干采樣采集,但它們具備出色的樣本波形捕捉長(zhǎng)度,最高可達(dá)1M。因此,可以實(shí)現(xiàn)具備可選窗口的FFT,提供出色的頻率分辨率和低本底噪聲。例如,對(duì)于7項(xiàng)Blackman-Harris窗口,圖7中所示的1 Mpts FFT圖描述了AD1955在生成的990.059 Hz正弦波下的失真水平。二次諧波是350 kHz帶寬內(nèi)–111.8 dBc下的最大失真分量和最大雜散。但是,在考慮整個(gè)806 kHz ADC Nyquist帶寬時(shí),SFDR受∑-? DAC調(diào)制器、內(nèi)插濾波器頻率和其二次諧波(384 kHz和768 kHz)限制。

圖7.從1 M點(diǎn)FFT分析中可以看出,在低于–111 dBc下具備不錯(cuò)的失真性能,在1 kHz輸入頻率下,10 kHz至200 kHz頻段內(nèi)出現(xiàn)最大雜散。本底噪聲約為–146 dBFS。

在相同條件下,對(duì)傳統(tǒng)的AD1862進(jìn)行測(cè)試,結(jié)果顯示頻率行為略微不同。在差分配置下,兩個(gè)20位DAC的時(shí)鐘速度約為500 kSPS,在1.130566 kHz下,本底噪聲為–151 dBFS,正弦輸出水平為12 V p-p時(shí)的THD為–104.5 dB。在AD4020 Nyquist帶寬(806 kHz)下,SFDR接近106 dB,受三階諧波限制。DAC重構(gòu)濾波器基于兩個(gè)AD743低噪聲FET放大器,與AD1955評(píng)估板中的濾波器一樣,屬于三階濾波器,但是-3 dB時(shí)的截止頻率為35 kHz。

為了變得有效,基于DDS的生成器需要采用不錯(cuò)的濾波器,支持在約250 kHz下實(shí)現(xiàn)大于100 dB衰減,以生成達(dá)到25 kHz CW信號(hào)頻率范圍的直流。這可以使用六階切比雪夫?yàn)V波器實(shí)現(xiàn),甚至使用用于顯示出色帶內(nèi)平坦度的六階巴特沃茲低通濾波器實(shí)現(xiàn)。濾波器階將被最小化,以限制模擬級(jí)的數(shù)量和問題點(diǎn),例如噪聲和失真。

結(jié)論

在標(biāo)準(zhǔn)評(píng)估板上實(shí)施的初級(jí)和開箱即用測(cè)試顯示,用于傳統(tǒng)正弦波CW生成的基于處理器的DDS技術(shù)要實(shí)現(xiàn)高性能指日可待。通過精心設(shè)計(jì)重構(gòu)濾波器和模擬輸出緩沖級(jí),可以實(shí)現(xiàn)–120 dBc諧波失真系數(shù)?;贒SP的NCO/DDS不只受到單信號(hào)音正弦波生成限制。通過使用具備合適的截止頻率,且無其他硬件變更的優(yōu)化AAF(貝塞爾或巴特沃茲),同樣的DSP和DAC組合可用作高性能AWG來生成任何類型的波形,例如,完全合成可設(shè)置參數(shù)的多信號(hào)音正弦波(可以完全控制每個(gè)分量的相位和幅度)來實(shí)施IMD測(cè)試。

由于浮點(diǎn)算法對(duì)于要求高精度和/或高動(dòng)態(tài)范圍的應(yīng)用至關(guān)重要,如今,低成本ADSP-21571或SoCADSP-SC571(ARM®和SHARC)等SHARC+ DSP處理器實(shí)際上是業(yè)界的實(shí)時(shí)處理標(biāo)準(zhǔn),支持最高10 MSPS的合計(jì)采樣速率。雙SHARC內(nèi)核和其硬件加速度計(jì)采用500 MHz時(shí)鐘頻率,可以提供高于5 Gflops的計(jì)算性能和數(shù)十個(gè)內(nèi)部專用SRAM,后者是生成各種波形,以及實(shí)施復(fù)雜的分析處理需要的基本組成部分。此類應(yīng)用表明,在實(shí)施精準(zhǔn)的數(shù)字信號(hào)處理時(shí),并非一定要系統(tǒng)性地使用硬件可編程解決方案。得益于ADI公司的CCES、VDSP++ C和C++編譯器,以及全套仿真器和實(shí)時(shí)調(diào)試器,浮點(diǎn)處理器及其整個(gè)開發(fā)環(huán)境可以快速輕松地從仿真器(例如MATLAB)移植代碼,以及快速實(shí)施調(diào)試。

參考文獻(xiàn)

1. Joseph A. Webb。美國專利US3654450,1970年4月。

2. Joseph Tierney、Charles M. Rader、Bernard Gold。“數(shù)字頻率合成器。”IEEE 音頻和電聲學(xué)論文集,第19卷第1期,1971年3月。

3. Jim Williams、Guy Hoover。AN-132:用于驗(yàn)證純度的A→D轉(zhuǎn)換器保真度測(cè)試。ADI公司,2011年2月。

4. John F. Hart。計(jì)算機(jī)逼近算法。Krieger出版公司,1978年。

5. William J. Cody、William Waite。初等函數(shù)軟件手冊(cè)。Prentice-Hall, Inc.,1980年。

6. Robin Green。“更快的數(shù)學(xué)函數(shù),第2部分介紹。”Sony Computer Entertainment America,2016年5月。

7. Henry T. Nicholas、Henry Samueli。“存在相位累加器截?cái)鄷r(shí)的直接數(shù)字頻率合成器的輸出頻譜分析。”IEEE,1987年5月。

8. Robert Adams、Khiem Nguyen、Karl Sweetland。“支持分段噪聲擾碼的113 dB SNR過采樣DAC。”IEEE,1998年2月。

ADSP-21000系列應(yīng)用手冊(cè),第1卷。ADI公司,1994年5月。

數(shù)字信號(hào)合成技術(shù)教程。ADI公司,2001年3月。

Butler, Oscar。“2017年夏季實(shí)習(xí)報(bào)告:高精度過采樣20位超低功率采集系統(tǒng)。”(ADI公司,2017年)

Crawford, James A. Advanced Phase-Lock Applications: FrequencySynthesis. AMI, LLC, May 2011.

Crawford, James A。高級(jí)鎖相應(yīng)用:頻率合成。AMI, LLC,2011年5月。

評(píng)估板用戶指南UG-048。ADI公司,2010年2月。EV-4020-REF-DGNZ參考設(shè)計(jì)板用戶指南UG-1280。

ADI公司,2019年5月。

Goldberg, Bar-Giora。頻率合成數(shù)字技術(shù)。McGraw-Hill,1995年8月。

Ds360型超低失真函數(shù)發(fā)生器。Stanford Research Systems,1999年。

Symons, Pete。數(shù)字波形生成。劍橋大學(xué)出版社,2013年11月。

AD1862數(shù)據(jù)手冊(cè)。ADI公司,2011年7月。

1241-2010 - 模數(shù)轉(zhuǎn)換器術(shù)語和測(cè)試方法的IEEE標(biāo)準(zhǔn)。IEEE,2011年1月。

作者簡(jiǎn)介

Patrick Butler是ADI公司南歐銷售集團(tuán)的一名現(xiàn)場(chǎng)應(yīng)用工程師,為法國全球市場(chǎng)和部分ADEF客戶提供支持。從1984年至今,他一直在ADI公司工作,主要負(fù)責(zé)DSP構(gòu)建模塊IC以及高速轉(zhuǎn)換器的開發(fā)。在此以前,他在法國圣艾蒂安斯倫貝謝公司ATE部門工作了5年,任設(shè)計(jì)工程師,之后法國南特Matra-MHS、AMD和Harris SC-Intersil擔(dān)任多個(gè)應(yīng)用工程師和FAE職位。如今,他的主要愛好是收集老式音響組件,在兩個(gè)兒子的幫助下,動(dòng)手制作高效的有源喇叭揚(yáng)聲器系統(tǒng)。

[HJ1]相位截?cái)?/div>

[HJ2]功耗

[HJ3]基于

(來源:ADI,作者:Patrick Butler,現(xiàn)場(chǎng)應(yīng)用工程師)

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請(qǐng)電話或者郵箱聯(lián)系小編進(jìn)行侵刪。