【導(dǎo)讀】氮化鎵 (GaN) 晶體管的開關(guān)速度比硅MOSFET快很多,從而有可能實現(xiàn)更低的開關(guān)損耗。然而,當(dāng)壓擺率很高時,特定的封裝類型會限制GaN FET的開關(guān)性能。將GaN FET與驅(qū)動器集成在一個封裝內(nèi)可以減少寄生電感,并且優(yōu)化開關(guān)性能。集成驅(qū)動器還可以實現(xiàn)保護(hù)功能。

簡介

氮化鎵 (GaN) 晶體管的開關(guān)性能要優(yōu)于硅MOSFET,因為在同等導(dǎo)通電阻的情況下,氮化鎵 (GaN) 晶體管的終端電容較低,并避免了體二極管所導(dǎo)致的反向恢復(fù)損耗。正是由于這些特性,GaN FET可以實現(xiàn)更高的開關(guān)頻率,從而在保持合理開關(guān)損耗的同時,提升功率密度和瞬態(tài)性能。

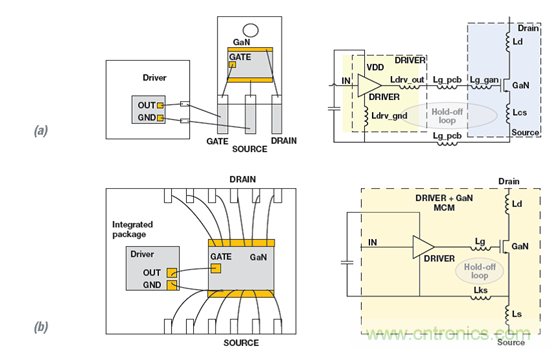

傳統(tǒng)上,GaN器件被封裝為分立式器件,并由單獨的驅(qū)動器驅(qū)動,這是因為GaN器件和驅(qū)動器基于不同的處理技術(shù),并且可能來自不同的廠商。每個封裝將會有引入寄生電感的焊線和引線,如圖1a所示。當(dāng)以每納秒數(shù)十到幾百伏電壓的高壓擺率進(jìn)行切換時,這些寄生電感會導(dǎo)致開關(guān)損耗、振鈴和可靠性問題。

將GaN晶體管與其驅(qū)動器集成在一起(圖1b)可以消除共源電感,并且極大降低驅(qū)動器輸出與GaN柵極之間的電感,以及驅(qū)動器接地中的電感。在這篇文章中,我們將研究由封裝寄生效應(yīng)所引發(fā)的問題和限制。在一個集成封裝內(nèi)對這些寄生效應(yīng)進(jìn)行優(yōu)化可以減少該問題,并且以高于100V/ns的高壓擺率實現(xiàn)出色的開關(guān)性能。

圖1. 由獨立封裝內(nèi)的驅(qū)動器驅(qū)動的GaN器件 (a);一個集成GaN/驅(qū)動器封裝 (b)。

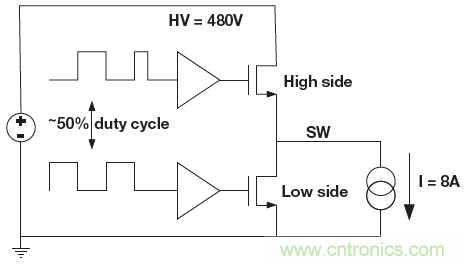

圖2. 用于仿真的半橋電路的簡化圖

仿真設(shè)置

為了仿真寄生電感效應(yīng),我們使用了一個采用直接驅(qū)動配置的空乏型GaN半橋功率級(圖2)。我們將半橋設(shè)置為一個降壓轉(zhuǎn)換器,總線電壓480V,死區(qū)時間50ns時50%占空比(輸出電壓 [VOUT] = 240V),以及一個8A的電感器電流。這個GaN柵極在開關(guān)電壓電平間被直接驅(qū)動。一個阻性驅(qū)動設(shè)定GaN器件的接通壓擺率。一個電流源只會仿真一個與連續(xù)傳導(dǎo)模式降壓轉(zhuǎn)換器內(nèi)開關(guān) (SW) 節(jié)點所連接的電感負(fù)載。

共源電感

高速開關(guān)中最重要的一個寄生要素是共源電感(圖1a中的Lcs),它限制了器件汲取電流的壓擺率。在傳統(tǒng)的TO-220封裝中,GaN源由焊線流至引線,而汲取電流與柵極電流都從這里流過。這個共源電感在汲取電流改變時調(diào)制柵源電壓。共源電感會高于10nH(其中包括焊線和封裝引線),從而限制了壓擺率 (di/dt),并增加開關(guān)損耗。

借助圖1b中所示的集成式封裝,驅(qū)動器接地直接焊接至GaN裸片的源焊墊。這個Kelvin源連接最大限度地縮短了電源環(huán)路與柵極環(huán)路共用的共源電感路徑,從而使得器件能夠以高很多的電流壓擺率來開關(guān)??梢詫⒁粋€Kelvin源引腳添加到一個分立式封裝內(nèi);然而,這個額外的引腳會使其成為一個不標(biāo)準(zhǔn)的電源封裝。Kelvin源引腳還必須從印刷電路板 (PCB) 引回至驅(qū)動器封裝,從而增加了柵極環(huán)路電感。

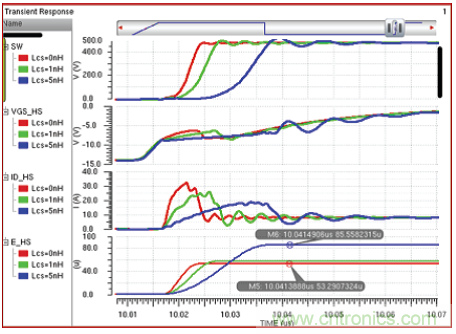

圖3.不同共源電感情況下的高管接通:紅色 = 0nH,綠色 = 1nH,藍(lán)色 = 5nH。E_HS是高管器件的VDS和IDS在運行時間內(nèi)的積分值(能耗)。

圖3顯示的是高管開關(guān)接通時的硬開關(guān)波形。在共源電感為5nH時,由于源降級效應(yīng),壓擺率減半。一個更低的壓擺率會帶來更長的轉(zhuǎn)換時間,導(dǎo)致更高的交叉?zhèn)鲗?dǎo)損耗,如能耗曲線圖中所示。在共源電感為5nH時,能量損耗從53μJ增加至85μJ,增加了60%。假定開關(guān)頻率為100kHz,功率損耗則會從從5.3W增加至8.5W。

柵極環(huán)路電感

柵極環(huán)路電感包括柵極電感和驅(qū)動器接地電感。柵極電感是驅(qū)動器輸出與GaN柵極之間的電感。在使用獨立封裝時,柵極電感包括驅(qū)動器輸出焊線 (Ldrv_out)、GaN柵極焊線 (Lg_gan) 和PCB跡線 (Lg_pcb),如圖1a中所示。

基于不同的封裝尺寸,柵極電感會從緊湊型表面貼裝封裝(例如,四方扁平無引線封裝)的幾納亨到有引線功率封裝(例如TO-220)的10nH以上。如果驅(qū)動器與GaN FET集成在同一個引線框架內(nèi)(圖1b),GaN柵極直接焊接到驅(qū)動器輸出上,這樣可以將柵極電感減少至1nH以下。封裝集成還可以極大地降低驅(qū)動器接地電感(從圖1a中的Ldrv_gnd + Ls_pcb到圖1b中的Lks)。

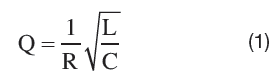

降低柵極環(huán)路電感對于開關(guān)性能有著巨大影響,特別是在關(guān)閉期間,GaN柵極被一個電阻器下拉。這個電阻器的電阻值需要足夠低,這樣的話,器件才不會在開關(guān)期間由于漏極被拉高而又重新接通。這個電阻器與GaN器件的柵源電容和柵極環(huán)路電感組成了一個電感器-電阻器-電容器 (L-R-C) 槽路。方程式1中的Q品質(zhì)因數(shù)表示為:

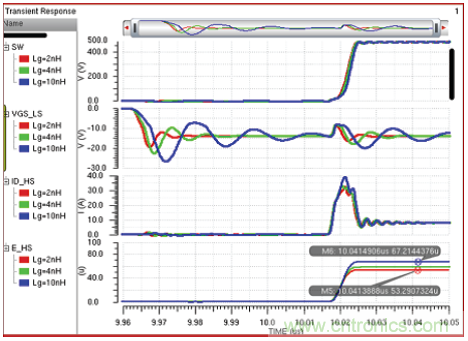

在柵極環(huán)路電感值更大時,Q品質(zhì)因數(shù)增加,振鈴變得更高。這個效應(yīng)用一個1Ω下拉電阻關(guān)閉低管GaN FET進(jìn)行仿真,圖4中這個效應(yīng)的出現(xiàn)時間為9.97μs,其中柵極環(huán)路電感變化范圍介于2nH到10nH之間。在10nH的情況下,低管VGS在負(fù)柵極偏置以下產(chǎn)生12V振鈴。這就極大地增加了GaN晶體管柵極的應(yīng)力。需要注意的一點是,任何FET的柵極上的過應(yīng)力都會對可靠性產(chǎn)生負(fù)面影響。

柵極環(huán)路電感還會對關(guān)斷保持能力產(chǎn)生巨大影響。當(dāng)?shù)凸芷骷臇艠O保持在關(guān)閉電壓時,并且高管器件接通,低管漏極電容將一個大電流傳送到柵極的保持環(huán)路中。這電流通過柵極環(huán)路電感將柵極推上去。圖4在大約10.02µs時的曲線變化便是說明了這一點。隨著電感增加,低管VGS被推得更高,從而增加了直通電流,這一點在高管漏電流曲線圖中可見 (ID_HS)。這個直通電流使得交叉?zhèn)鲗?dǎo)能量損耗 (E_HS) 從53µJ增加至67µJ。

圖4. 不同柵極環(huán)路電感下的低管關(guān)閉和高管接通波形:紅色 = 2nH,綠色 = 4nH,藍(lán)色 = 10nH。E_HS是高管能耗。

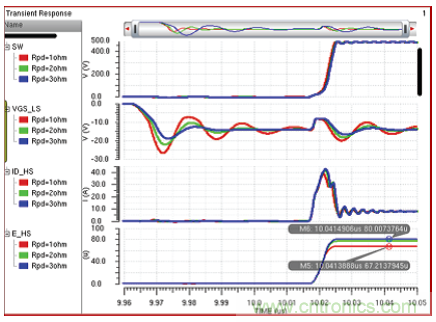

根據(jù)方程式 (1),減輕柵極應(yīng)力的一個方法就是增加下拉電阻值,反過來減少L-R-C槽路的Q品質(zhì)因數(shù)。圖5顯示的是用一個10nH柵極環(huán)路電感和在1Ω到3Ω之間變化的下拉電阻 (Rpd) 進(jìn)行的仿真結(jié)果。雖然柵極下沖被一個3Ω下拉電阻限制在負(fù)偏置電壓以下的數(shù)伏特內(nèi),但是關(guān)斷保持能力惡化,從而導(dǎo)致更大的直通電流。這一點在漏電流曲線圖中很明顯。

E_HS能量曲線圖顯示出,在每個開關(guān)周期內(nèi)有額外的13µJ損耗,與2nH的柵極環(huán)路電感和1Ω下拉電阻時53µJ相比,差不多增加了60%(圖4)。

假定開關(guān)頻率為100kHz,高管器件上的功率損耗從5.3W增加至8W,其原因是由高柵極環(huán)路電感和高下拉電阻值所導(dǎo)致的直通。這個額外的功率損耗會使得功率器件內(nèi)的散熱變得十分難以管理,并且會增加封裝和冷卻成本。

圖5. 使用10nH柵極環(huán)路電感和下拉電阻時的仿真結(jié)果:Rpd = 1Ω(紅色)、2Ω(綠色)和3Ω(藍(lán)色)。E_HS是高管能耗。

為了減輕直通電壓,可以將柵極偏置為更大的負(fù)電壓,不過這樣做會增加?xùn)艠O上的應(yīng)力,并且會在器件處于第三象限時增大死區(qū)時間損耗。因此,在柵極環(huán)路電感比較高時,柵極應(yīng)力與器件關(guān)斷保持能力之間的均衡和取舍很難管理。你必須增加?xùn)艠O應(yīng)力,或者允許半橋直通,這會增加交叉?zhèn)鲗?dǎo)損耗和電流環(huán)路振鈴,并且會導(dǎo)致安全工作區(qū) (SOA) 問題。一個集成式GaN/驅(qū)動器封裝提供低柵極環(huán)路電感,并且最大限度地降低柵極應(yīng)力和直通風(fēng)險。

GaN器件保護(hù)

將驅(qū)動器與GaN晶體管安裝在同一個引線框架內(nèi)可以確保它們的溫度比較接近,這是因為引線框架的導(dǎo)熱性能極佳。熱感測和過熱保護(hù)可以置于驅(qū)動器內(nèi)部,使得當(dāng)感測到的溫度超過保護(hù)限值時,GaN FET將關(guān)閉。

一個串聯(lián)MOSFET或一個并聯(lián)GaN感測FET可以被用來執(zhí)行過流保護(hù)。它們都需要GaN器件與其驅(qū)動器之間具有低電感連接。由于GaN通常以較大的di/dt進(jìn)行極快的開關(guān),互聯(lián)線路中的額外電感會導(dǎo)致振鈴,并且需要較長的消隱時間來防止電流保護(hù)失效。集成驅(qū)動器確保了感測電路與GaN FET之間盡可能少的電感連接,這樣的話,電流保護(hù)電路可以盡可能快的做出反應(yīng),以保護(hù)器件不受過流應(yīng)力的影響。

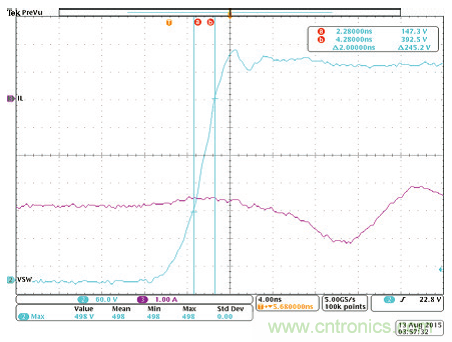

圖6. 一個半橋降壓轉(zhuǎn)換器(通道2)中的高管接通時的SW節(jié)點波形。

開關(guān)波形

圖6是一個半橋的開關(guān)波形;

這個半橋包含2個集成式驅(qū)動器的GaN器件,采用8mm x 8mm四方扁平無引線 (QFN) 封裝。通道2顯示SW節(jié)點,此時高管器件在總線電壓為480V的情況下,以120V/ns的壓擺率被硬開關(guān)。這個經(jīng)優(yōu)化的驅(qū)動器集成式封裝和PCB將過沖限制在50V以下。需要說明的一點是,捕捉波形時使用的是1GHz示波器和探頭。

結(jié)論

GaN晶體管與其驅(qū)動器的封裝集成消除了共源電感,從而實現(xiàn)了高電流壓擺率。它還減少了柵極環(huán)路電感,以盡可能地降低關(guān)閉過程中的柵極應(yīng)力,并且提升器件的關(guān)斷保持能力。集成也使得設(shè)計人員能夠為GaN FET搭建高效的過熱和電流保護(hù)電路。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進(jìn)行處理。

推薦閱讀: