【導(dǎo)讀】電機(jī)在各種工業(yè)����、汽車(chē)和商業(yè)領(lǐng)域應(yīng)用廣泛����。電機(jī)由驅(qū)動(dòng)器控制,驅(qū)動(dòng)器通過(guò)改變輸入功率來(lái)控制其轉(zhuǎn)矩���、速度和位置�。高性能電機(jī)驅(qū)動(dòng)器可以提高效率��,實(shí)現(xiàn)更快速���、更精確的控制。高級(jí)電機(jī)控制系統(tǒng)集控制算法、工業(yè)網(wǎng)絡(luò)和用戶接口于一體�����,因此需要更多處理能力來(lái)實(shí)時(shí)執(zhí)行所有任務(wù)?��,F(xiàn)代電機(jī)控制系統(tǒng)通常利用多芯片架構(gòu)來(lái)實(shí)現(xiàn):數(shù)字信號(hào)處理器(DSP)執(zhí)行電機(jī)控制算法��,F(xiàn)PGA 實(shí)現(xiàn)高速 I/O 和網(wǎng)絡(luò)協(xié)議��,微處理器處理執(zhí)行控制1�。

隨著片上系統(tǒng)(SoC)的出現(xiàn)����,例如集 CPU 的靈活性與 FPGA 的處 理能力于一體的 Xilinx® Zynq All Programmable SoC,設(shè)計(jì)人員終于能夠?qū)㈦姍C(jī)控制功能和其他處理任務(wù)納入單個(gè)器件中��?�?刂扑惴?����、網(wǎng)絡(luò)和其他處理密集型任務(wù)被分流到可編程邏輯��,而管理控制、系統(tǒng)監(jiān)控與診斷���、用戶接口以及調(diào)試則由處理單元處理����?�?删幊踢壿嬁梢园鄠€(gè)并行工作的控制內(nèi)核���,以實(shí)現(xiàn)多軸機(jī)器或多重控制系統(tǒng)����。由于在單芯片上實(shí)現(xiàn)了完整的控制器���,因此硬件設(shè)計(jì)可以更簡(jiǎn)單���、更可靠、更便宜��。

近年來(lái)�����,在 MathWorks®Simulink®等軟件建模與仿真工具的推動(dòng)下��,基于模型的設(shè)計(jì)已發(fā)展成為完整的設(shè)計(jì)流程——從模型創(chuàng)建到實(shí)現(xiàn)2 �����?���;谀P偷脑O(shè)計(jì) 改變了工程師和科學(xué)家的工作方式,把設(shè)計(jì)任務(wù)從實(shí)驗(yàn)室和現(xiàn)場(chǎng)轉(zhuǎn)移到桌面?,F(xiàn)在,包括工廠和控制器在內(nèi)的整個(gè)系統(tǒng)都可以建模�,工程師可以先調(diào)整好控制器的行為,再將其部署到現(xiàn)場(chǎng)���。這樣就能降低受損風(fēng)險(xiǎn)�����,加速系統(tǒng)集成����,減少對(duì)設(shè)備供貨的依賴�����。一旦完成控制模型,Simulink 環(huán)境便可將其自動(dòng)轉(zhuǎn)換為由控制系統(tǒng)運(yùn)行的 C 和 HDL 代碼�,節(jié)省時(shí)間并避免人工編程錯(cuò)誤。將系統(tǒng)模型鏈接到快速原型開(kāi)發(fā)環(huán)境可進(jìn)一步降低風(fēng)險(xiǎn)�����,因?yàn)楹笳咴试S觀察控制器在實(shí)際條件下會(huì)如何運(yùn)作�。

一個(gè)可實(shí)現(xiàn)更高電機(jī)控制性能的完整開(kāi)發(fā)環(huán)境利用 Xilinx Zynq SoC 實(shí)現(xiàn)控制器,MathWorks Simulink 用于進(jìn)行基于模型的設(shè)計(jì) 和自動(dòng)生成代碼��,ADI 公司的 智能驅(qū)動(dòng)器套件用于快速開(kāi)發(fā)驅(qū)動(dòng)系統(tǒng)原型��。

Xilinx FPGA 與 SoC 電機(jī)控制解決方案

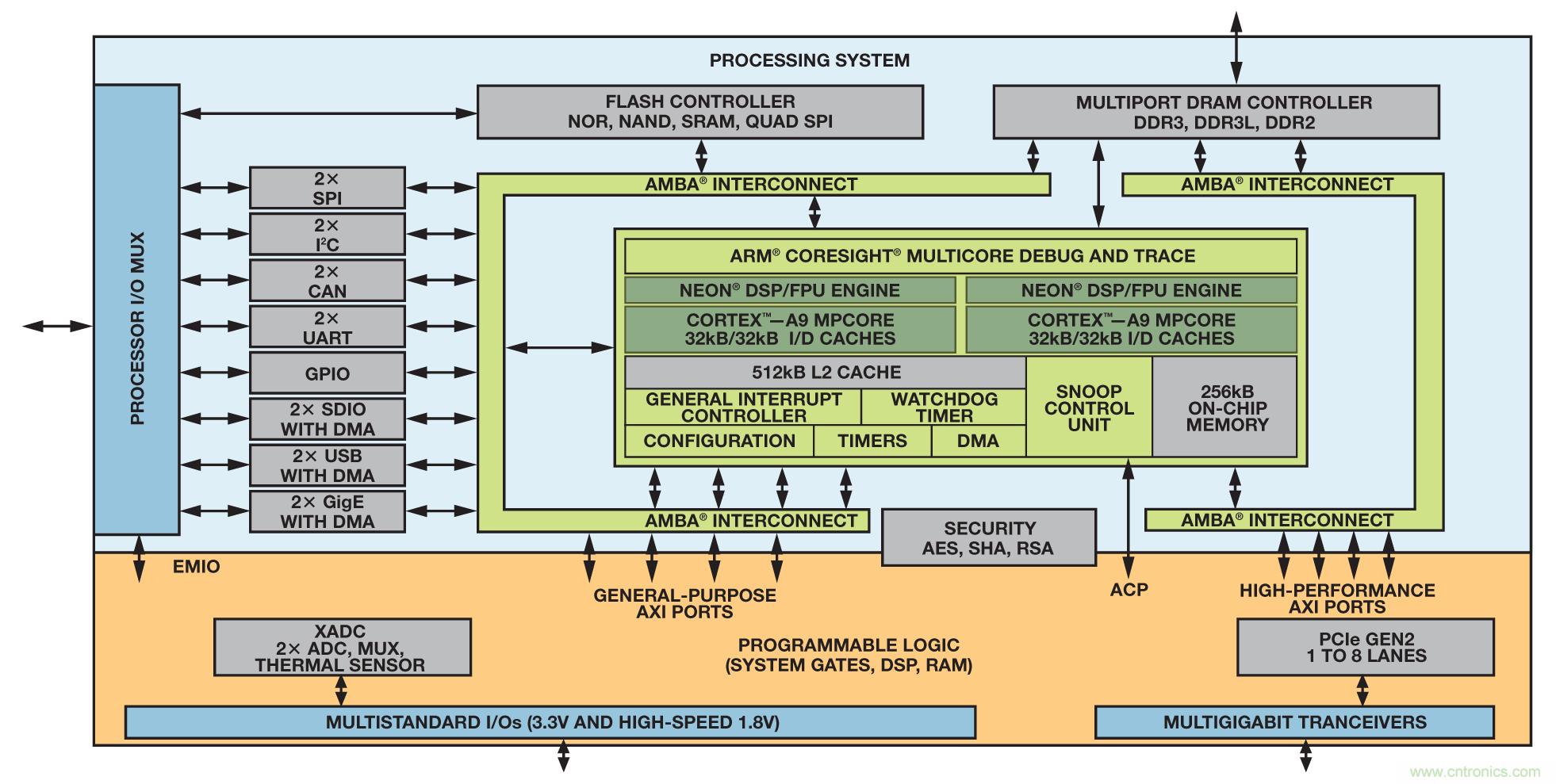

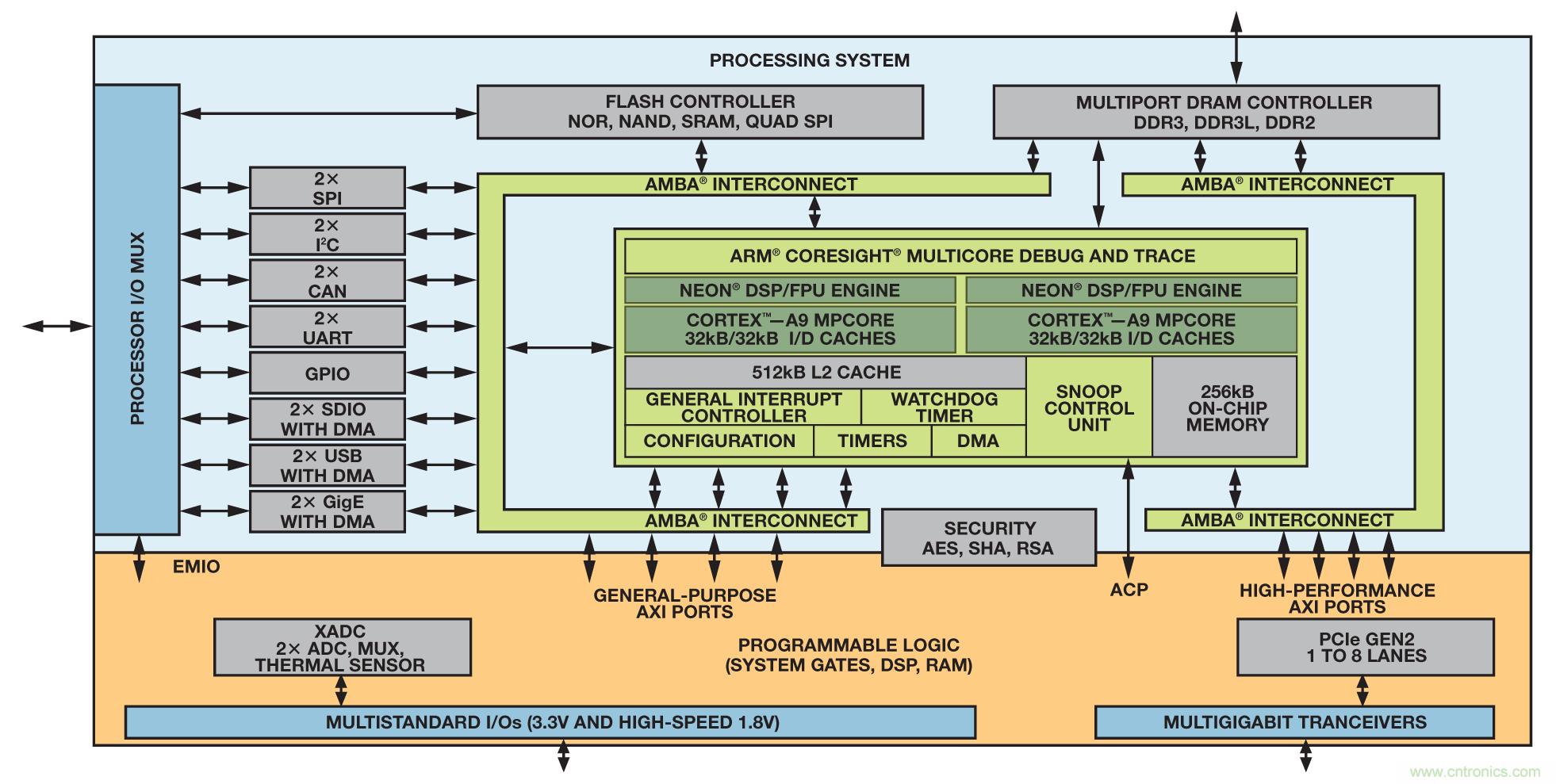

高級(jí)電機(jī)控制系統(tǒng)必須全面執(zhí)行控制�、通信和用戶接口任務(wù),每 種任務(wù)都有不同的處理帶寬要求和實(shí)時(shí)約束�。為了實(shí)現(xiàn)這樣的控 制系統(tǒng),所選的硬件平臺(tái)必須魯棒且可擴(kuò)展����,以便為將來(lái)的系統(tǒng) 改進(jìn)和擴(kuò)張創(chuàng)造條件。Zynq All Programmable SoC 集高性能處理 系統(tǒng)與可編程邏輯于一體����,滿足上述要求(如圖 1 所示)����。這種 組合可提供出色的并行處理能力��、實(shí)時(shí)性能�����、快速計(jì)算和靈活的 連接��。該 SoC 集成了兩個(gè) Xilinx 模數(shù)轉(zhuǎn)換器(XADC)�,用于監(jiān)控 系統(tǒng)或外部模擬傳感器���。

圖 1. Xilinx Zynq SoC 功能框圖

Zynq 包括一個(gè)雙核 ARM Cortex-A9 處理器����、一個(gè) NEON 協(xié)處理 器和多個(gè)用于加速軟件執(zhí)行的浮點(diǎn)擴(kuò)展單元��。處理系統(tǒng)處理管理 控制��、運(yùn)動(dòng)控制�、系統(tǒng)管理、用戶接口和遠(yuǎn)程維護(hù)等任務(wù)��,這些 功能非常適合通過(guò)軟件實(shí)現(xiàn)。為了發(fā)揮系統(tǒng)的能力���,可以采用嵌 入式 Linux 或?qū)崟r(shí)操作系統(tǒng)���。可以使用自給自足的處理器�,而無(wú) 需配置可編程邏輯。這樣����,軟件開(kāi)發(fā)人員編寫(xiě)代碼與硬件工程師 設(shè)計(jì) FPGA 結(jié)構(gòu)可以同時(shí)進(jìn)行。

在可編程邏輯方面��,該器件擁有多達(dá) 444,000 個(gè)邏輯單元和 2200 個(gè) DSP Slice�,可提供巨大的處理帶寬。FPGA 結(jié)構(gòu)可擴(kuò)展����,因而 用戶的選擇范圍很廣——從包含 28,000 個(gè)邏輯單元的小型器件到 支持最具挑戰(zhàn)性的信號(hào)處理應(yīng)用的高端器件。5 個(gè) AMBA-4 AXI 高速互連將可編程邏輯緊密地耦合到處理系統(tǒng)�,提供相當(dāng)于 3000 以上引腳的有效帶寬?���?删幊踢壿嬤m合執(zhí)行時(shí)間關(guān)鍵的處理密集 型任務(wù)����,如實(shí)時(shí)工業(yè)以太網(wǎng)協(xié)議等�,而且它支持多個(gè)控制內(nèi)核并 行工作,以實(shí)現(xiàn)多軸機(jī)器或多重控制系統(tǒng)��。

基于 Xilinx All Programmable SoC 的解決方案和平臺(tái)滿足當(dāng)今復(fù) 雜控制算法(如磁場(chǎng)定向控制 FOC)和復(fù)雜調(diào)制方案(如 Xilinx 和 Qdesys 設(shè)計(jì)的再生脈沖頻率調(diào)制器3 )所提出的關(guān)鍵時(shí)序和性 能要求�����。

利用 MathWorks Simulink 實(shí)現(xiàn)基于模型的設(shè)計(jì)

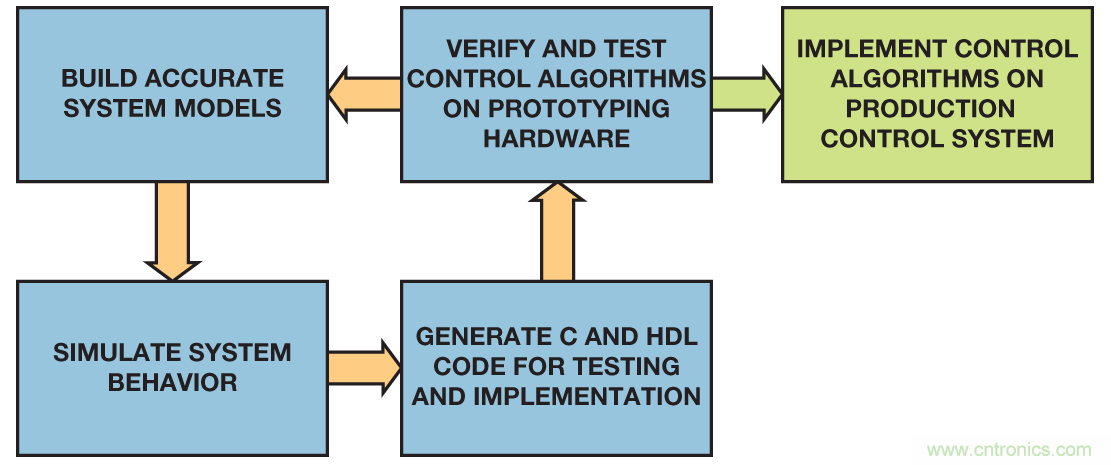

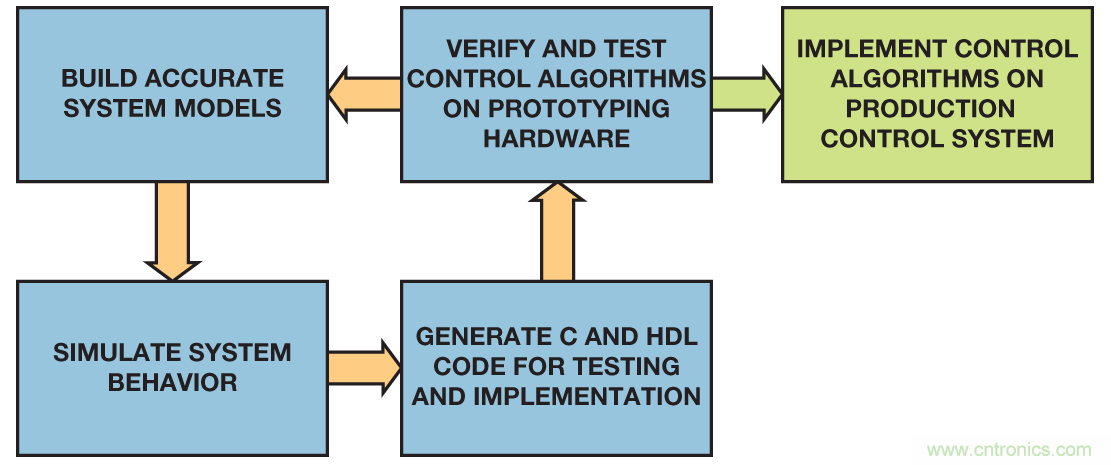

Simulink 是一種支持多域仿真和基于模型設(shè)計(jì)的框圖環(huán)境��,非常 適合對(duì)包括控制算法和工廠模型的系統(tǒng)進(jìn)行仿真�����。為了實(shí)現(xiàn)精確 定位等目的���,電機(jī)控制算法會(huì)調(diào)節(jié)速度、轉(zhuǎn)矩和其他參數(shù)��。利用 仿真評(píng)估控制算法可以有效地確定電機(jī)控制設(shè)計(jì)是否合適�,判斷 其合適后再進(jìn)行昂貴的硬件測(cè)試,從而減少算法開(kāi)發(fā)的時(shí)間和成 本。圖 2 給出了設(shè)計(jì)電機(jī)控制算法的有效工作流程:

● 構(gòu)建精確的控制器和工廠模型�,常常是根據(jù)電機(jī)、驅(qū)動(dòng)電子��、傳感器和負(fù)載的資源庫(kù)

● 對(duì)系統(tǒng)行為進(jìn)行仿真以驗(yàn)證控制器的表現(xiàn)是否符合預(yù)期

● 產(chǎn)生 C 代碼和 HDL 進(jìn)行實(shí)時(shí)測(cè)試和實(shí)施

● 利用原型硬件測(cè)試控制算法

● 在原型硬件上進(jìn)行仿真和測(cè)試后�����,如果控制系統(tǒng)證明令人滿意�����,則將控制器部署到最終生產(chǎn)系統(tǒng)上

圖 2. 電機(jī)控制算法設(shè)計(jì)的工作流程

MathWorks產(chǎn)品包括Control System Toolbox,™ SimPowerSystems,™ 和 Simscape™ 提供工業(yè)標(biāo)準(zhǔn)算法和應(yīng)用程序以對(duì)線性控制系統(tǒng) 進(jìn)行系統(tǒng)化分析�����、設(shè)計(jì)和調(diào)諧�����,此外還有元件庫(kù)和分析工具���,用 于對(duì)機(jī)械�、電氣���、液壓和其他物理領(lǐng)域的各種系統(tǒng)進(jìn)行建模和仿 真���。利用這些工具可以創(chuàng)建高保真的工廠和控制器模型�����,進(jìn)而驗(yàn) 證控制系統(tǒng)的行為和性能�����,成功之后方移交實(shí)際實(shí)施��。該仿真環(huán) 境是驗(yàn)證極端功能情形和工作狀況的理想場(chǎng)所,確?����?刂破饕褳?這些狀況做好準(zhǔn)備�����,并且其實(shí)際操作對(duì)設(shè)備和工作人員都將是安 全的��。

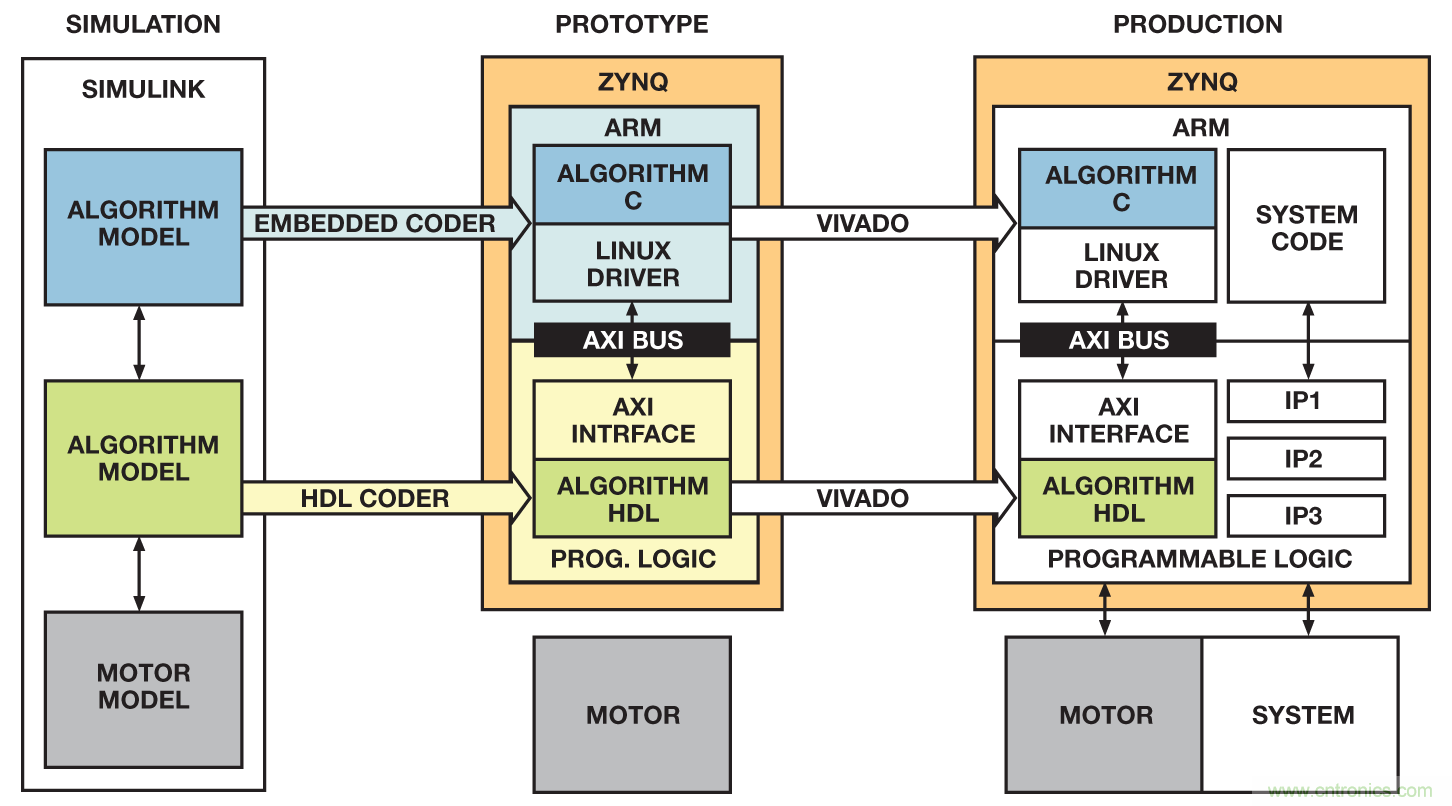

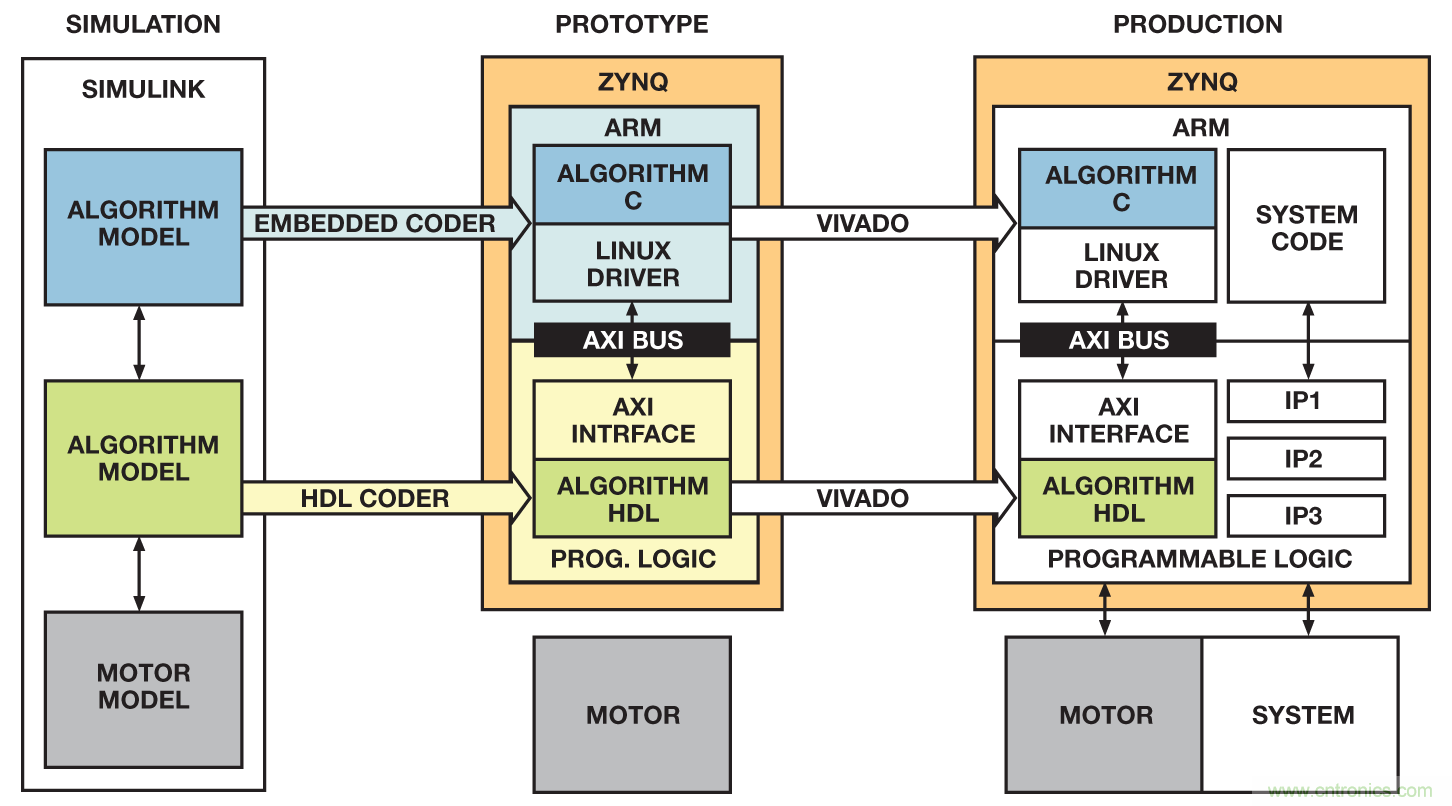

一旦控制系統(tǒng)在仿真環(huán)境中完成了全面驗(yàn)證�,就可以利用嵌入式 轉(zhuǎn)碼器和 HDL 轉(zhuǎn)碼工具將其轉(zhuǎn)換為 C 代碼和 HDL,并部署到原 型硬件上進(jìn)行測(cè)試,然后部署到最終生產(chǎn)系統(tǒng)上�。此時(shí)要指定定 點(diǎn)和時(shí)序行為等軟硬件實(shí)施要求。自動(dòng)生成代碼有助于縮短從概 念到實(shí)際系統(tǒng)實(shí)現(xiàn)所需的時(shí)間���,消除編程錯(cuò)誤�����,確保實(shí)際結(jié)果與 模型相符���。圖 3 給出了在 Simulink 中進(jìn)行電機(jī)控制器建模并將其 轉(zhuǎn)移到最終生產(chǎn)系統(tǒng)所需的實(shí)際步驟。

圖 3. 從仿真到生產(chǎn)的過(guò)程

第一步是在 Simulink 中對(duì)控制器和工廠進(jìn)行建模和仿真��。在這一 階段�����,控制器算法被劃分為在軟件中實(shí)現(xiàn)的模塊和在可編程邏輯 中實(shí)現(xiàn)的模塊�����。劃分和仿真完成后��,利用嵌入式轉(zhuǎn)碼器和 HDL 轉(zhuǎn)碼器將控制器模型轉(zhuǎn)換為 C 代碼和 HDL���?����;?Zynq 的原型系 統(tǒng)驗(yàn)證控制算法的性能�����,并且?guī)椭M(jìn)一步調(diào)諧控制器模型����,然后 轉(zhuǎn)移到生產(chǎn)階段。在生產(chǎn)階段��,將自動(dòng)生成的 C 代碼和 HDL 集 成到復(fù)雜的生產(chǎn)系統(tǒng)框架中�。此工作流程確保控制算法在達(dá)到 生產(chǎn)階段之前經(jīng)過(guò)全面驗(yàn)證和測(cè)試���,使得系統(tǒng)魯棒性具有高可 信度。

利用 ADI 公司智能驅(qū)動(dòng)器套件快速完成原型開(kāi)發(fā)

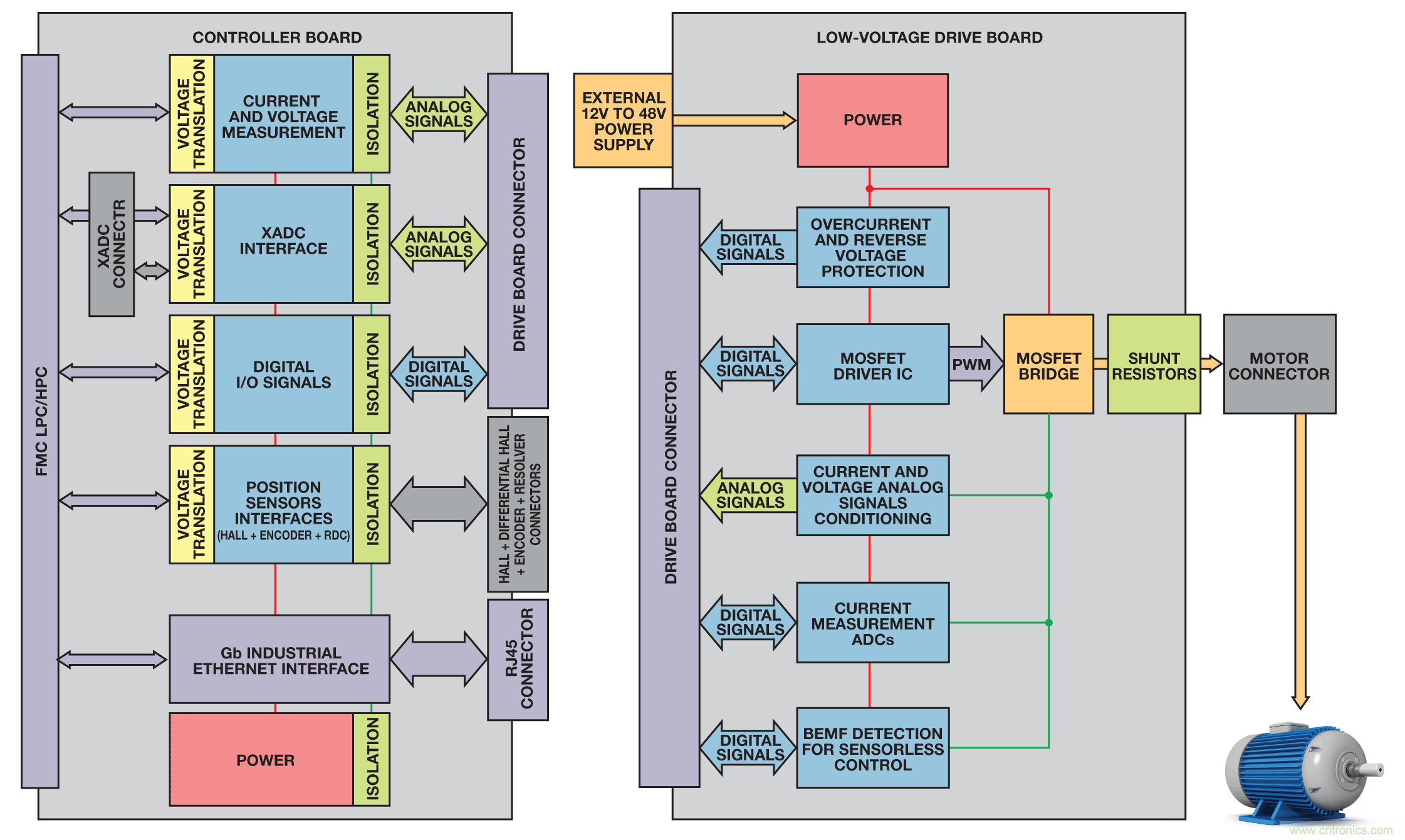

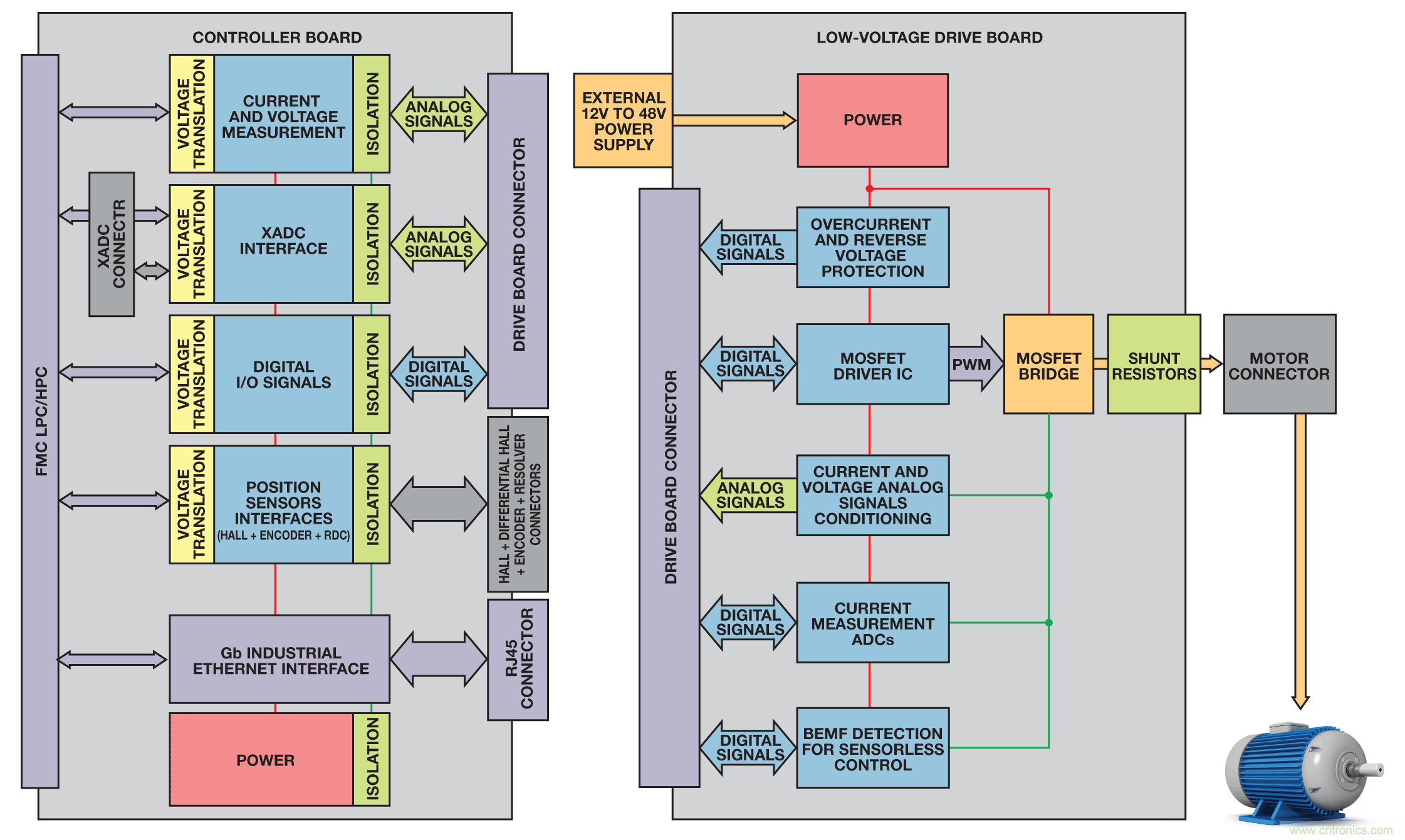

選擇合適的原型開(kāi)發(fā)硬件是設(shè)計(jì)過(guò)程的一個(gè)主要步驟��。ADI 公司 的智能驅(qū)動(dòng)器套件支持快速���、高效的原型開(kāi)發(fā)�。AvnetZynq-7000 All Programmable SoC/Analog Devices智能驅(qū)動(dòng)器套件將 Zynq- 7000 All Programmable SoC ARM 雙核 Cortex-A9 + 28 nm 可編程 邏輯與 ADI 公司最新一代高精度數(shù)據(jù)轉(zhuǎn)換器和數(shù)字隔離相 結(jié)合,可實(shí)現(xiàn)高性能電機(jī)控制和雙通道千兆以太網(wǎng)工業(yè)網(wǎng)絡(luò)連 接�����。該套件帶有 Avnet ZedBoard 7020 基板和 ADI 公司的 AD-FMCMOTCON1-EBZ 模塊����,構(gòu)成一個(gè)完整的驅(qū)動(dòng)系統(tǒng),能夠 高效控制多種類(lèi)型的電機(jī)����。另外,該套件可以利用 ADI 公司的 AD-DYNO1-EBZ 測(cè)功器驅(qū)動(dòng)系統(tǒng)�����,進(jìn)行擴(kuò)展�,后者是一個(gè)動(dòng)態(tài)可調(diào) 的負(fù)載,可用來(lái)測(cè)試實(shí)時(shí)電機(jī)控制性能�����。AD-FMCMOTCON1-EBZ 模塊由控制器和驅(qū)動(dòng)板組成�,如圖 4 所示。

圖 4. AD-FMCMOTCON1-EBZ 功能框圖

控制板是一個(gè)混合信號(hào) FPGA 夾層卡 (FMC)�����,可利用低引腳數(shù) (LPC) 或高引腳數(shù) (HPC) FMC 連接器連接到任何 Xilinx FPGA 或 SoC 平臺(tái)。它具有以下特性:

● 利用隔離式 ADC 測(cè)量電流和電壓

● 隔離式 Xilinx XADC 接口

● 完全隔離的數(shù)字控制和反饋信號(hào)

● 霍爾��、差分霍爾��、編碼器和旋變器接口

● 2 個(gè)千兆以太網(wǎng)物理層��,支持 EtherCAT����、ProfiNET、Ethernet/IP或 Powerlink 等高速工業(yè)通信協(xié)議

● FMC 信號(hào)電壓自適應(yīng)接口��,支持在所有 FMC 電壓電平上無(wú)縫工作

隔離是任何電機(jī)控制系統(tǒng)的一個(gè)關(guān)鍵方面�����,其目的是保護(hù)控制器 和用戶����?����?刂瓢迳夏M和數(shù)字信號(hào)的完全隔離,確保 FPGA 平臺(tái) 永遠(yuǎn)不受電機(jī)驅(qū)動(dòng)側(cè)可能產(chǎn)生的危險(xiǎn)電壓影響�����。

驅(qū)動(dòng)板包含驅(qū)動(dòng)電機(jī)以及電流電壓檢測(cè)與保護(hù)電路所需的全部電源電子���。該板具有以下特性:

● 以最大 18 A 電流驅(qū)動(dòng) 12 V 至 48 V 范圍的 BLDC(無(wú)刷直流)/PMSM(永磁同步電機(jī))/有刷直流/步進(jìn)電機(jī)

● 動(dòng)態(tài)制動(dòng)功能和集成式過(guò)流與反向電壓保護(hù)

● 利用隔離式 ADC 測(cè)量相電流�;可編程增益放大器使電流測(cè)量輸入范圍達(dá)到最大

● 向控制板提供直流總線電壓��、相電流和總電流反饋信號(hào)

● 集成 BEMF 過(guò)零檢測(cè)��,用于實(shí)現(xiàn) PMSM 或 BLDC 電機(jī)的無(wú)傳感器控制

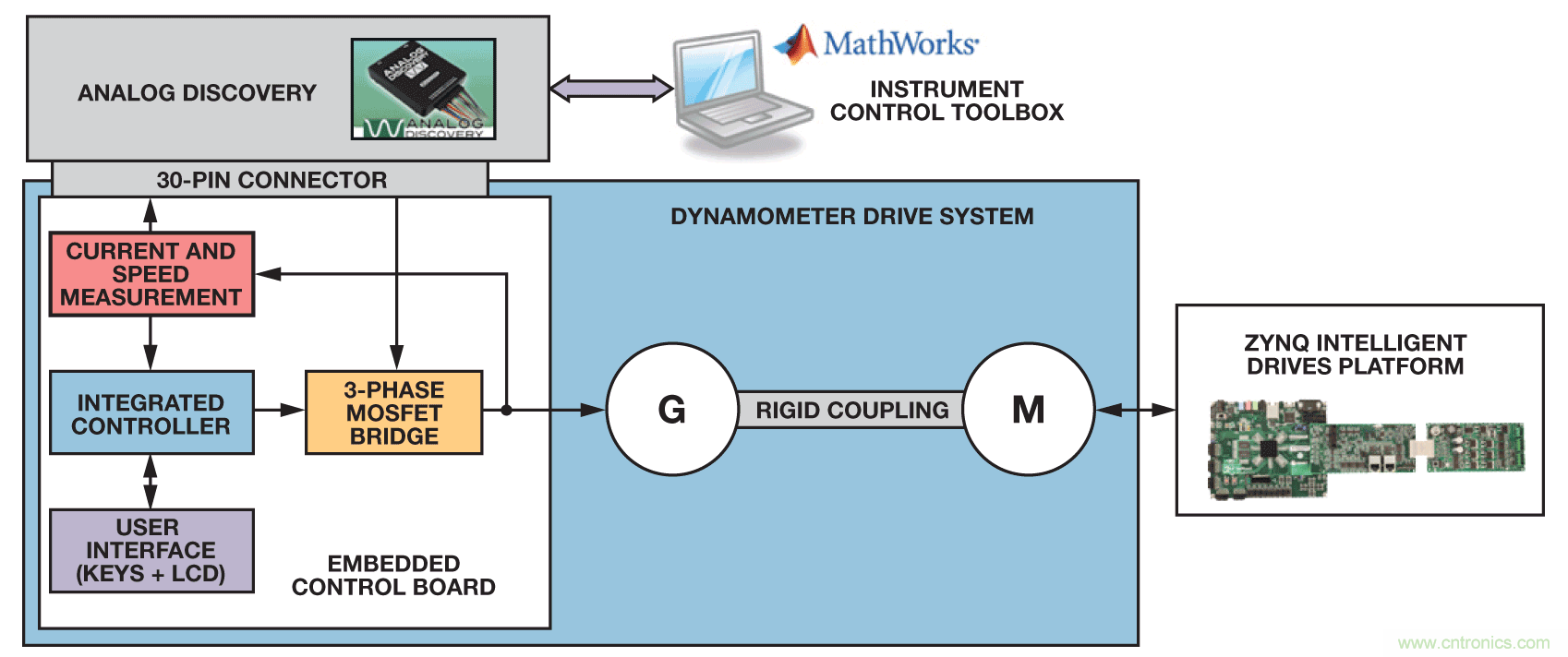

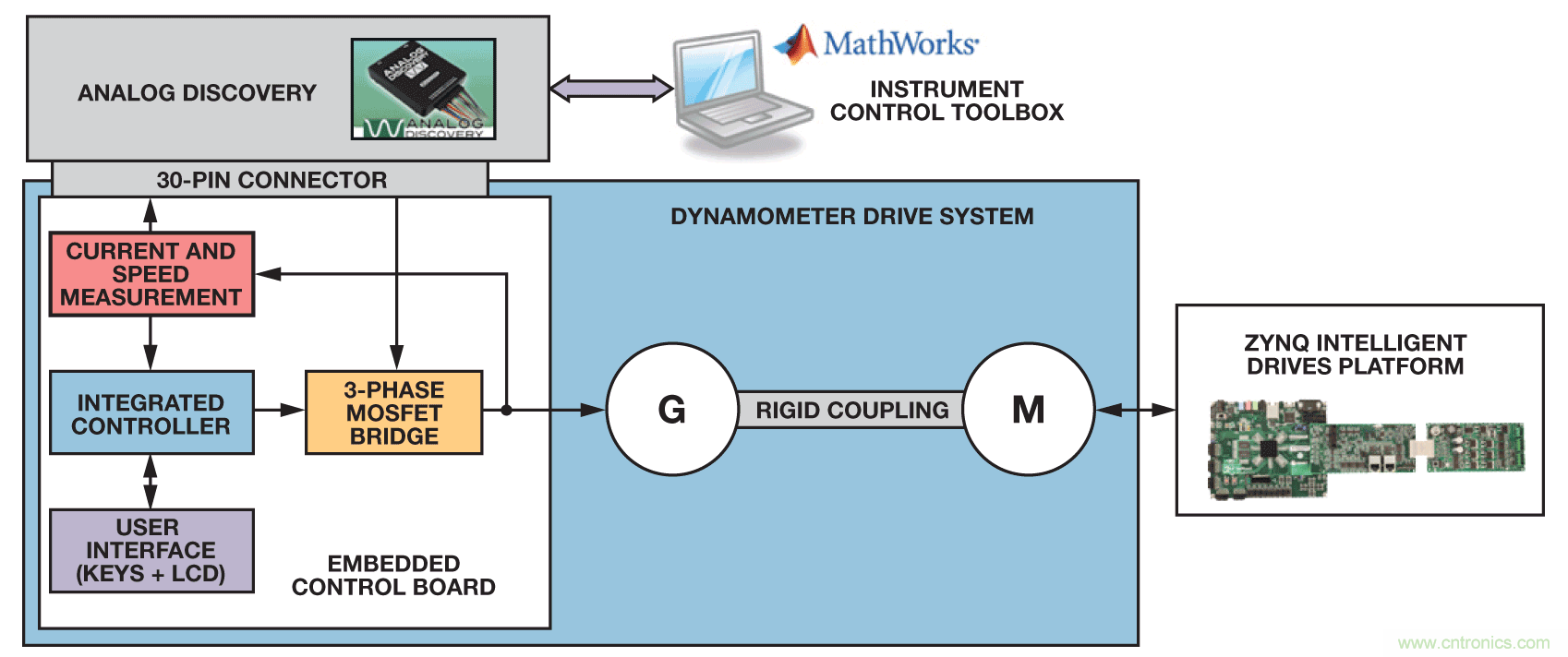

測(cè)功器是一個(gè)動(dòng)態(tài)可調(diào)的負(fù)載�����,可用于測(cè)試實(shí)時(shí)電機(jī)控制性 能���,由兩臺(tái) BLDC 電機(jī)通過(guò)剛性連接直接耦合而成���。其中一臺(tái) BLDC 電機(jī)用作負(fù)載,由測(cè)功器的嵌入式控制系統(tǒng)控制����,而另 一臺(tái)由 ADI 公司的智能驅(qū)動(dòng)器套件驅(qū)動(dòng)�����,如圖 5 所示����。該系統(tǒng) 配有一個(gè)用戶界面�����,用于顯示有關(guān)負(fù)載電流和速度的信息��,并 支持設(shè)置不同的負(fù)載曲線���。要實(shí)現(xiàn)外部控制����,可利用 Analog Discovery USB 示波器捕捉負(fù)載信號(hào)�;要從 MATLAB®直接控 制,可使用 MathWorks Instrument Control Toolbox™����。

圖 5. 測(cè)功器驅(qū)動(dòng)系統(tǒng)

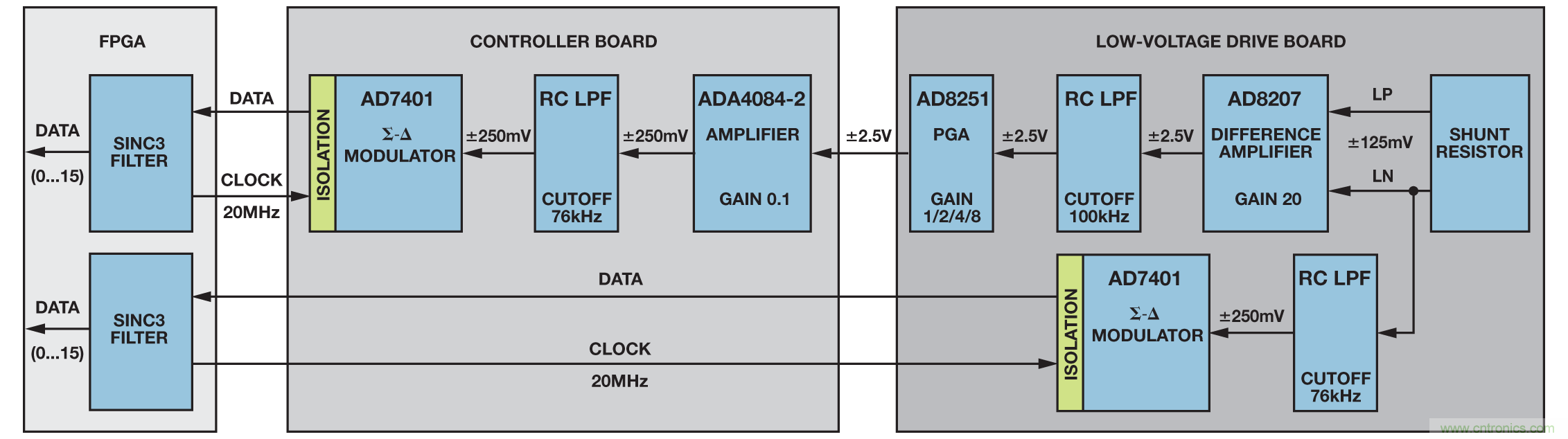

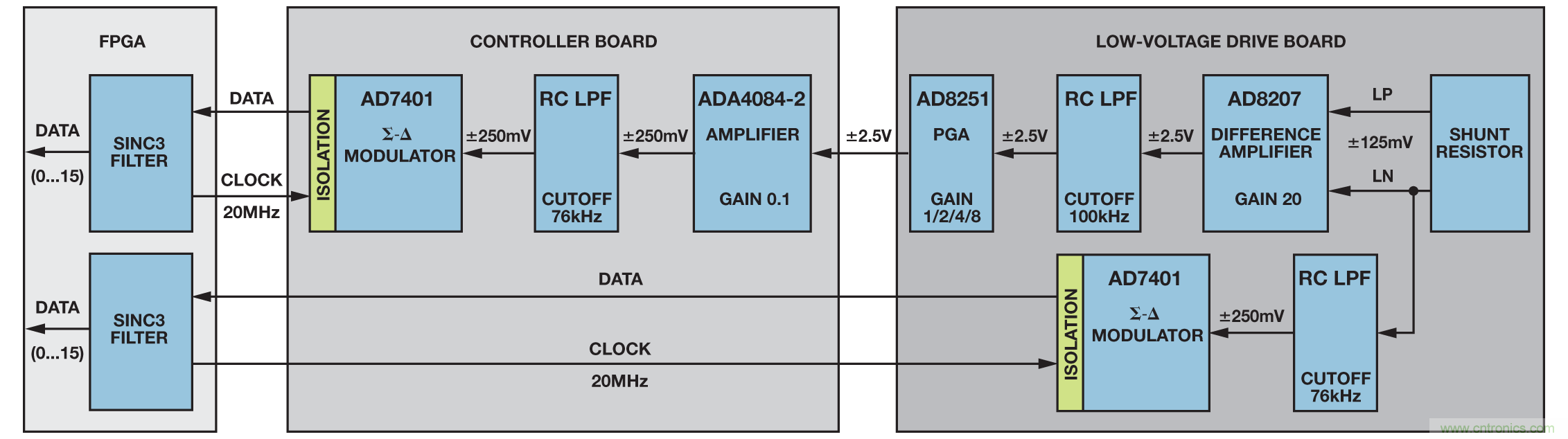

電機(jī)電流和電壓測(cè)量的質(zhì)量對(duì)電機(jī)控制系統(tǒng)的性能有很大影響。 通過(guò)利用高性能模擬信號(hào)調(diào)理器件和 ADC,ADI 公司智能驅(qū)動(dòng) 器套件提供精密電流和電壓測(cè)量���。測(cè)量路徑分為控制器和驅(qū)動(dòng)板 兩部分,如圖 6 所示��。

圖 6. 相電流信號(hào)鏈

相電流通過(guò)測(cè)量分流電阻上的電壓來(lái)檢測(cè)�����。取決于 ADC 是否靠 近分流電阻���,有兩條可能的測(cè)量路徑可以獲得最高測(cè)量精度�。如 果 ADC 靠近分流電阻����,則信號(hào)路徑非常短,不易受到噪聲耦合 影響����。分流電阻上的小差分電壓由隔離式Σ-Δ調(diào)制器AD7401直 接測(cè)量,而無(wú)需其他接口和信號(hào)調(diào)理電路���。如果 ADC 遠(yuǎn)離分流 電阻��,則信號(hào)路徑很長(zhǎng)�,容易受到噪聲耦合影響,尤其是電源開(kāi) 關(guān)噪聲和電機(jī)的噪聲耦合�����。必須采取特別措施確保 ADC 與分流 電阻之間的 PCB 走線和信號(hào)調(diào)理電路受到適當(dāng)?shù)钠帘?�。分流?阻上的小差分電壓被驅(qū)動(dòng)板上的差動(dòng)放大器AD8207 放大�����,后者 置于分流電阻附近以避免噪聲耦合�����。信號(hào)從±125 mV 滿量程輸 入范圍放大至±2.5 V 范圍����,以最大程度地降低耦合噪聲的影 響。放大后的信號(hào)又經(jīng)過(guò)一個(gè)采用可編程增益儀表放大器(PGIA)AD8251的放大級(jí)��,以確保 ADC 始終接收到經(jīng)過(guò)適當(dāng)縮放以適應(yīng) 輸入范圍的輸入信號(hào)���。放大后的模擬信號(hào)經(jīng)過(guò)連接器進(jìn)入控制 板���。連接器會(huì)屏蔽每個(gè)模擬信號(hào)���,以降低噪聲耦合影響。來(lái)自驅(qū) 動(dòng)板的模擬信號(hào)利用運(yùn)算放大器ADA4084-2重新轉(zhuǎn)換到AD7401輸入范圍��。

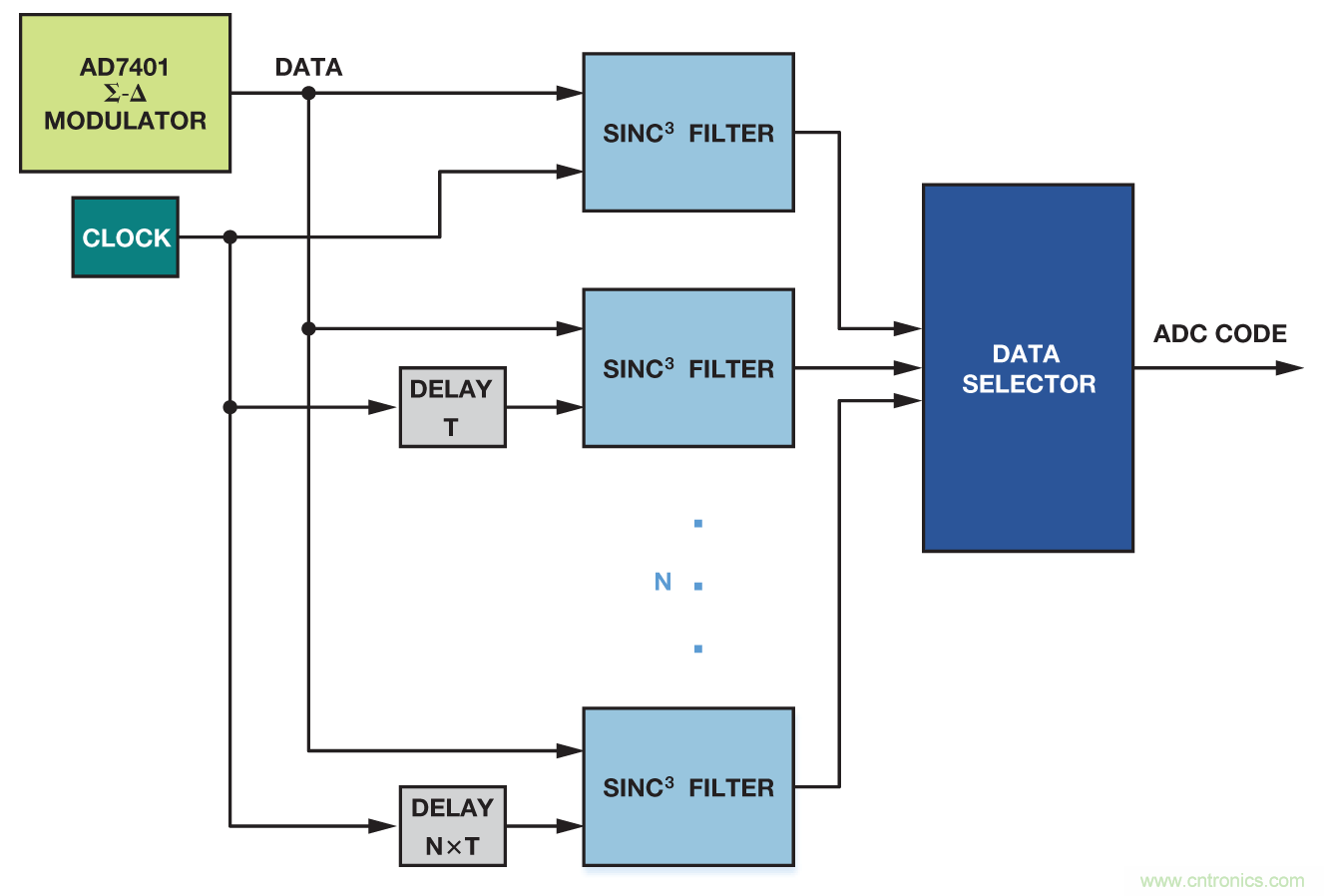

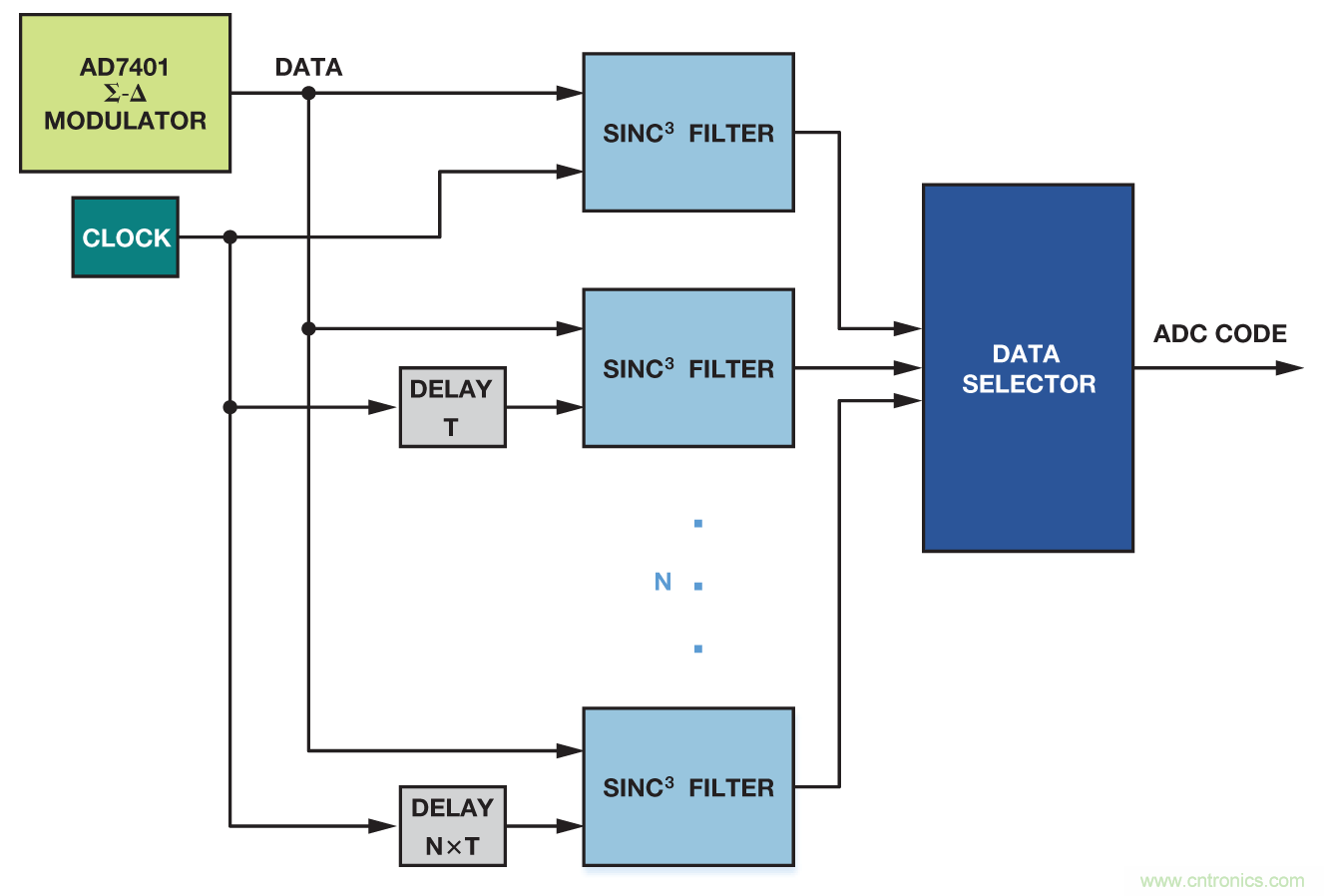

電流和電壓反饋信號(hào)鏈中的最重要器件是二階隔離式Σ-Δ調(diào)制 器 AD7401A���。這款高性能 ADC 具有 16 位分辨率(無(wú)失碼)����、 13.3有效位數(shù)(ENOB)和 83 dB SNR。2線數(shù)字接口包括一個(gè) 20 MHz 時(shí)鐘輸入和一個(gè) 1 位數(shù)字位流輸出���。ADC 輸出利用 sinc3 數(shù)字濾 波器重構(gòu)��。數(shù)據(jù)手冊(cè)中提供了一個(gè)針對(duì) 16 位輸出和 78 kHz 采樣 速率的濾波器模型和 HDL 實(shí)現(xiàn)方案�。輸出分辨率和采樣速率可 通過(guò)改變?yōu)V波器模型和抽取來(lái)控制��。78 kHz 采樣速率對(duì)許多應(yīng)用 可能是足夠的����,但某些情況需要更高的速率。這些情況下,可利 用圖 7 所示的濾波器庫(kù)來(lái)將系統(tǒng)采樣速率提至最高 10 MSPS (真 16 位數(shù)據(jù))���。濾波器庫(kù)包含 n 個(gè) sinc3濾波器�,其采樣時(shí)鐘 延遲 T(即 sinc3濾波器傳播時(shí)間除以 n)的倍數(shù)�。數(shù)據(jù)選擇器以 周期T輸出 ADC 碼。

圖 7. 濾波器庫(kù)

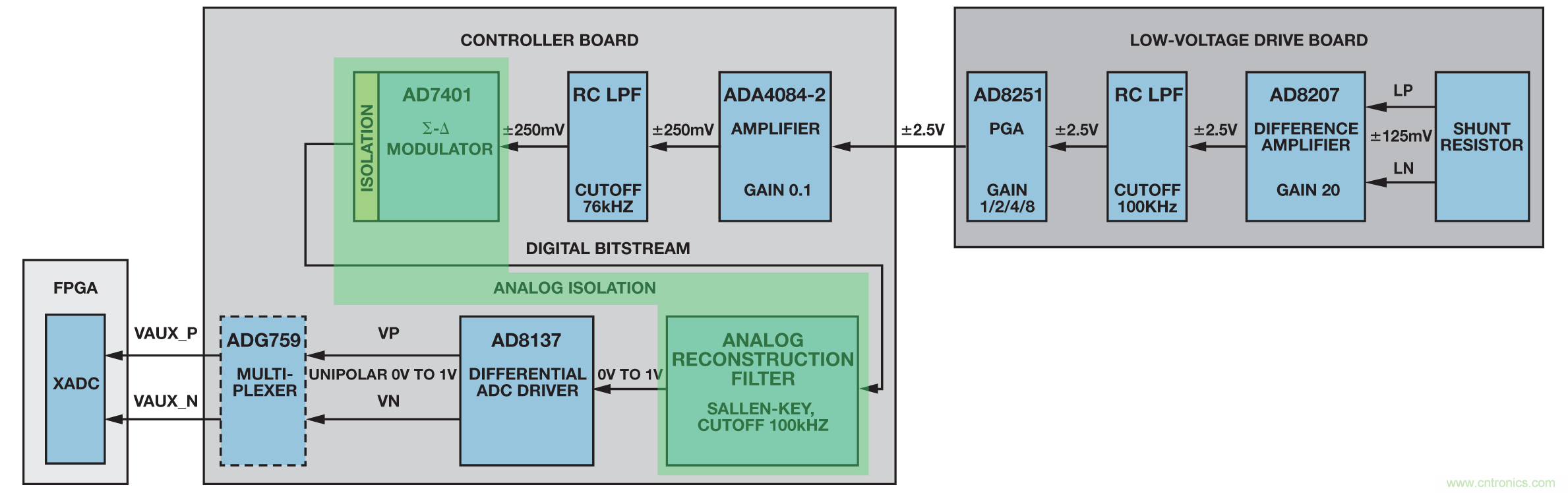

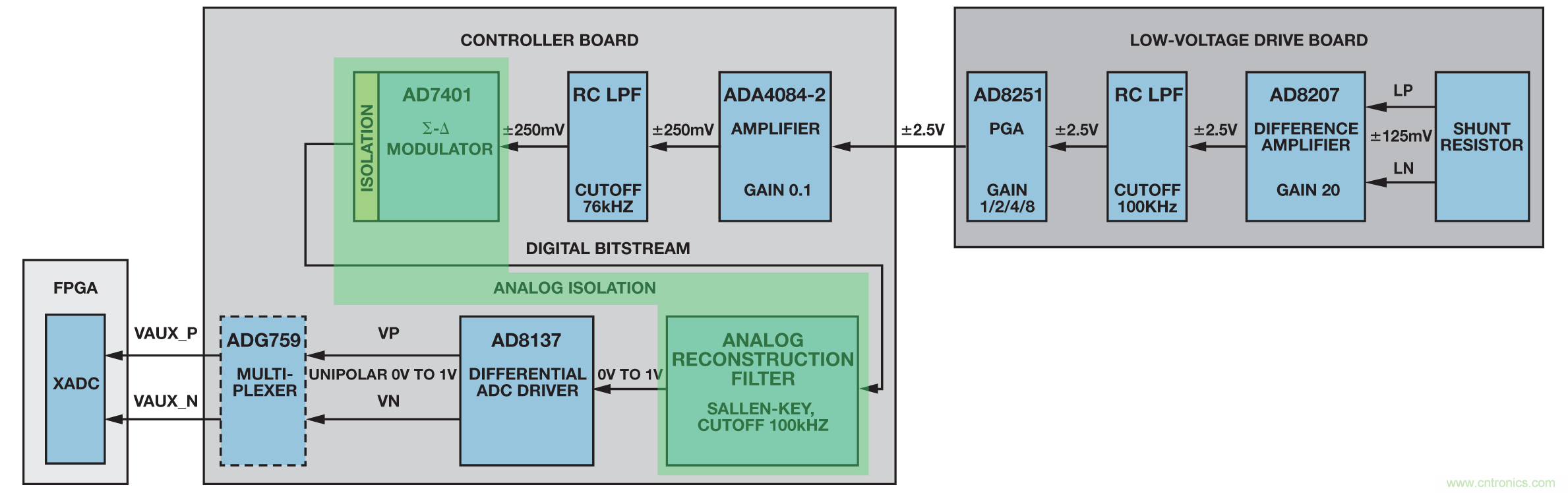

相電流測(cè)量也可以由 Zynq XADC 執(zhí)行�����。XADC 信號(hào)測(cè)量鏈?zhǔn)褂?常規(guī)測(cè)量鏈的完整路徑�����,并在 AD7401 Σ-Δ調(diào)制器之后增加一 個(gè) Sallen-Key 模擬重構(gòu)濾波器��。該濾波器是在控制板上利用運(yùn)算 放大器AD8646實(shí)現(xiàn)�����,如圖 8 所示�。隔離式Σ-Δ調(diào)制器和模擬重構(gòu)濾波器的組合為實(shí)現(xiàn) XADC 輸入信號(hào)的模擬隔離提供了一種便利、低成本的方法����,同時(shí)不影響測(cè)量質(zhì)量�。

圖8. XADC 信號(hào)測(cè)量鏈

ADI 公司智能驅(qū)動(dòng)器套件帶有一套 Simulink 控制器模型���、完整的Xilinx Vivado 框架和 ADI Linux 基礎(chǔ)設(shè)施����,便于用戶完成電機(jī)控制系統(tǒng)設(shè)計(jì)所需的全部步驟——從仿真開(kāi)始��,經(jīng)過(guò)原型開(kāi)發(fā)�,最終在生產(chǎn)系統(tǒng)上實(shí)現(xiàn)�。

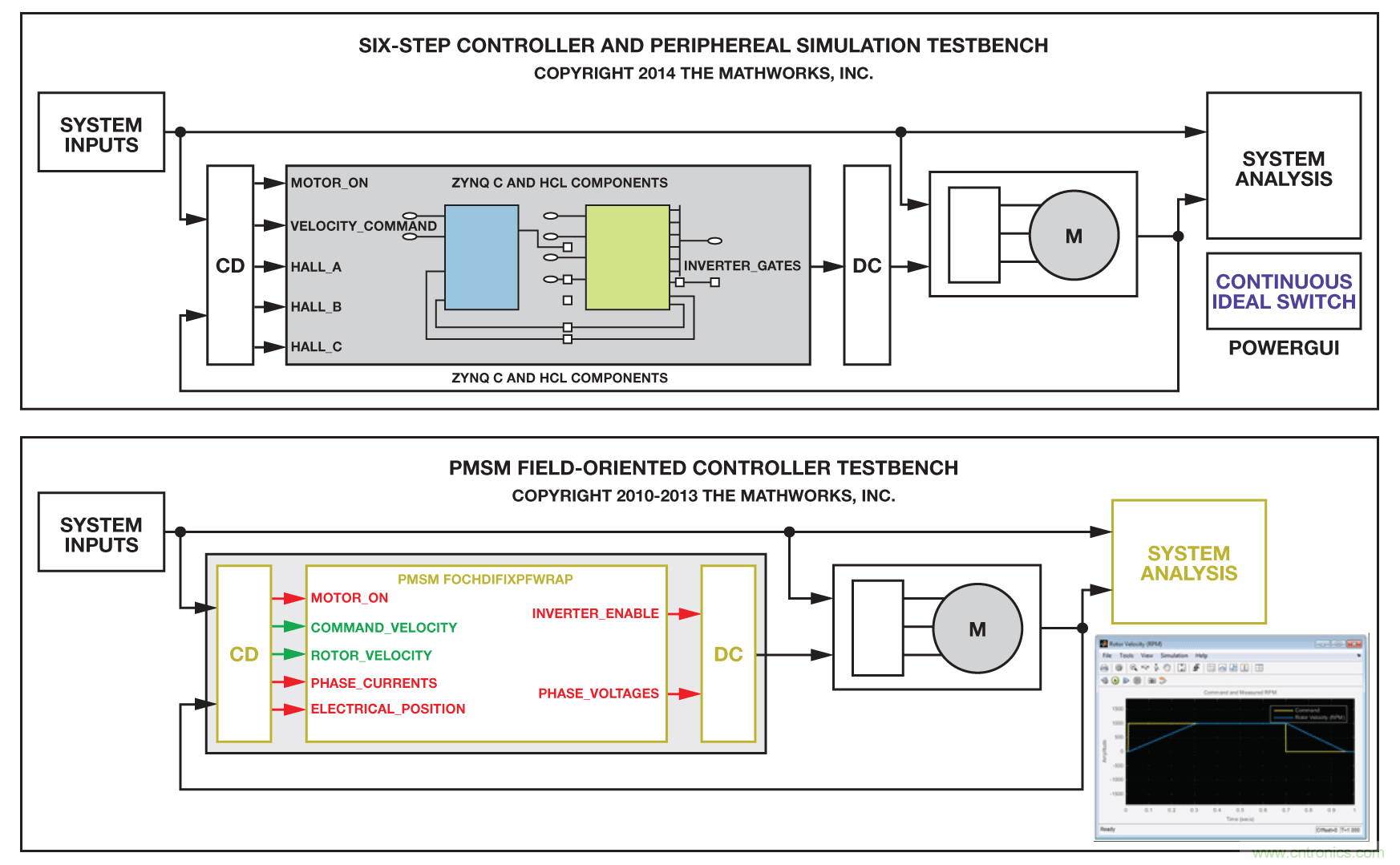

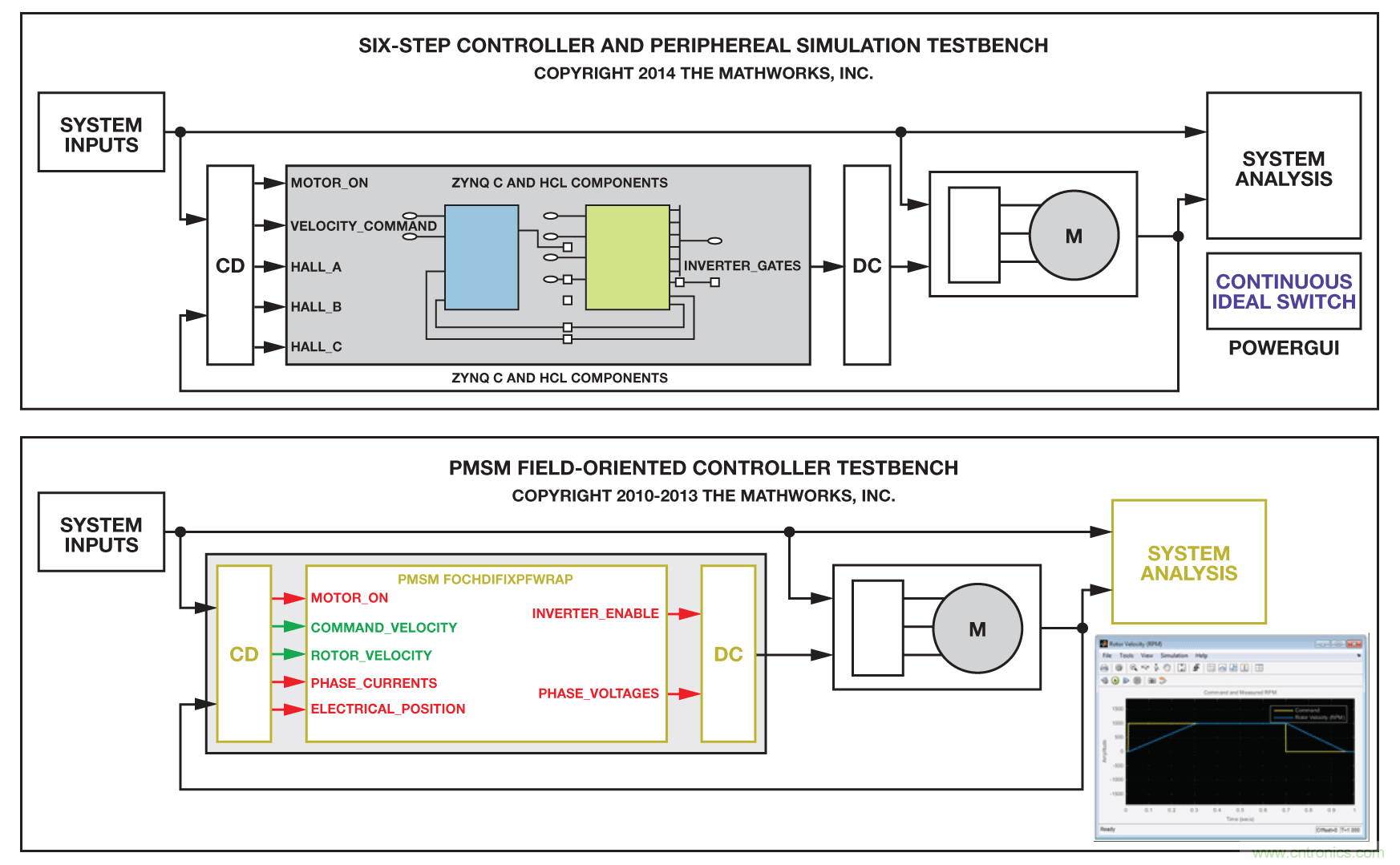

可以利用兩個(gè)控制器模型(一個(gè)六步控制器和一個(gè) PMSM 磁場(chǎng)定向控制器)來(lái)啟動(dòng)設(shè)計(jì)過(guò)程。圖 9 顯示了這兩個(gè)控制器的高級(jí)視圖���。六步控制器實(shí)現(xiàn)一個(gè)用于 BLDC 電機(jī)的梯形控制器�;FOC控制器提供一個(gè) FOC 內(nèi)核以便集成到控制系統(tǒng)中�����。

圖 9. Simulink 控制器模型

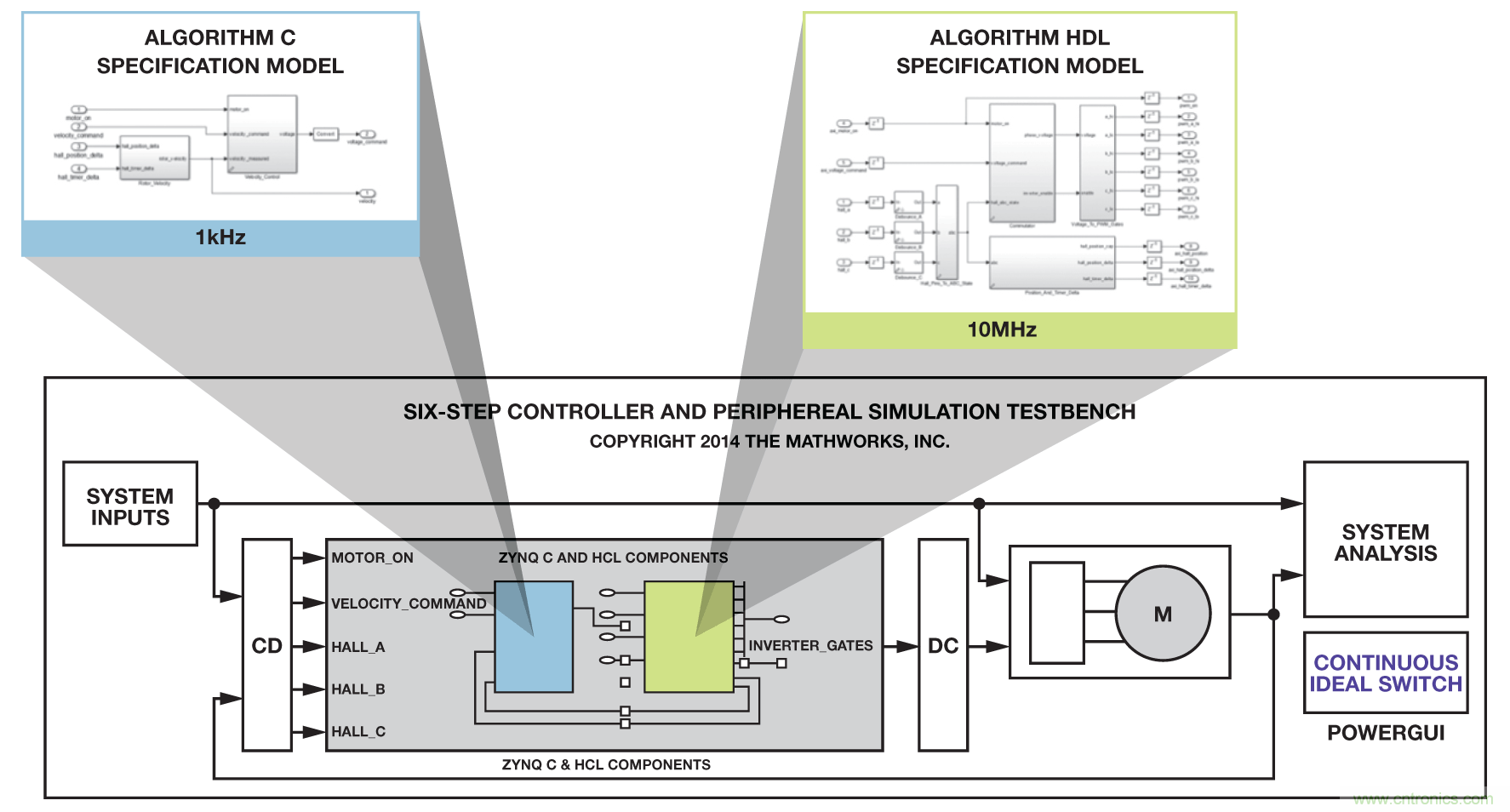

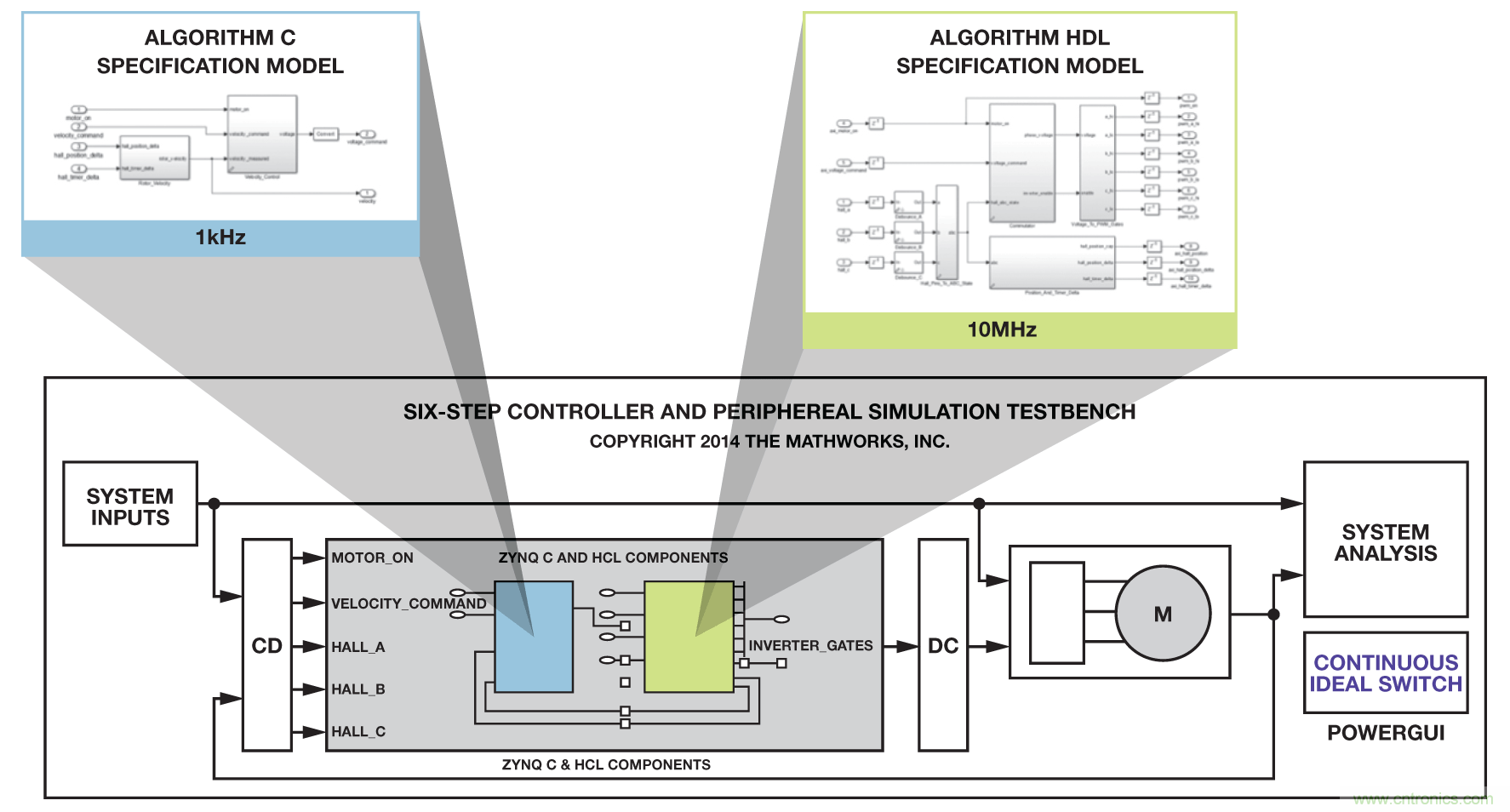

工廠和控制器模型在仿真階段創(chuàng)建��,通過(guò)完整系統(tǒng)的行為仿真來(lái)驗(yàn)證控制器符合預(yù)期�����。控制器模型劃分為由 C 代碼和 HDL 實(shí)現(xiàn)的多個(gè)部分��,并指定時(shí)序��、定點(diǎn)實(shí)現(xiàn)�����、采樣速率和環(huán)路時(shí)間等約束條件以確?�?刂破髂P偷男袨榕c在硬件實(shí)現(xiàn)中一樣���。圖 10 顯示了六步控制器的軟件和 HDL 劃分���。

圖 10. 控制器的 C 代碼和 HDL 劃分

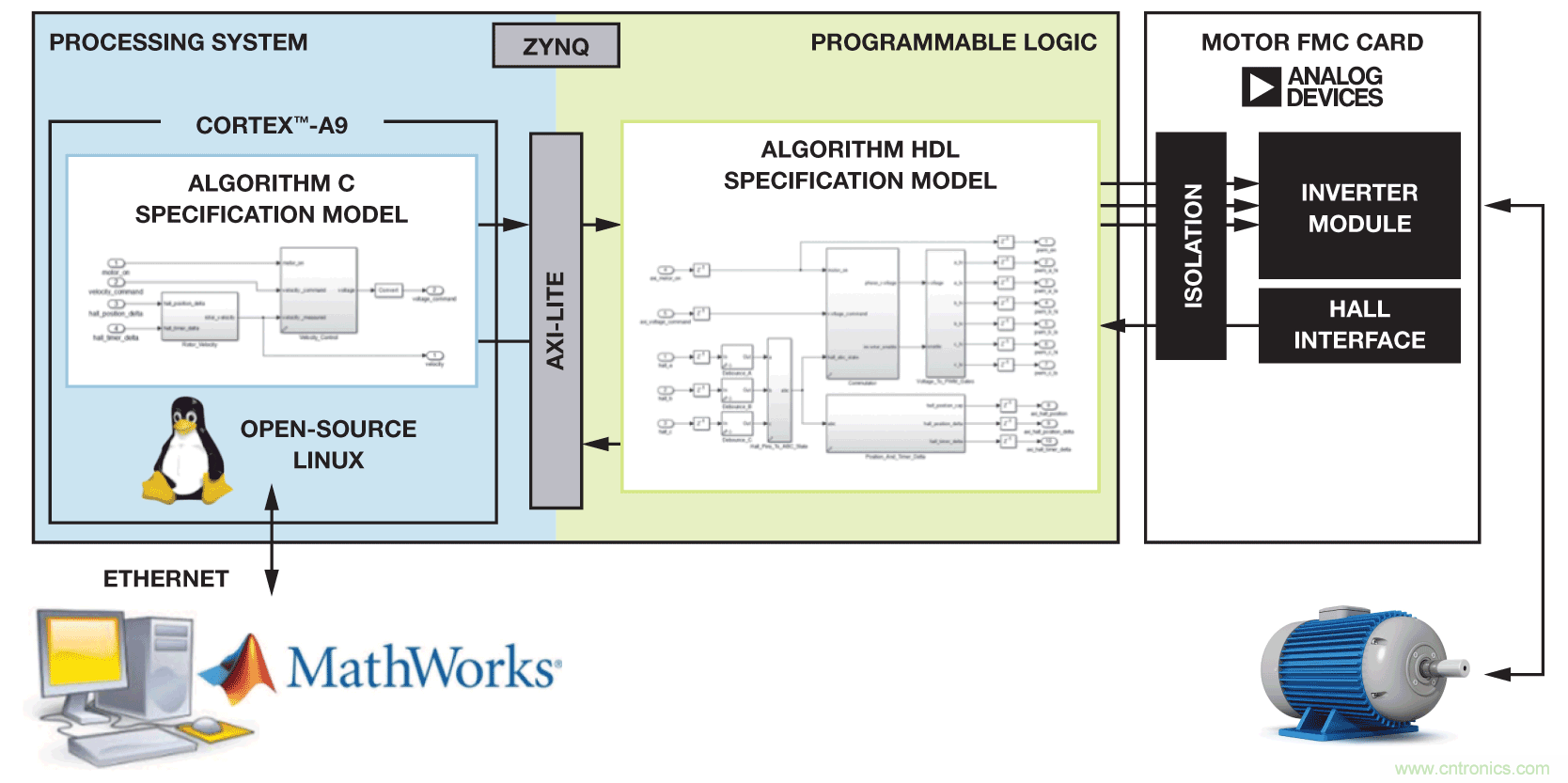

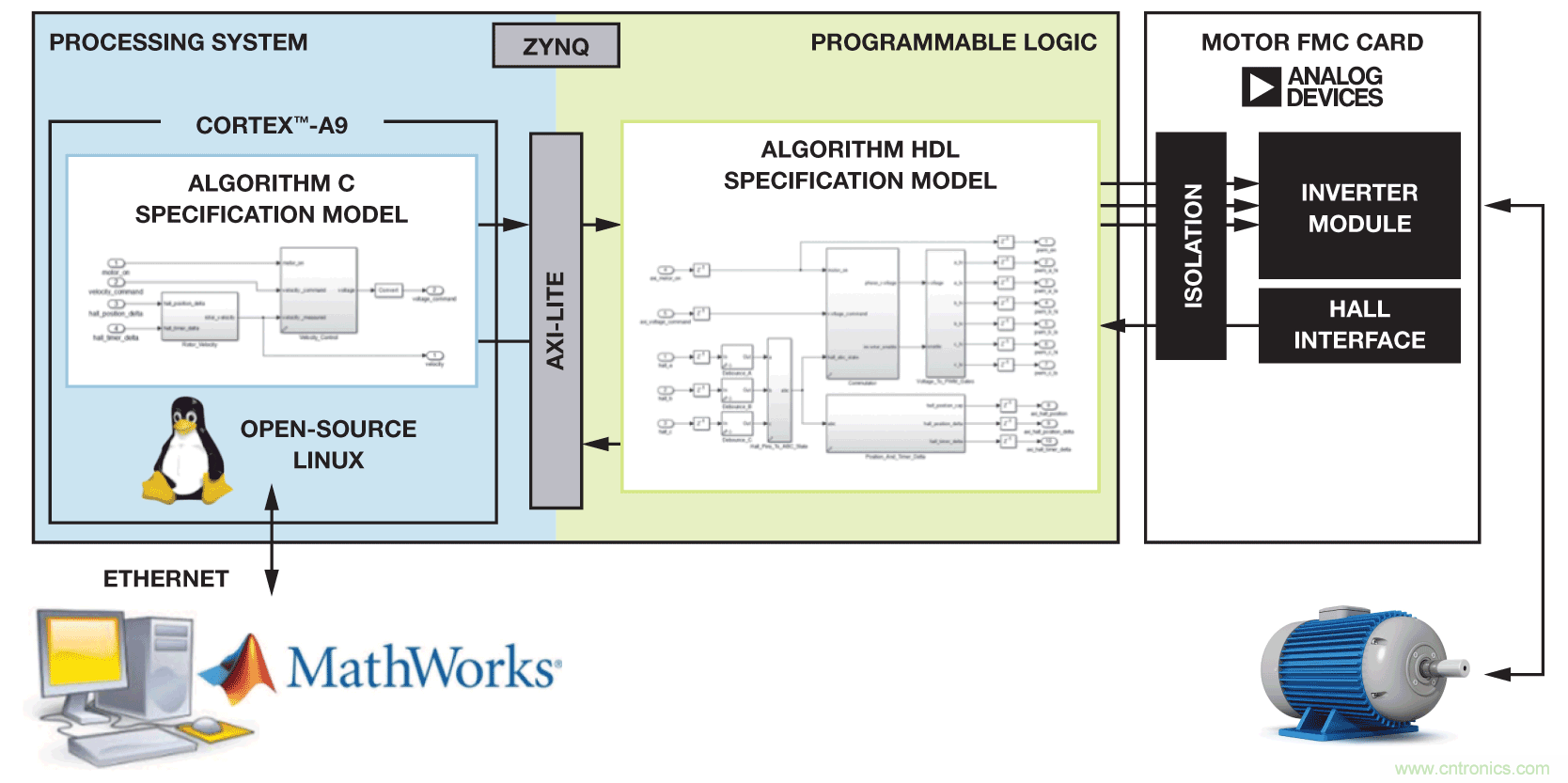

一旦控制器在仿真中經(jīng)過(guò)全面驗(yàn)證,下一步便是在硬件平臺(tái)上制作原型��。針對(duì) ARM 內(nèi)核和可編程邏輯��,Zynq SoC 引導(dǎo)工作流程從劃分為多個(gè)子系統(tǒng)的 Simulink 模型產(chǎn)生 C 代碼和 HDL���。利用此工作流程��,HDL 轉(zhuǎn)碼器生成針對(duì)可編程邏輯的 HDL���,嵌入式轉(zhuǎn)碼器則生成針對(duì) ARM 的 C 代碼���。MathWorks Zynq 支持包支持從模型生成由算法 C 代碼組成的 ARM 可執(zhí)行文件(與 AXI 總線接口),并支持從模型生成由 HDL 代碼組成的位流(與可編程邏輯引腳和 AXI 總線接口)���。圖 11 顯示了控制器實(shí)現(xiàn)及其與ADI 智能驅(qū)動(dòng)器硬件的關(guān)系�。

圖 11. 原型系統(tǒng)上的控制器實(shí)現(xiàn)

一旦將位流和可執(zhí)行文件加載到硬件中����,就可以開(kāi)始控制器的運(yùn)行測(cè)試。利用 Simulink 與運(yùn)行開(kāi)源 Linux OS 的嵌入式系統(tǒng)之間的以太網(wǎng)鏈路執(zhí)行硬件在環(huán)(HIL)測(cè)試�����。軸轉(zhuǎn)速等電機(jī)參數(shù)可以在 Simulink 中捕捉�,并與仿真結(jié)果相比較���,確保實(shí)際系統(tǒng)實(shí)現(xiàn)與模型相符����。一旦控制算法測(cè)試完畢��,便可將控制器轉(zhuǎn)移到生產(chǎn)系統(tǒng)上。

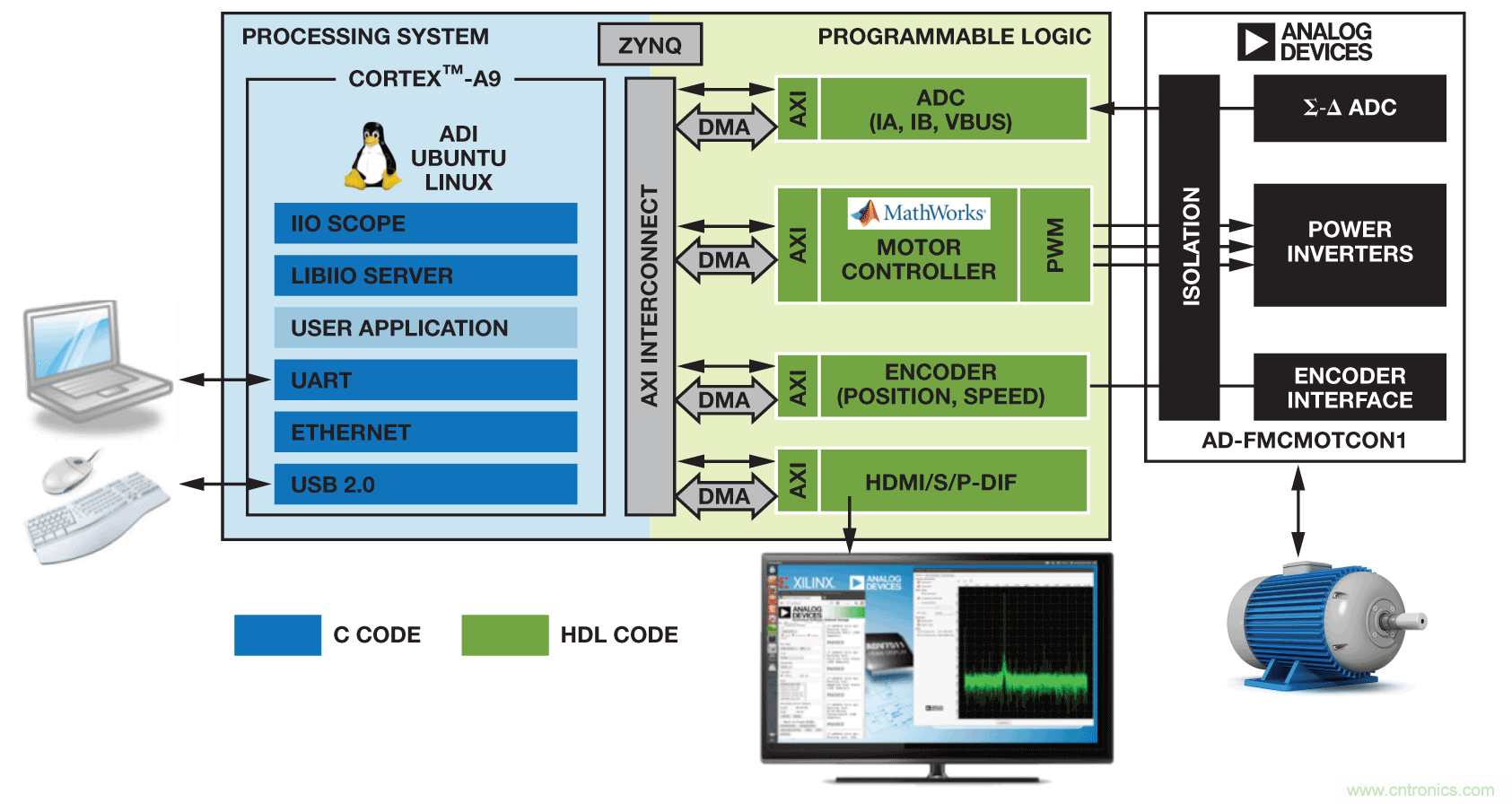

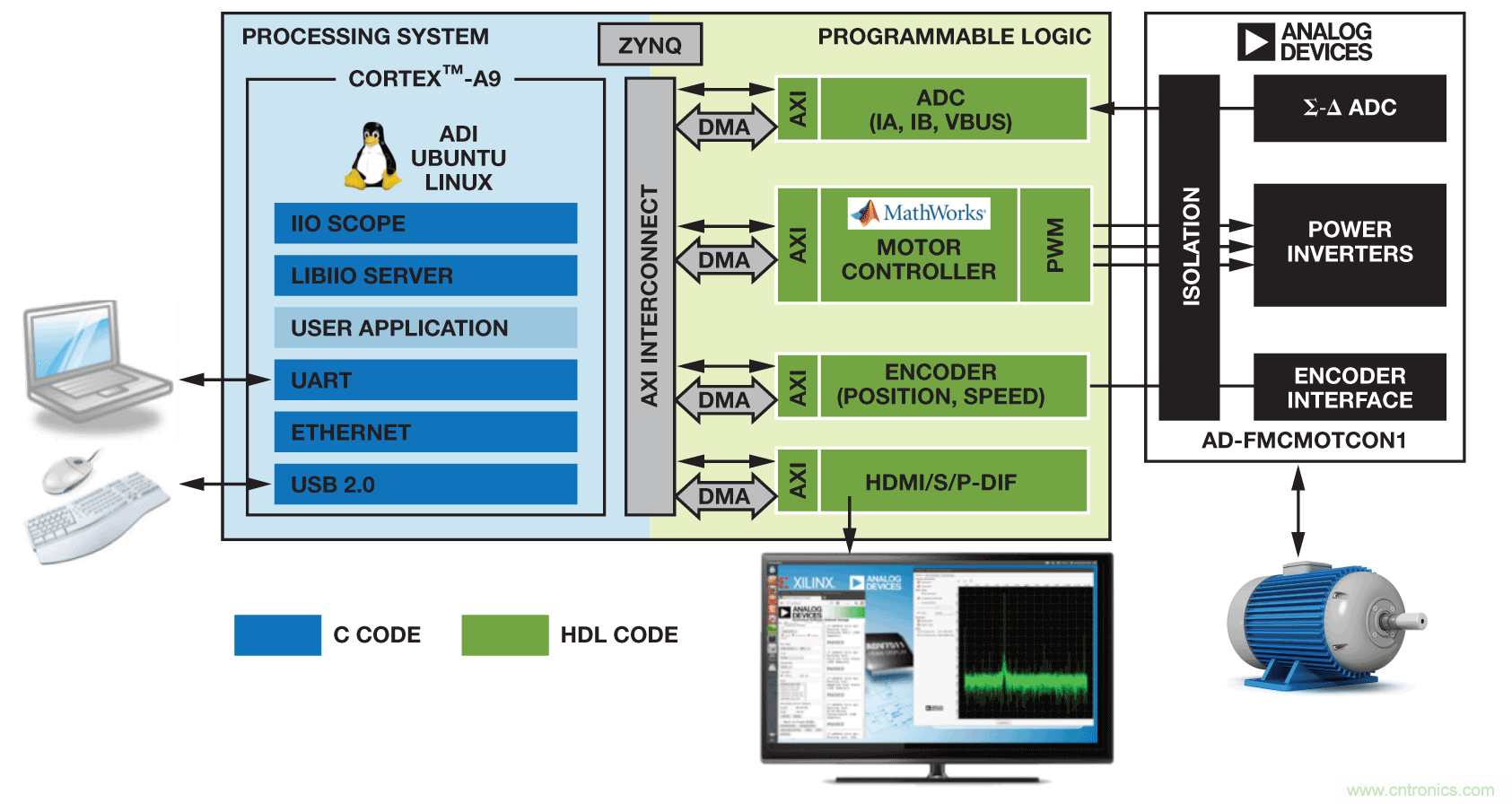

除了智能驅(qū)動(dòng)器套件以外�����,ADI 公司還提供完整的 Vivado 框架和 Linux 基礎(chǔ)設(shè)施以用于原型開(kāi)發(fā)和最終生產(chǎn)���。圖 12 顯示了支持智能驅(qū)動(dòng)器套件的 Zynq 基礎(chǔ)設(shè)施�。該高級(jí)框圖說(shuō)明了 ADI 參考設(shè)計(jì)在 Xilinx Zynq SoC 上是如何劃分的�。可編程邏輯實(shí)現(xiàn) IP內(nèi)核����,用于與 ADC、位置傳感器和電機(jī)驅(qū)動(dòng)級(jí)接口�。由 HDL 轉(zhuǎn)碼器生成的 HDL 代表電機(jī)控制算法,集成到 ADI 公司 IP 中����。所有 IP 都有低速 AXI-Lite 接口用于配置和控制,并有高速 AXIStreaming接口用于通過(guò) DMA 通道向軟件傳輸實(shí)時(shí)數(shù)據(jù)�。高速以太網(wǎng)接口可以利用 ARM 處理系統(tǒng)的硬 MAC 外設(shè)或可編程邏輯中的 Xilinx 以太網(wǎng) IP 實(shí)現(xiàn)。

ARM Cortex A9 處理系統(tǒng)運(yùn)行 ADI 公司提供的 Ubuntu Linux��,其中包括:與 ADI 公司智能驅(qū)動(dòng)器硬件接口所需的 Linux IIO 驅(qū)動(dòng)�,用于監(jiān)測(cè)和控制的IIO Oscilloscope(示波器)用戶空間應(yīng)用程序��,支持實(shí)時(shí)數(shù)據(jù)采集和通過(guò) TCP 控制系統(tǒng)的libiio服務(wù)器���,在遠(yuǎn)程計(jì)算機(jī)上運(yùn)行的客戶端,以及整合嵌入式轉(zhuǎn)碼器所生成 C代碼的可選用戶應(yīng)用程序����。

圖 12. ADI Linux 基礎(chǔ)設(shè)施

所有 ADI Linux 驅(qū)動(dòng)均基于 Linux 工業(yè) I/O(IIO)子系統(tǒng),其現(xiàn)已包括在所有主流 Linux 內(nèi)核中��。IIO Scope 是 ADI 公司開(kāi)發(fā)的一款開(kāi)源 Linux 應(yīng)用程序���,運(yùn)行在 Xilinx Zynq 中的雙核 ARMCortex A9 上�,能夠顯示連接到 Xilinx Zynq 平臺(tái)的 ADI FMC 卡所獲取的實(shí)時(shí)數(shù)據(jù)�。這些數(shù)據(jù)可以在時(shí)域中、頻域中或以星座圖的形式顯示����。支持以不同的常用文件格式(如逗號(hào)分隔值或.matMatlab 文件等)保存所捕獲的數(shù)據(jù)以供進(jìn)一步分析����。IIO Scope提供一個(gè)圖形用戶界面,用于更改或讀取 ADI FMC 卡的配置��。

libiio 服務(wù)器支持實(shí)時(shí)數(shù)據(jù)采集、通過(guò) TCP 控制系統(tǒng)以及運(yùn)行于遠(yuǎn)程計(jì)算機(jī)上的客戶端���。服務(wù)器運(yùn)行于 Linux 下的嵌入式目標(biāo)上���,通過(guò) TCP 管理目標(biāo)與遠(yuǎn)程客戶端之間的實(shí)時(shí)數(shù)據(jù)交換。IIO客戶端可以作為系統(tǒng)對(duì)象集成到 MATLAB 和 Simulink 原生應(yīng)用程序中�����。一路 HDMI 輸出用于在監(jiān)視器上顯示 Linux 界面��,鼠標(biāo)和鍵盤(pán)可通過(guò) USB 2.0 端口連接到系統(tǒng)����。

ADI 公司為智能驅(qū)動(dòng)器套件提供的 Linux 軟件和 HDL 基礎(chǔ)設(shè)施,連同 MathWorks 和 Xilinx 提供的工具�,非常適合開(kāi)發(fā)電機(jī)控制應(yīng)用原型。它們還包含適用于生產(chǎn)的組件�,可將其集成到最終控制系統(tǒng)中,從而減少?gòu)母拍畹缴a(chǎn)所需的時(shí)間和成本��。

結(jié)論

本文說(shuō)明了采用 FPGA 的現(xiàn)代電機(jī)控制系統(tǒng)的要求和趨勢(shì)����,以及為滿足這些約束條件和幫助實(shí)現(xiàn)更高效���、更精確的電機(jī)控制解決方案,MathWorks���、Xilinx 和 ADI 公司帶給市場(chǎng)的工具和系統(tǒng)���。通過(guò)將 MathWorks 基于模型的設(shè)計(jì)和自動(dòng)生成代碼工具與強(qiáng)大的Xilinx Zynq SoC、ADI 公司的隔離�、功率、信號(hào)調(diào)理和測(cè)量解決方案相結(jié)合����,電機(jī)驅(qū)動(dòng)系統(tǒng)的設(shè)計(jì)、驗(yàn)證��、測(cè)試和實(shí)現(xiàn)可以比以前更有效率����,進(jìn)而提高電機(jī)控制性能并縮短上市時(shí)間。ADI 公司智能驅(qū)動(dòng)器套件與 Avnet Zynq-7000 All Programmable SoC 配合使用�,為利用 MathWorks Simulink 設(shè)計(jì)的電機(jī)控制算法提供出色的原型開(kāi)發(fā)環(huán)境�。該智能驅(qū)動(dòng)器套件帶有一組參考設(shè)計(jì) 4,旨在為所有希望評(píng)估該系統(tǒng)的人士提供一個(gè)起點(diǎn),并且?guī)椭鷨?dòng)任何新的電機(jī)控制項(xiàng)目��。

參考電路

1. Hill, Tom. ""借助 Matlab 將電機(jī)驅(qū)動(dòng)遷移到 Zynq SoC 設(shè)計(jì)中���。." Xcell 雜志���,87 期,2014 年第二季度

2. O''''''''Sullivan, Dara, Jens Sorensen, 和 Anders Frederiksen. ""閉環(huán)電機(jī)控制中基于模型的設(shè)計(jì)工具." PCIM Europe, 2014.

3. Corradi, Dr. Giulio. ""頻率空間矢量調(diào)制—第一部分." 網(wǎng)絡(luò)���, 2012 年 10 月 4 日�。

4. AD-FMCMOTCON1-EBZ 用戶指南�����。

推薦閱讀: