【導讀】當今,數(shù)字時代的核心動力便是單片機,DSP ,PLD/ EDA ,以其各自的特點滿足了各種需要,推動著信息技術的快速發(fā)展。這里將對這三類電子產(chǎn)品分別加以介紹,并作比較和分析。

引言

信息技術正在快速發(fā)展,其應用已經(jīng)深入到各個領域各個方面。如今越來越多的電子產(chǎn)品向著智能化、微型化、低功耗方向發(fā)展,其中有的產(chǎn)品還需要實時控制和信號處理。電子系統(tǒng)的復雜性在不斷增加,它迫切要求電子設計技術也有相應的變革和飛躍。使用純SSI 數(shù)字電路設計系統(tǒng)工作量大, 靈活性低, 而且系統(tǒng)可靠性差。廣泛使用單片機(MCU) 設計系統(tǒng)克服了純SSI 數(shù)字電路系統(tǒng)許多不可逾越的困難,是一個具有里程碑意義的飛躍。而DSP以其極強的信號處理功能贏得了廣闊的市場,得到了廣泛地應用。近年來,PLD 器件迅速發(fā)展,尤其是CPLD/ FPGA 向深亞微米領域進軍,PLD 器件得到了廣泛應用,以CPLD/ FPGA 為物質(zhì)基礎的EDA 技術誕生了。它具有電子技術高度智能化、自動化的特點,打破了軟硬件最后的屏障,使得硬件設計如同軟件設計一樣簡單。它作為一種創(chuàng)新技術正在改變著數(shù)字系統(tǒng)的設計方法、設計過程和設計觀念。單片機,DSP ,PLD/ EDA 以其各自的特點滿足了各種需要,正從各個領域各個層面改變著世界,它們已經(jīng)成為數(shù)字時代的核心動力,推動著信息技術的快速發(fā)展。

以下,我們將對單片機,DSP,PLD/ EDA 分別加以介紹,并作比較和分析。

單片機

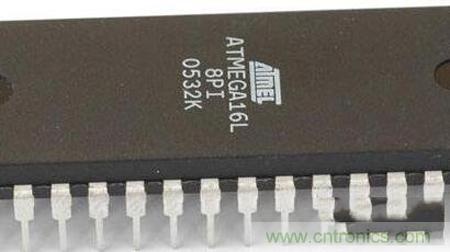

單片機是集成了CPU ,ROM ,RAM 和I/ O 口的微型計算機。它有很強的接口性能,非常適合于工業(yè)控制,因此又叫微控制器(MCU) 。它與通用處理器不同,它是以工業(yè)測控對象、環(huán)境、接口等特點出發(fā),向著增強控制功能,提高工業(yè)環(huán)境下的可靠性、靈活方便地構成應用計算機系統(tǒng)的界面接口的方向發(fā)展。所以,單片機有著自己的特點。

品種齊全,型號多樣

自從INTEL 推出51 系列單片機,許多公司對它做出改進,發(fā)展成為增強型51 系列,而且新的單片機類型也不斷涌現(xiàn)。如MOTOROLA 和PHIL IPS 均有幾十個系列,幾百種產(chǎn)品。CPU 從8 ,16 ,32 到64 位,多采用RISC 技術,片上I/O 非常豐富,有的單片機集成有A/ D , “看門狗”,PWM ,顯示驅動,函數(shù)發(fā)生器,鍵盤控制等,它們的價格也高低不等,這樣極大地滿足了開發(fā)者的選擇自由。

低電壓和低功耗

隨著超大規(guī)模集成電路的發(fā)展,NMOS 工藝單片機被CMOS代替,并開始向HMOS 過渡。供電電壓由5V 降到3V ,2V 甚至到1V ,工作電流由mA 降至μA ,這在便攜式產(chǎn)品中大有用武之地。

DSP芯片

DSP 又叫數(shù)字信號處理器。顧名思義,DSP 主要用于數(shù)字信號處理領域,非常適合高密度,重復運算及大數(shù)據(jù)容量的信號處理?,F(xiàn)在已經(jīng)廣泛應用于通信、便攜式計算機和便攜式儀表、雷達、圖像、航空、家用電器、醫(yī)療設備等領域,常見的手機、數(shù)字電視和數(shù)碼相機都離不開DSP。DSP用于手機和基站中為移動通信的發(fā)展做出重要貢獻,將在2. 5G和3G中扮演重要角色??梢哉f,DSP已經(jīng)融入到生活的方方面面。

DSP 相對于一般微處理器作了很大的擴充和增強,主要是:

a) 修正的哈佛結構,多總線技術以及流水線結構。將程序與數(shù)據(jù)存儲器分開,使用多總線,取指令和取數(shù)據(jù)同時進行,以及流水線技術,這使得速度有了較大的提高。

b) 硬件乘法器以及特殊指令。這是區(qū)別于一般微處理器的重要標志。一般微處理器用軟件實現(xiàn)乘法,逐條執(zhí)行指令,速度慢。而DSP 依靠硬件乘法器單周期完成乘法運算,而且還具有專門的信號處理指令,如TM320 系列的FIRS ,LMS ,MACD 指令等。

EDA 技術

當今電子系統(tǒng)的復雜性在不斷增加,而電子產(chǎn)品的更新?lián)Q代越來越快,傳統(tǒng)的設計方法難以適應。隨著計算機技術的發(fā)展,ECAD 在某種程度上減輕了設計人員的工作壓力,但其智能化、自動化水平仍不盡人意。于是EDA 技術作為一種全新的技術誕生了。它正改變著數(shù)字系統(tǒng)和設計方法,設計過程和設計觀念。

EDA(即Electronic Design AutomaTIon) 即電子設計自動化,它是以計算機為工具,在EDA 軟件平臺上,對用硬件描述語言HDL 完成的設計文件自動地邏輯編譯、邏輯化簡、邏輯分割、邏輯綜合及優(yōu)化、邏輯布局布線、邏輯仿真,直至對于特定目標芯片進行適配編譯、邏輯影射和編程下載等。設計者只需用HDL 語言完成系統(tǒng)功能的描述,借助EDA 工具就可得到設計結果,將編譯后的代碼下載到目標芯片就可在硬件上實現(xiàn)。這里的目標芯片就是PLD 器件( FPGA/CPLD) 。FPGA/ CPLD 是EDA 技術的物質(zhì)基礎,這兩者是分不開的??梢哉f沒有PLD 器件,EDA 技術就成為無源之水。

EDA 技術作為一種現(xiàn)代電子系統(tǒng)開發(fā)方式,具有兩方面特點。

修改軟件程序即可改變硬件

由于FPGA/ CPLD 可以通過軟件編程對該硬件的結構和工作方式進行重構,修改軟件程序就相當于改變了硬件,這是非常有用的。軟件可以使用自頂向下的設計方案,而且可以多個人分工并行工作,這些年來IP 核產(chǎn)業(yè)的崛起,將若干軟核結合起來就可以構成一個完整的系統(tǒng),這一切極大地縮短了開發(fā)周期和上市時間,有利于在激烈的市場競爭中搶占先機。

速度快,可靠性高

MCU 和DSP 都是通過串行執(zhí)行指令來實現(xiàn)特定功能,不可避免低速,而FPGA/ CPLD 則可實現(xiàn)硬件上的并行工作,在實時測控和高速應用領域前景廣闊;另一方面,F(xiàn)PGA/CPLD 器件在功能開發(fā)上是軟件實現(xiàn)的,但物理機制卻和純硬件電路一樣,十分可靠。而MCU 和DSP芯片在強干擾條件下,尤其是強電磁干擾下,很可能越出正常的工作流程,出現(xiàn)PC 跑飛現(xiàn)象。EDA 高可靠性正好克服了它們這一先天不足。

結束語

單片機,DSP和FPGA/ CPLD 各具特色,滿足了不同需要,已經(jīng)成為數(shù)字時代的核心動力。為了充分發(fā)揮它們的優(yōu)勢,三者結合成為一個新的發(fā)展趨勢。

MCU 與DSP的結合

MCU 價格底,能很好地完成通信和智能控制的任務,但信號處理能力差。DSP恰好相反。把兩者結合,能滿足同時需要智能控制和數(shù)字信號處理的場合,如蜂窩電話,無繩網(wǎng)絡產(chǎn)品等,這有利于減小體積,降低功耗和成本。

DSP 和FPGA/ CPLD 的結合

由于FPGA/ CPLD 兼有串/ 并行工作方式,高速度和寬口徑適用性等特點,將DSP與FPGA 集成在一個芯片上,可實現(xiàn)寬帶信號處理,極大地提高信號處理速度。另外,F(xiàn)PGA可以進行硬件重構,功能擴展或性能改善非常容易??傊瑔纹瑱C,DSP , PLD/ EDA 極大地推動了信息技術的發(fā)展。要作為一名工程師,必須掌握從系統(tǒng)設計級、電路設計級到物理實現(xiàn)級整個過程分析設計能力,能熟練使用新器件,新的開發(fā)工具,并不斷更新觀念,只有這樣,才能適應時代發(fā)展,才能把握現(xiàn)在,創(chuàng)造未來!

PLD入門須知的幾點小常識!

PLD是可編程邏輯器件(Programable Logic Device)的簡稱,F(xiàn)PGA是現(xiàn)場可編程門陣列(Field Programable Gate Array)的簡稱,兩者的功能基本相同,只是實現(xiàn)原理略有不同,所以我們有時可以忽略這兩者的區(qū)別,統(tǒng)稱為可編程邏輯器件或PLD/FPGA。

PLD是電子設計領域中最具活力和發(fā)展前途的一項技術,它的影響絲毫不亞于70年代單片機的發(fā)明和使用。

PLD能做什么呢?可以毫不夸張的講,PLD能完成任何數(shù)字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用PLD來實現(xiàn)。PLD如同一張白紙或是一堆積木,工程師可以通過傳統(tǒng)的原理圖輸入法,或是硬件描述語言自由的設計一個數(shù)字系統(tǒng)。通過軟件仿真,我們可以事先驗證設計的正確性。在PCB完成以后,還可以利用PLD的在線修改能力,隨時修改設計而不必改動硬件電路。使用PLD來開發(fā)數(shù)字電路,可以大大縮短設計時間,減少PCB面積,提高系統(tǒng)的可靠性。

PLD的這些優(yōu)點使得PLD技術在90年代以后得到飛速的發(fā)展,同時也大大推動了EDA軟件和硬件描述語言(HDL)的進步。

如何使用PLD呢?其實PLD的使用很簡單,學習PLD比學習單片機要簡單的多,有數(shù)字電路基礎,會使用計算機,就可以進行PLD的開發(fā)。不熟悉PLD的朋友,可以先看一看可編程邏輯器件的發(fā)展歷程。

開發(fā)PLD需要了解兩個部分:1.PLD開發(fā)軟件 2.PLD本身

1.PLD開發(fā)軟件

由于PLD軟件已經(jīng)發(fā)展的相當完善,用戶甚至可以不用詳細了解PLD的內(nèi)部結構,也可以用自己熟悉的方法:如原理圖輸入或HDL語言來完成相當優(yōu)秀的PLD設計。所以對初學者,首先應了解PLD開發(fā)軟件和開發(fā)流程。了解PLD的內(nèi)部結構,將有助于提高我們設計的效率和可靠性。

如何獲得PLD開發(fā)軟件軟件呢?

許多PLD公司都提供免費試用版或演示版(當然商業(yè)版大都是收費的),例如:可以免

費從上下載Altera公司的 QuartusII (web版),或向其代理商索取這套軟件。Xilinx 公司也提供免費軟件:ISE WebPack,這套可以從xilinx網(wǎng)站下載。LatTIce 提供isplever Base版下載,Actel等公司也都有類似的免費軟件提供。以上免費軟件都需要在網(wǎng)上注冊申請LISENCE文件,如果您對軟件的安裝還有不清楚,請仔細閱讀相關網(wǎng)頁上的說明。 通常這些免費軟件已經(jīng)能夠滿足一般設計的需要,當然,要想軟件功能更強大一些,只能購買商業(yè)版軟件。

如果你打算使用VHDL或Verilog HDL硬件描述語言來開發(fā)PLD/FPGA,通常還需要使用一些專業(yè)的HDL開發(fā)軟件,這是因為FPGA廠商提供的軟件的HDL綜合能力一般都不是很強,需要其他軟件來配合使用。

對于PLD產(chǎn)品,一般分為:基于乘積項(Product-Term)技術,EEPROM(或Flash)工藝的中小規(guī)模PLD,以及基于查找表(Look-Up table)技術,SRAM工藝的大規(guī)模PLD/FPGA。

EEPROM工藝的PLD(CPLD)密度小,多用于5,000門以下的小規(guī)模設計,適合做復雜的組合邏輯,如譯碼。SRAM工藝的PLD(FPGA),密度高,觸發(fā)器多,多用于10,000門以上的大規(guī)模設計,適合做復雜的時序邏輯,如數(shù)字信號處理和各種算法。

目前有多家公司生產(chǎn)CPLD/FPGA,最大的三家是:ALTERA,XILINX,LatTIce, 您可以參閱PLD廠商欄目獲得更多信息

2.PLD/FPGA的分類和使用

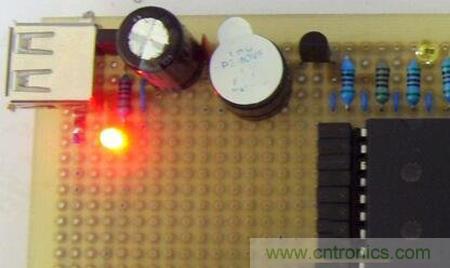

在PLD/FPGA開發(fā)軟件中完成設計以后,軟件會產(chǎn)生一個最終的編程文件(如 .pof )。如何將編程文件燒到PLD芯片中去呢?

1.對于基于乘積項(Product-Term)技術,EEPROM(或Flash)工藝的PLD(如Altera的MAX系列,LatTIce的大部分產(chǎn)品,Xilinx的XC9500,Coolrunner系列), 廠家提供編程電纜,電纜一端裝在計算機的并行打印口上,另一端接在PCB板上的一個十芯插頭,PLD芯片有四個管腳(編程腳)與插頭相連。

它向系統(tǒng)板上的器件提供配置或編程數(shù)據(jù),這就是所謂的在線可編程。Byteblaster使用戶能夠獨立地配置PLD器件,而不需要編程器或任何其它編程硬件。編程電纜可以向代理商購買,也可以根據(jù)廠家提供的編程電纜的原理圖自己制作,成本僅需一,二十元。 早期的PLD是不支持ISP的,它們需要用編程器燒寫。目前的PLD都可以用ISP在線編程,也可用編程器編程。這種PLD可以加密,并且很難解密,所以常常用于單板加密。

2.對于基于查找表(LUT,Look-Up table)技術,SRAM工藝的FPGA(如Altera的所有FPGA,如ACEX,Cyclone,Stratix系列,Xilinx的所有FPGA,如Spartan,Virtex系列,Lattice的EC/ECP系列等),由于SRAM工藝的特點,掉電后數(shù)據(jù)會消失,因此調(diào)試期間可以用下載電纜配置PLD器件,調(diào)試完成后,需要將數(shù)據(jù)固化在一個專用的EEPROM中(用通用編程器燒寫,或者用專用配置芯片),上電時,由這片配置EEPROM先對FPGA加載數(shù)據(jù),十幾個毫秒到幾百個毫秒后,F(xiàn)PGA即可正常工作。亦可由CPU配置FPGA。但SRAM工藝的PLD一般不可以直接加密。

3.還有一種反熔絲(Anti-fuse)技術的FPGA,如Actel,Quicklogic的部分產(chǎn)品就采用這種工藝。但這種的PLD是不能重復擦寫,需要使用專用編程器,所以開發(fā)過程比較麻煩,費用也比較昂高。但反熔絲技術也有許多優(yōu)點:布線能力更強,系統(tǒng)速度更快,功耗更低,同時抗輻射能力強,耐高低溫,可以加密,所以在一些有特殊要求的領域中運用較多,如軍事及航空航天。

為了解決反熔絲FPGA不可重復擦寫的問題,Actel等公司在90年代中后期開發(fā)了基于Flash技術的FPGA,如ProASIC系列,這種FPGA不需要配置,數(shù)據(jù)直接保存在FPGA芯片中,用戶可以改寫(但需要10幾伏的高電壓)。

隨著技術的發(fā)展,在2004年以后,一些廠家推出了一些新的PLD和FPGA,這些產(chǎn)品模糊了PLD和FPGA的區(qū)別。例如Altera最新的MAXII系列PLD,這是一種基于FPGA(LUT)結構,集成配置芯片的PLD,在本質(zhì)上它就是一種在內(nèi)部集成了配置芯片的FPGA,但由于配置時間極短,上電就可以工作,所以對用戶來說,感覺不到配置過程,可以傳統(tǒng)的PLD一樣使用,加上容量和傳統(tǒng)PLD類似,所以altera把它歸作PLD。 還有像Lattice的XP系列FPGA,也是使用了同樣的原理,將外部配置芯片集成到內(nèi)部,在使用方法上和PLD類似,但是因為容量大,性能和傳統(tǒng)FPGA相同,也是LUT架構,所以Lattice仍把它歸為FPGA。