【導(dǎo)讀】電動(dòng)機(jī)總體上消耗了很大一部分的全球電力,從而帶來了更復(fù)雜的電機(jī)控制設(shè)計(jì),這些設(shè)計(jì)使用基于傳感器和無傳感器反饋回路和先進(jìn)的算法�,實(shí)現(xiàn)更精密的控制和更高的電機(jī)效率����。

電動(dòng)機(jī)總體上消耗了很大一部分的全球電力。市場(chǎng)研究機(jī)構(gòu)IHS Technology指出����,96%的電機(jī)壽命周期成本是純電力成本。監(jiān)管機(jī)構(gòu)為它們實(shí)施了更嚴(yán)格的能源標(biāo)準(zhǔn)�。而且,制造商正在審查其在設(shè)備總體成本(TCO)中所占的巨大比率�。這帶來了更復(fù)雜的電機(jī)控制設(shè)計(jì)���,這些設(shè)計(jì)使用基于傳感器和無傳感器反饋回路和先進(jìn)的算法�����,實(shí)現(xiàn)更精密的控制和更高的電機(jī)效率�����。

電機(jī)設(shè)計(jì)人員還必需支持不斷變化的工業(yè)控制標(biāo)準(zhǔn)和技術(shù)�����,同時(shí)提供關(guān)鍵性系統(tǒng)功能以確保安全性��、可調(diào)節(jié)性和可靠性����。要滿足能效和系統(tǒng)級(jí)功能需求增強(qiáng)的雙目標(biāo),需要充分的算法處理能力和靈活的可調(diào)節(jié)系統(tǒng)架構(gòu)�。基于閃存的非易失性安全低功耗系統(tǒng)級(jí)芯片(SoC)FPGA器件通過提供必需的功率�����,同時(shí)結(jié)合固有和分級(jí)的安全性和可靠性,能夠同時(shí)應(yīng)對(duì)這兩個(gè)挑戰(zhàn)����,不但可保護(hù)物聯(lián)網(wǎng)(IoT)應(yīng)用的通信,并且具有在各種多軸或高RPM應(yīng)用中快速��、輕易地從小占位面積轉(zhuǎn)換至功能豐富的定制電機(jī)設(shè)計(jì)的可調(diào)節(jié)性�����。

挑戰(zhàn)

雖然傳統(tǒng)設(shè)計(jì)使用簡(jiǎn)單的標(biāo)量控制����、高效電機(jī)在所有轉(zhuǎn)矩和速度范圍使用磁場(chǎng)定向控制(FOC),以顯著提升效率��。由于采用電流控制�,F(xiàn)OC還可以根據(jù)應(yīng)用需求來優(yōu)化功率逆變器電路和電機(jī)占位面積。它使用反饋回路�����,帶有或不帶有傳感器��,以及復(fù)雜算法來調(diào)整關(guān)鍵的電機(jī)動(dòng)作參數(shù)�,包括速度�、位置或角度��、轉(zhuǎn)矩��、電流及通量����。傳統(tǒng)上��,單軸或雙軸設(shè)計(jì)利用微控制器(MCU)和DSP處理算法����,但其處理能力無法跟上日益增長(zhǎng)的多軸或高旋轉(zhuǎn)電機(jī)性能需求。此外��,現(xiàn)時(shí)的情況日趨復(fù)雜�,因?yàn)槌穗姍C(jī)控制的效率外,我們很多時(shí)候還要關(guān)注其他問題���,尤其是聯(lián)網(wǎng)的工廠�,現(xiàn)今的物聯(lián)網(wǎng)(IoT)環(huán)境對(duì)于安全通信帶來了重要的要求—這是基于閃存的FPGA架構(gòu)適宜處理的挑戰(zhàn)����。

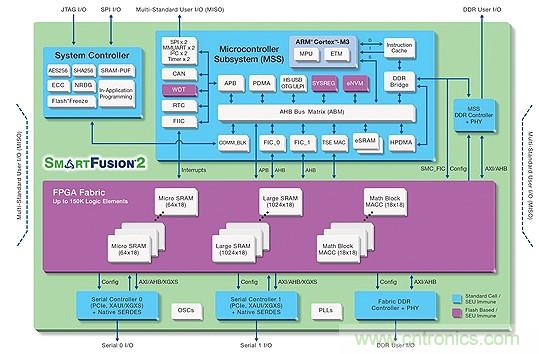

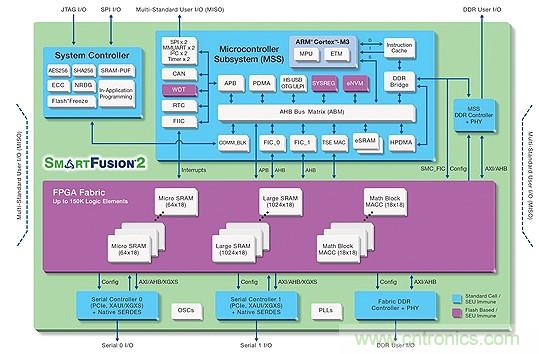

圖1:可以用于電機(jī)控制和監(jiān)控功能,基于閃存的SoC FPGA架構(gòu)示例。

在電機(jī)控制設(shè)計(jì)的功率電子方面�,存在著從絕緣柵雙極晶體管(IGBT)器件轉(zhuǎn)向碳化硅(SiC)功率MOSFET器件的遷移,SiC解決方案提供更高的帶隙以提升冷卻性能(因而可以使用較小�����、較廉價(jià)的散熱片)����、更好的熱傳導(dǎo)性以提高功率密度,以及更高的開關(guān)頻率(超過100kHz)�����,因而可以在逆變器級(jí)使用更小的磁件��,有助于降低客戶的TCO�����。

在控制端�,DSP和MCU器件在較高開關(guān)頻率場(chǎng)合的表現(xiàn)不佳,某些DSP可以優(yōu)化幾個(gè)用于高頻開關(guān)的通道����,但是���,它們?nèi)匀蝗狈焖龠m應(yīng)需求變化, 以及增添更多脈寬調(diào)制(PWM)通道來控制功率電子級(jí)(事實(shí)上�,這通常卸載至FPGA器件)的能力。ASIC和ASSP器件具有相同的靈活性和擴(kuò)展性難題��。

基于閃存的FPGA器件提供比基于MCU/DSP解決方案的更高性能���,用于高速、低遲滯算法處理�,同時(shí)集成附加的系統(tǒng)功能以進(jìn)一步提升TCO。設(shè)計(jì)人員能夠使用基于閃存的FPGA來調(diào)節(jié)至更高的開關(guān)頻率和更多的PWM通道����,以匹配功率電子裝置,從而支持超越MCU/DSP的功能�����。

圖1所示為帶有ARM Cortex-M3微控制器的基于閃存SoC FPGA器件�,可以用于電機(jī)控制和監(jiān)控功能。這個(gè)FPGA用于電機(jī)控制功能的硬件加速����,以提升性能和設(shè)計(jì)靈活性����。電機(jī)控制算法可以運(yùn)行在FPGA器件����,以實(shí)現(xiàn)更快速的并行處理,它具有智能分區(qū)�,以確保微控制器子系統(tǒng)中的所有通信協(xié)議處理都不會(huì)影響到在FPGA器件內(nèi)運(yùn)行的電機(jī)控制算法計(jì)算。

即插即用IP模塊化套件�,經(jīng)定制實(shí)施所有必需的數(shù)學(xué)電機(jī)模型,完善了今天的FPGA解決方案��。開發(fā)人員可以確定哪一個(gè)IP模塊用于FPGA架構(gòu)中的硬件加速�����,從而能夠應(yīng)對(duì)全系列算法處理挑戰(zhàn)��。這些解決方案確保低功耗運(yùn)作���,同時(shí)推動(dòng)開發(fā)人員優(yōu)化其系統(tǒng)以使用加快上市速度的簡(jiǎn)化設(shè)計(jì)過程���,同時(shí)提供滿足不斷演進(jìn)之需求的靈活性和可擴(kuò)展性,從而實(shí)現(xiàn)高可靠性���、高安全性和保密功能�。

低功耗運(yùn)作

用于電機(jī)控制設(shè)計(jì)的FPGA器件必需同時(shí)減小靜態(tài)功率和總體功率,特別是在高頻率和高溫下�����。與必需在上電期間從外部ROM進(jìn)行配置的使用六個(gè)晶體管的SRAM單元的FPGA相比��,具有內(nèi)置單晶體管閃存單元的FPGA更具有優(yōu)勢(shì)���?�;陂W存的最新FPGA解決方案還使用了全面的方法來最大限度地降低功耗, 包括工藝技術(shù)���、架構(gòu)和可配置邏輯設(shè)計(jì)���, 以及嵌入式功能,包括增強(qiáng)的M3 MCU�、5G SERDES、DDR2/3�、TSE、DSP模塊��, 以及專用功率模式。與基于SRAM的FPGA解決方案相比�����,這種方法可降低50%總體功率和降低10%靜態(tài)功率����。

可靠性、安全性和保密性

正常情況下�����,在實(shí)施確定性定時(shí)很重要的電機(jī)控制和網(wǎng)絡(luò)功率方面��,F(xiàn)PGA器件更為可靠����。微控制器的定時(shí)變化可能高達(dá)數(shù)毫秒,而FPGA器件的定時(shí)變化則少于數(shù)納秒��。

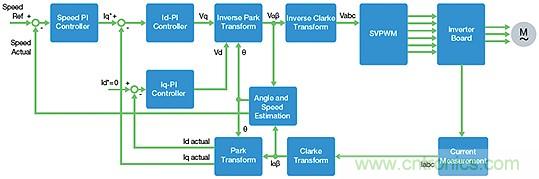

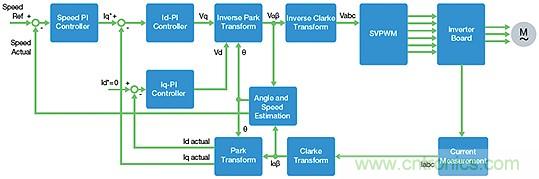

圖2:IP模塊推動(dòng)共用FPGA資源的分享����,實(shí)現(xiàn)最高效的芯片利用率。

實(shí)現(xiàn)安全性的最佳選擇是基于閃存FPGA器件��,而不是基于SRAM的FPGA器件,原因在于它們?cè)诜且资源鎯?chǔ)器中儲(chǔ)存配置信息—比特流永遠(yuǎn)不會(huì)在啟動(dòng)時(shí)暴露�����。它們還具有單粒子翻轉(zhuǎn)(SEU)免疫能力��,SEU可以改變配置SRAM的內(nèi)容���。某些基于閃存的FPGA器件具有保護(hù)超連接工業(yè)IoT系統(tǒng)避免克隆�、篡改和其它惡意攻擊的關(guān)鍵存儲(chǔ)能力��,還可以用作信任根器件�。為滿足安全需求,這些FPGA器件具有物理反克隆等功能(physically unclonable function,PUF)�����,其中公匙/私匙方案可以用于通過公匙基礎(chǔ)設(shè)施(PKI)實(shí)施M2M認(rèn)證�。其它功能包括加密加速器�、隨機(jī)數(shù)字發(fā)生器、保護(hù)CPU/DSP內(nèi)核的硬件防火墻頭�����,以及差分功率分析(DPA)防御措施,這些功能合并起來���,在整個(gè)系統(tǒng)中實(shí)施分層安全性以保護(hù)硬件和數(shù)據(jù)����。

通過模塊化方法簡(jiǎn)化設(shè)計(jì)

模塊化和性能導(dǎo)向IP模塊套件可以通過即插即用簡(jiǎn)單性來實(shí)施算法�����。設(shè)計(jì)可以輕易在多個(gè)平臺(tái)遷移�,以加快上市速度。所有IP模塊均已在實(shí)際硬件上通過模擬測(cè)試�����, 以確保精密的轉(zhuǎn)矩輸出�����,并可輕易集成以創(chuàng)建任務(wù)專用模塊�����。各個(gè)模塊促進(jìn)了共用FPGA資源的分享,以實(shí)現(xiàn)最高效的芯片利用率(圖2)����。

這款I(lǐng)P套件還包括所有基礎(chǔ)構(gòu)件,包括Clarke和Park轉(zhuǎn)換��、用于控制環(huán)路反饋的比例積分(PI)控制器����,以及空間矢量PWM(SVPWM)。

靈活性和可擴(kuò)展性

模塊化IP套件還可以簡(jiǎn)化定制和擴(kuò)展���,以支持不同的多軸電機(jī)或高RPM解決方案的組合��,同時(shí)滿足不斷演進(jìn)的技術(shù)標(biāo)準(zhǔn)��。IP模塊越緊湊(比如整個(gè)套件小于10,000個(gè)邏輯組件)�����,以便需要越多資源來支持集成需求��。根據(jù)需求而定,在FPGA器件上運(yùn)行的IP套件可以調(diào)節(jié)以驅(qū)動(dòng)兩個(gè)無刷直流(BLDC)/步進(jìn)電機(jī)通道至六軸解決方案����,或者擴(kuò)展電機(jī)性能至超過70,000RPM�。一個(gè)調(diào)節(jié)多軸FOC控制的方法���,是在器件中各個(gè)FOC環(huán)路實(shí)行時(shí)分多工�,使得每個(gè)電機(jī)可以單獨(dú)控制�,從而滿足不同的參考速度和轉(zhuǎn)矩需求。在FPGA架構(gòu)中實(shí)施各種功能�����,騰出微處理器子系統(tǒng)用于運(yùn)行通信協(xié)議堆棧�,提供人機(jī)接口,或者其它任務(wù)����。

電機(jī)的設(shè)計(jì)人員必需滿足強(qiáng)制的能量要求, 同時(shí)確保系統(tǒng)能夠調(diào)節(jié)和適應(yīng)�����?;陂W存的SoC FPGA器件提供了吸引力日益增強(qiáng)的產(chǎn)品以替代DSP、MCU�����、ASIC 和ASSP器件,結(jié)合了必需的處理能力及硬件和軟件可編程性����,以及電路板選項(xiàng),用于加速和智能分區(qū)功能�����?�;陂W存的FPGA器件增添了固有的安全性��,能夠用作連接工廠中安全I(xiàn)oT通信的信任根�。

推薦閱讀: