【導(dǎo)讀】本設(shè)計實例討論了工程師在設(shè)計PCB上的PAM-4PHY 通道時應(yīng)遵循的關(guān)鍵實踐。實現(xiàn)50Gbps PAM-4 PHY鏈路時必須嚴格要求,確保在高速收發(fā)器之間實現(xiàn)穩(wěn)定的通信。

隨著物聯(lián)網(wǎng)(IoT)和5G移動寬帶應(yīng)用的興起,預(yù)計總體數(shù)據(jù)流量將會迅猛增長,400千兆以太網(wǎng)(400GbE)作為新一代有線通信標準,能夠有力支持這一趨勢。在400GbE通信的實施中,其電氣接口在8通道上傳輸4電平脈沖幅度調(diào)制(PAM-4)信令。每通道50Gbps,總共8個通道結(jié)合起來,使以太網(wǎng)的總帶寬可以達到400Gbps。IEEE802.3bs定義了使用50Gbps(即25GBaud)PAM-4信令的400GbE的電氣規(guī)范。

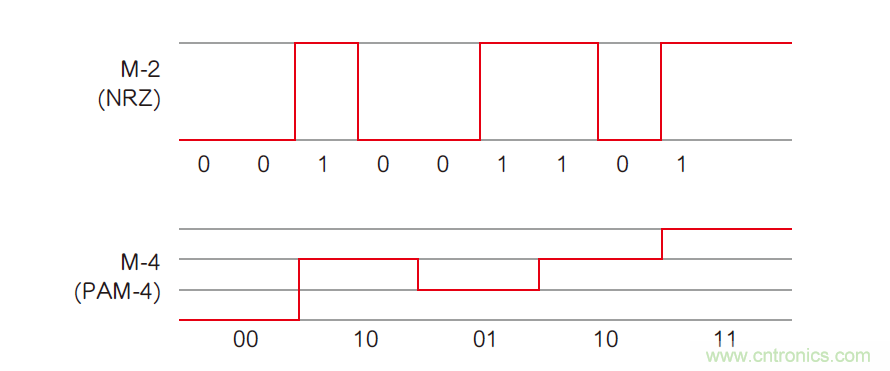

PAM-4具有4種數(shù)字幅度電平,如圖1所示。與NRZ相比,PAM-4的優(yōu)勢是每個電平或符碼都包含兩個信息比特,在相同的波特率下,吞吐量是NRZ的兩倍。

圖1:NRZ與PAM-4的對比。在相同的波特率下,PAM-4的吞吐量是NRZ的兩倍。

考慮電源完整性的關(guān)鍵設(shè)計實現(xiàn)

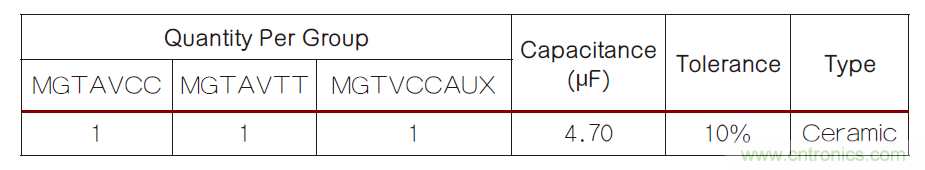

一旦PDN上的開關(guān)噪聲耦合至收發(fā)器集成電路的電源層,傳輸信號中將感應(yīng)到抖動,這可能會增加接收集成電路中的比特誤碼率。為了讓噪聲紋波保持在較小水平,符合設(shè)計規(guī)范,PDN阻抗應(yīng)低于目標阻抗。目標阻抗由公式1決定。

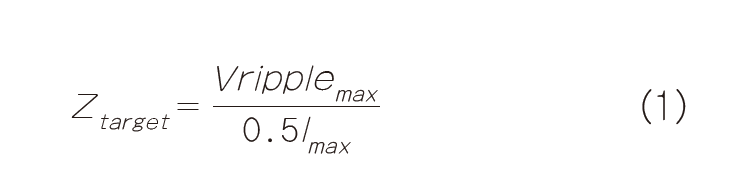

為了最大限度降低PDN阻抗,要特別關(guān)注去耦電容、互連電感和電源平面電容等印刷電路板元件。去耦電容應(yīng)安裝在靠近高速收發(fā)器電源引腳的位置,以減少PDN阻抗,進而在噪聲耦合進收發(fā)器集成電路封裝電源平面之前,減小來自外部源(如穩(wěn)壓器和其它開關(guān)集成電路)的噪聲。高速收發(fā)器電源引腳的噪聲將低于10mVpp。為Xilinx FPGA上的高速收發(fā)器電源引腳推薦的最小電容數(shù)量如圖2所示,在靠近每個高速收發(fā)器電源組(即MGTAVCC、MGTAVTT和MGTVCCAUX)的位置都安裝了1個4.7uF陶瓷電容器。

圖2:為Xilinx FPGA上的高速收發(fā)器電源引腳推薦的電容數(shù)量。

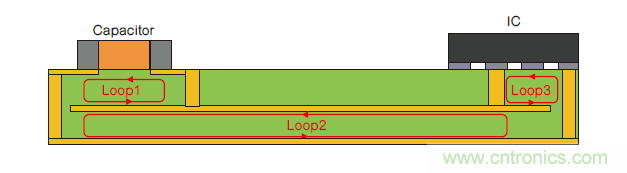

當互連電感減少時,PDN阻抗會相應(yīng)降低。互連電感主要由走線(連接電容器的貼裝焊盤與過孔)的寄生電感引起。根據(jù)圖3所示的印刷電路板的剖面圖,每個互連回路(圖中標示為回路1、2、3)中都會形成互連電感。去耦電容器要盡量安裝在靠近集成電路電源引腳的位置,以最大限度減小互連電感。

圖3:印刷電路板內(nèi)的互連電感。

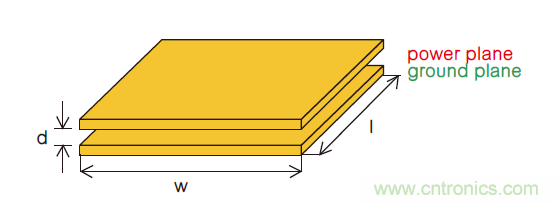

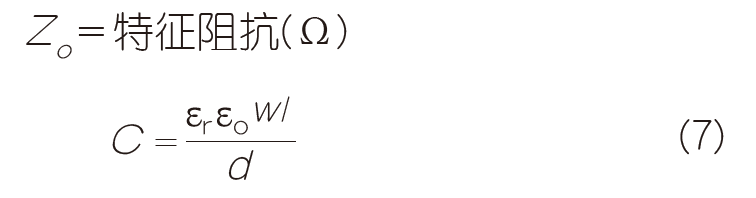

當印刷電路板疊層中的電源平面和接地面之間形成的平面電容增加時,PDN阻抗會降低。參見圖4所示的平面電容基礎(chǔ)模型和公式2,通過減少平行面之間的厚度,增加電源平面與接地面之間并行面的面積,或使用具有較大介電常數(shù)的基片,電容會相應(yīng)升高。

圖4:印刷電路板疊層中的平面電容基礎(chǔ)模型。

考慮信號完整性的關(guān)鍵設(shè)計實現(xiàn)

根據(jù)指南,印刷電路板上走線長度達到8英寸的PAM-4通道在14GHz和28GHz分別具有低于10dB和20dB的插入損耗,從而在收發(fā)器之間實現(xiàn)無縫數(shù)據(jù)通信。下面我們將從信號完整性的視角討論7個關(guān)鍵設(shè)計實踐。

1.為印刷電路板基片選擇低損耗材料

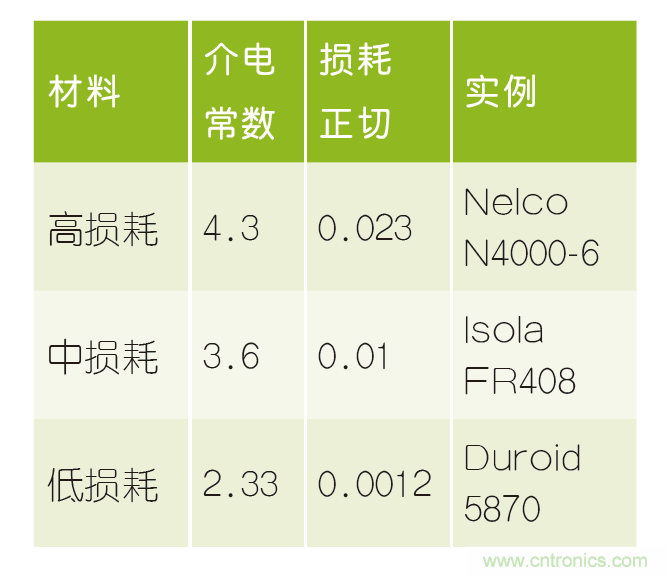

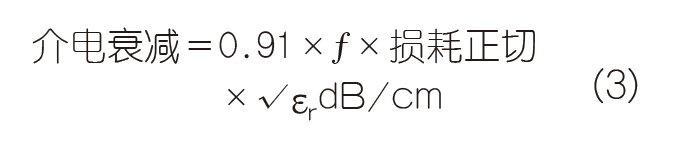

根據(jù)介電特性(例如損耗正切和介電損耗),印刷電路板基片介電材料可以分為3類。如表1表示,高損耗材料(如Nelco N4000-6)的損耗正切值超過0.02,介電常數(shù)超過4;中等損耗材料(如Isola FR408)的損耗正切值約為0.01,介電常數(shù)在3和4之間;低損耗材料(如Duroid 5870)的損耗正切值約為0.001,介電常數(shù)低于3。介電衰減與損耗正切和介電常數(shù)的平方根成正比,如公式3所示。

表1:介電材料種類。

利用公式1在14GHz頻率和8英寸走線長度條件下進行計算,從結(jié)果可見,高、中和低損耗材料的介電衰減分別為12.35dB、4.91dB和0.47dB。之前已經(jīng)提到,在14GHz頻率、8英寸走線長度條件下,插入損耗低于10dB,應(yīng)選擇較低損耗的材料,以便為其它通道損耗留出裕量。

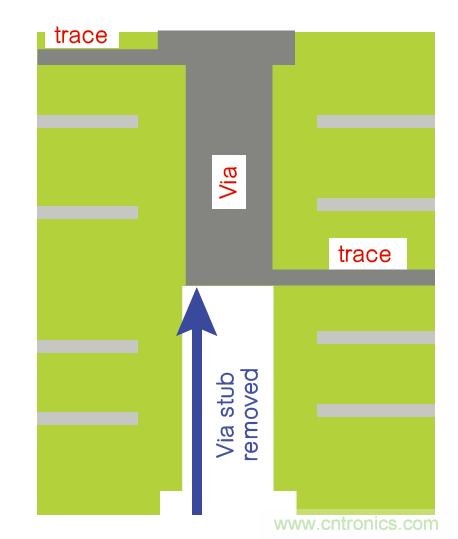

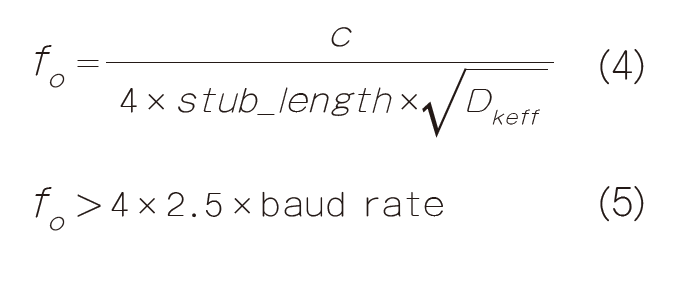

2.最大限度減少過孔殘樁

當使用過孔來連接印刷電路板走線至集成電路時,應(yīng)使用盲孔或反鉆孔(如圖5所示),以最大限度減少殘樁長度,進而提高1/4波諧振頻率,增加物理層鏈路的帶寬。參考公式4,1/4波諧振頻率與殘樁長度成反比。重新排列公式4和5,對于使用低損耗材料的印刷電路板上的50Gbps(即25GBaud/s)PAM-4傳輸, 為2.33,最大殘樁長度可以達到大約16mil。

為2.33,最大殘樁長度可以達到大約16mil。

圖5:盲孔或反鉆孔。

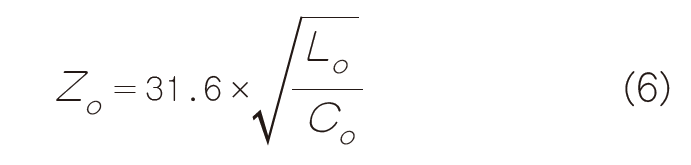

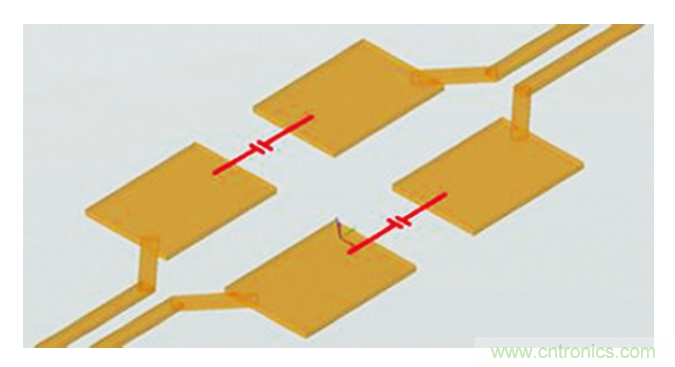

3.最大限度減少交流耦合電容器表面貼裝焊盤造成的阻抗失配

與印刷電路板走線相比,交流耦合電容器表面貼裝焊盤使用的銅片更寬。例如,0402封裝中的電容器貼裝焊盤寬度為20mil,而0603封裝的焊盤寬度為30mil。圖6顯示了與100Ω差分走線(differential trace)串聯(lián)的電容器表面貼裝焊盤的3D模型,從圖中可以看出,沿著這些6mil寬的銅片走線傳播的信號,一旦到達更寬的銅片焊盤(例如0603封裝的30mil寬度),會遇到阻抗不連續(xù)性。根據(jù)公式6和7,銅片的橫截面積越大,電容就越大,導(dǎo)致傳輸線特征阻抗出現(xiàn)電容不連續(xù)性(如下降)。

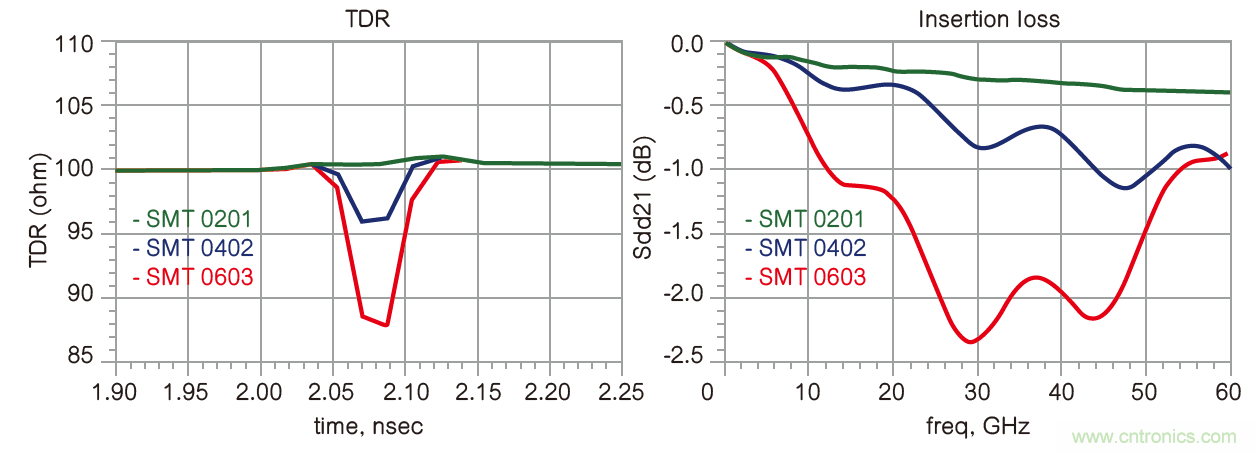

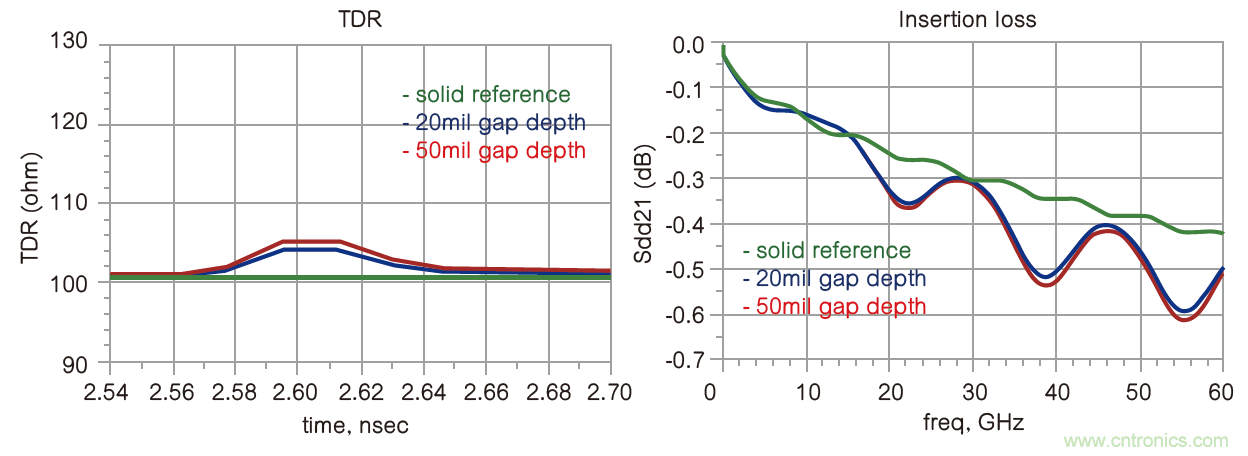

從圖7的時域反射計(TDR)和Sdd21曲線可知,焊盤越寬,阻抗不連續(xù)性就越大,這種不連續(xù)性會產(chǎn)生更嚴重的信號反射,進而引起更大的插入損耗。0603和0402在14GHz時的衰減分別為1.2dB和0.4dB,至少兩倍于0201(即0.2dB)的情況。因此,設(shè)計師應(yīng)該使用封裝更小的電容器,例如0201(即10mil寬焊盤)來最大限度減小不連續(xù)性。

圖6:使用Keysight EMPro建模電容表面貼裝焊盤與差分走線串聯(lián)。

圖7:使用Keysight EMPro仿真不同表面貼裝焊盤寬度的TDR和Sdd21與500mil長的印刷電路板走線串聯(lián)。

4.提供連續(xù)參考面

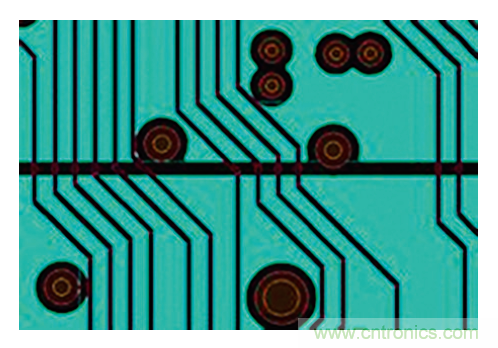

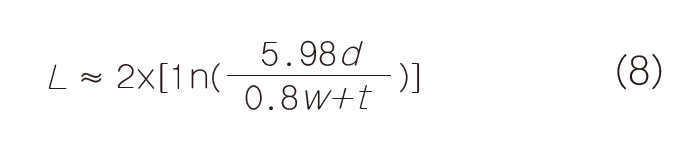

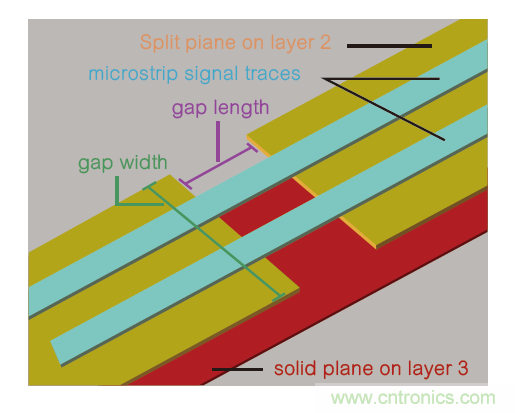

當印刷電路板走線跨越2個分離平面之間的間隙時(圖8粗黑線所示),會遇到電感阻抗不連續(xù)性或瑕疵參考。這一現(xiàn)象可用公式(6)和(8)分別確定。為了研究瑕疵參考的影響,在EMPro中創(chuàng)建并仿真跨越分離平面的傳輸線3D模型,如圖9所示。微帶差分走線跨越了100mil長和250mil寬的間隙。間隙深度為微帶差分走線與第3層固體面的間距??缭介g隙時,走線與參考底面之間的距離會增加(即電流返回路徑變長),導(dǎo)致電感升高,從而引起間隙的走線阻抗增加。圖10中的TDR和Sdd21曲線證實了非固體參考面對信號完整性的負面影響,跨越分離面會產(chǎn)生更大的電感阻抗不連續(xù)性,進而導(dǎo)致更高的插入損耗。因此,確保固體參考面覆蓋整個走線長度路徑十分重要。

圖8:印刷電路板俯視圖:信號跨越分離面。

式中: L = 銅走線的寄生電感(nH); d = 銅走線和參考底面之間的距離(cm); w = 銅走線寬度(cm); t = 銅走線厚度(cm); x = 銅走線長度(cm)。

圖9:Keysight EMPro中差分走線跨越分離面的模型。

圖10:使用Keysight EMPro仿真、帶固體參考面并跨越分離面的500mil長印刷電路板走線的TDR和Sdd21。

5.最大限度減少信號串擾

串擾會引起受擾信號出現(xiàn)噪聲感應(yīng),從而導(dǎo)致接收集成電路的誤碼增加。因此,帶狀線上使用非交叉布線,因為FEXT相比NEXT更低;而在微帶線上使用交叉布線,因為與FEXT相比NEXT更低。除此之外,差分對間間隔應(yīng)至少是走線寬度的三倍。

6.差分對內(nèi)偏移

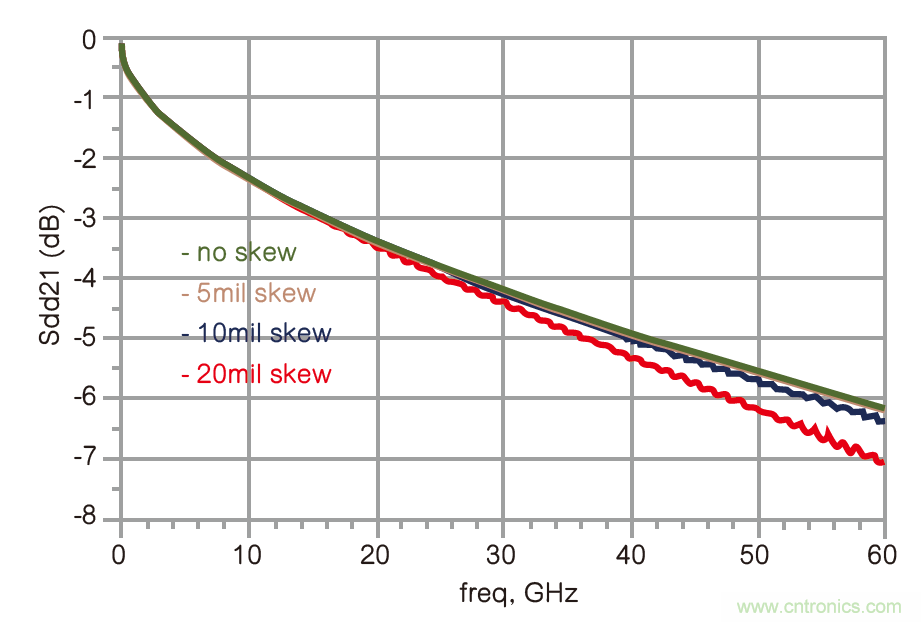

印刷電路板走線中的差分對內(nèi)偏移會帶來更高的插入損耗,從而增加物理層鏈路的誤碼率。由于反相和非反相信號的相位并不是正好相差180度,所以差分模式中的眼高度會變小。圖11中的Sdd21曲線顯示了差分對內(nèi)偏移對信號完整性的影響,偏移越大,插入損耗越高。因此,每個物理層鏈路的差分對內(nèi)偏移都應(yīng)限制在5mil以內(nèi),以減少傳輸損耗??梢允褂蒙咝尾季€技術(shù)來最大限度減少偏移。

圖11:使用Keysight ADS仿真、具有不同差分對內(nèi)偏移的8英寸長印刷電路板走線的Sdd21。

7.光纖編織

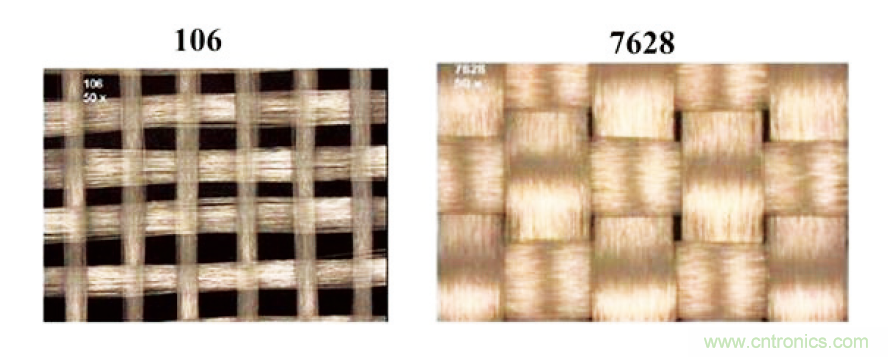

印刷電路板介電基片由編織玻璃纖維與環(huán)氧樹脂結(jié)合組成。圖12是使用顯微鏡看到的、采用纖維編織樣式106和7628制成的印刷電路板基片的俯視圖。淺棕色粗線是玻璃纖維編織部分,黑色的方塊是環(huán)氧樹脂。編號更高的玻璃纖維樣式,如7628,可以實現(xiàn)更密集的玻璃纖維編織。

圖12:印刷電路板的介電基片是利用玻璃纖維樣式106和7628編織的纖維織物。

玻璃纖維與環(huán)氧樹脂的介電屬性截然不同。例如,NE玻璃纖維的介電常數(shù)(Dk)和損耗正切(Df)分別為4.4和0.0006,E玻璃纖維的Dk和Df分別為6.6和0.0012。而環(huán)氧樹脂的Dk為3.2,遠遠低于玻璃纖維的對應(yīng)值。當使用較為稀疏的纖維編織做基片時,印刷電路板走線能夠更頻繁地穿過樹脂和玻璃纖維的不同區(qū)域。結(jié)果就是,信號沿著走線從發(fā)送端傳輸?shù)浇邮斩耍渌俣然騻鞑r延經(jīng)常會發(fā)生變化。它們之間的關(guān)系可以通過公式9來說明。

式中: V = 信號在印刷電路板上的速度(英寸/ns); C = 光速(約12英寸/ns); = 介電常數(shù)。

= 介電常數(shù)。

這種情況為50Gbps信號傳輸帶來了巨大挑戰(zhàn)。例如,在最壞情況下,非反相信號走線可能穿過玻璃纖維但沒有穿過環(huán)氧樹脂,而反相信號的走線可能穿過很多樹脂區(qū)域。結(jié)果,由于反相信號遇到不斷變化的傳播時延,非反相信號與反相信號之間的相位差在接收端一般會遠遠小于180o。上升沿和下降沿之間的大偏移或錯位,導(dǎo)致眼圖寬度和高度減少。而且,接收端會出現(xiàn)高誤碼率。因此,解決辦法就是采用更密集的纖維編織。

布局后的通道仿真

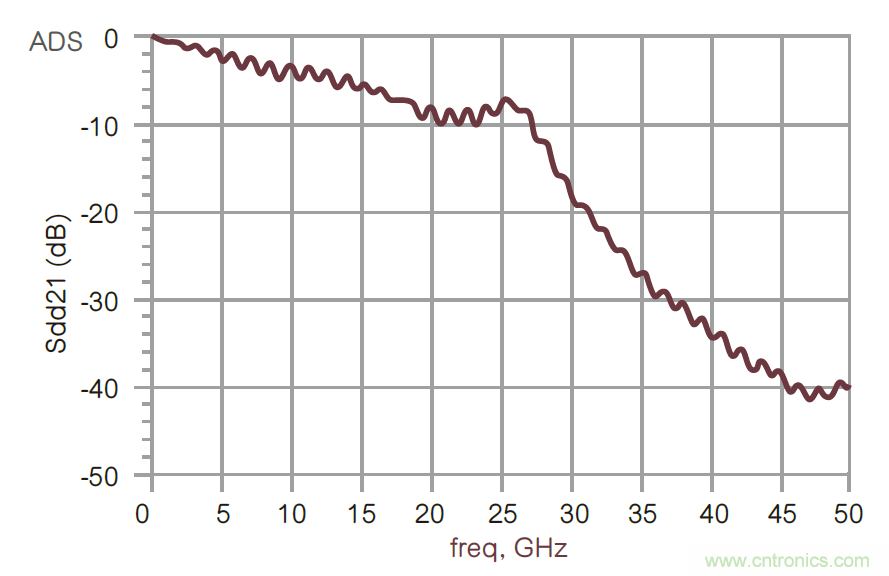

一旦按照上述關(guān)鍵實踐完成了印刷電路板布局設(shè)計,布局文件將導(dǎo)入Keysight EMPro進行3DEM仿真。選擇圖13中突出顯示的8英寸長差分走線進行s參數(shù)抽取,將其導(dǎo)入Keysight ADS進行布局后PAM-4通道仿真。圖14中的插入損耗曲線顯示提取的差分走線符合規(guī)定的閾值,即在14GHz時低于10dB,在28GHz時低于20dB。

圖13:選擇差分走線用于3DEM仿真。

圖14:印刷電路板上所選PAM-4差分走線的插入損耗曲線。

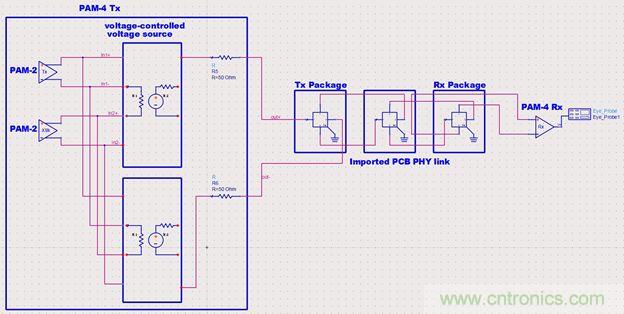

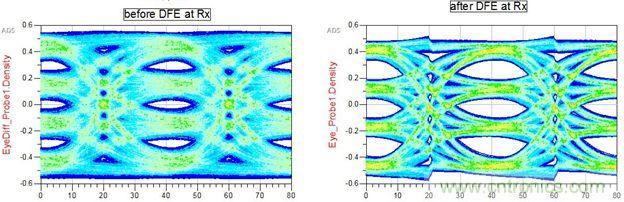

圖15顯示了使用Keysight ADS生成的通道分析拓撲,兩個25GBaud/s的PAM-2信號注入壓控電壓源以生成PAM-4信號。PAM-4波形的傳播路徑為:發(fā)射端封裝、8英寸PCB走線(即圖13中顯示的傳輸線)、接收端封裝,最后是接收端。在發(fā)射端,信號幅度和上升/下降時間分別為1.2Vpp和16ps。PAM-4信號的最小眼寬和眼高分別為1/4單位間隔(即25GBaud/s數(shù)據(jù)速率下為10ps)和50mV。如圖16所示,PAM-4眼圖有4個數(shù)字幅度電平,因此有3個眼圖。在啟用決策反饋均衡(DFE)前,接收端信號的眼高和眼寬分別為60mV和14ps。一旦啟用接收端的6接頭DFE,眼圖幾乎變大一倍(即140mV眼高和23ps眼寬)。結(jié)果符合指南中的技術(shù)指標。均衡方案的選擇和接頭的調(diào)節(jié)很大程度上取決于通道的插入損耗或頻率響應(yīng)。我們進行了多次嘗試來獲得更好的開眼結(jié)果。

圖15:使用Keysight ADS在25GBaud/s下進行布局后PAM-4通道仿真。

圖16:從圖15中的通道仿真結(jié)果得到的接收端眼圖。

結(jié)論

工程師在設(shè)計印刷電路板PAM-4物理層通道時,應(yīng)謹慎借鑒本文討論的所有關(guān)鍵實踐。實施50Gbps PAM-4物理層鏈路時必須嚴格要求,確保在高速收發(fā)器之間實現(xiàn)穩(wěn)定的通信。

作者:Chang Fei Yee,Keysight公司

本文轉(zhuǎn)載自《電子技術(shù)設(shè)計》。

推薦閱讀: