【導(dǎo)讀】電阻值的計(jì)算,我們在高中時(shí)期就會了,那么上拉電阻阻值的計(jì)算是怎么樣的呢?下面由小編為您介紹OC門和OD門上拉電阻阻值的計(jì)算技巧。

首先來看一下什么是OC門和OD門,OC門是集電極開路(Open Collector Gate)集成TTL門電路,即TTL門電路的一種,顧名思義,其集成電路內(nèi)部輸出管的集電極開路。在使用中門電路的輸出端必須經(jīng)上拉電阻接另一電源電壓。通過調(diào)節(jié)數(shù)值或上拉電阻阻值,可以改變輸出端輸出的高電平的數(shù)值或輸出的驅(qū)動電流值。這就是OC門與普通TTL門電路的主要區(qū)別。除此,兩個(gè)以上OC門的輸出端可以并聯(lián),而普通TTL門電路輸出端不能隨便并聯(lián)。OD門是漏極開路(()pen Drain Collector Gate)集成CMOS門電路。它的特性和使用情況與OC完全相同。

在單個(gè)OC(或OD)門的使用中,單個(gè)OC(或OD)門電路的輸出端與外接電源之間需接上拉電阻R,否則輸出端無高、低電平。在輸入信號作用下,當(dāng)門電路內(nèi)部輸出管飽和時(shí),通過電阻R的電流是內(nèi)部管的飽和電流。減去內(nèi)部管的飽和電流在電阻R上的壓降就是輸出端y的低電平輸出電壓值。在信號作用下,當(dāng)內(nèi)部輸出管截止時(shí),通過電阻R的電流是內(nèi)部管的截止電流。減去內(nèi)部管的截止電流在電阻R上的壓降,就是輸出端y的高電平輸出電壓值。如果輸出端外接負(fù)載.電阻上的壓降還要考慮負(fù)載電流,而負(fù)載電流的方向和大小由輸入特性決定。這就是計(jì)算電路中電阻阻值的技巧。

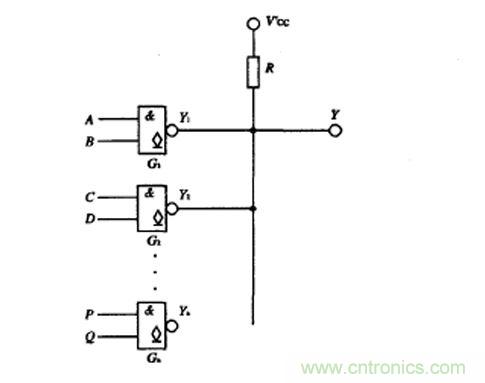

另外,上拉電阻在多個(gè)OC或(或OD)門的使用中,也有一定的計(jì)算機(jī)巧,多個(gè)OC或(或OD)門的輸出端并聯(lián),共用一個(gè)上拉電阻,否則輸出端無高、低電平。這種連接叫“線與”。

Y=Y1·Y2·...·Yn,可見,Y1,Y2,...Yn,中只要有一個(gè)以上為低電平時(shí),y就為低電平;而只有Y1,Y2,?,Yl均為高電時(shí),Y才為高電平。在輸入信號作用下Y為低電平時(shí)。根據(jù)Y1,Y2,?,Yn的輸出情況,所有輸出低電平的集成電路內(nèi)部輸出管的飽和電流決定電阻R上的壓降。Vcc減去內(nèi)部管的總飽和電流在電阻R上的壓降就是輸出端y的低電平輸出電壓值。在輸入信號作用下Y為高電平時(shí),所有集成電路內(nèi)部輸出管的截止電流決定電阻R上的壓降。Vcc減去內(nèi)部管的總截止電流在電阻R上的壓降。就是輸出端Y的高電平輸出電壓值。如果輸出端外接負(fù)載門,電阻上的壓降還要考慮負(fù)載電流,而負(fù)載電流的方向和大小由負(fù)載門的輸入特性決定。這就是下圖中電路中電阻阻值的技巧。