【導(dǎo)讀】高精度應(yīng)用需要精心設(shè)計(jì)的低噪聲模擬前端來(lái)獲得最佳信噪比(SNR)�����,這就要求采用明智的方法來(lái)選擇ADC以全面準(zhǔn)確地捕捉傳感器信號(hào)���。還要選用驅(qū)動(dòng)運(yùn)算放大器和基準(zhǔn)電壓源等支持器件來(lái)優(yōu)化電路性能。

振動(dòng)��、溫度���、壓力和光等現(xiàn)實(shí)世界的信號(hào)需要精 確的信號(hào)調(diào)理和信號(hào)轉(zhuǎn)換�,才能在數(shù)字域中進(jìn) 行進(jìn)一步數(shù)據(jù)處理���。為了克服高精度應(yīng)用的多 種挑戰(zhàn)�����,需要一個(gè)精心設(shè)計(jì)的低噪聲模擬前端來(lái)實(shí)現(xiàn)最佳 信噪比(SNR)�����。但許多系統(tǒng)既負(fù)擔(dān)不起最昂貴的器件�,也 無(wú)法承受低噪聲器件的更高功耗�����。本文解決有關(guān)利用噪聲 優(yōu)化方法來(lái)設(shè)計(jì)完整解決方案的問(wèn)題。本文提出了一種系 統(tǒng)的方法來(lái)設(shè)計(jì)增益模塊和ADC組合�,并給出一個(gè)實(shí)例供 大家參考。以調(diào)理低頻(接近直流)信號(hào)為例���,對(duì)該電路進(jìn) 行噪聲計(jì)算和分析���。

設(shè)計(jì)模擬前端時(shí),請(qǐng)遵循以下七個(gè)步驟:

1. 描述傳感器或增益模塊前端的電氣輸出��。

2. 計(jì)算ADC的需求�����。

3. 為信號(hào)轉(zhuǎn)換找到最佳ADC + 基準(zhǔn)電壓���。

4. 為運(yùn)算放大器找到最大增益并定義搜索條件��。

5. 找到最佳放大器并設(shè)計(jì)增益模塊�����。

6. 根據(jù)設(shè)計(jì)目標(biāo)檢查解決方案總噪聲����。

7. 運(yùn)行仿真并驗(yàn)證。

第1步:描述傳感器或增益模塊前端的電氣輸出

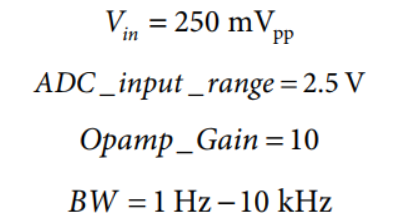

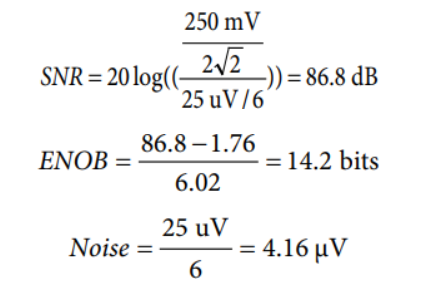

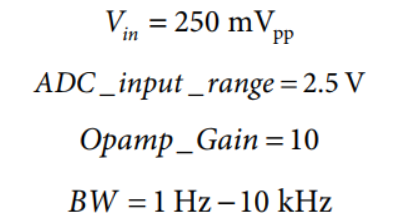

信號(hào)可能直接來(lái)源于傳感器�����,也可能在到達(dá)增益模塊之前 經(jīng)過(guò)EMI和RFI濾波器����。為了設(shè)計(jì)增益模塊�����,必須知道信號(hào) 的交流和直流特性以及可用的電源�。知道了信號(hào)的特性和 噪聲電平后,我們就能知道選擇ADC時(shí)需要何種輸入電 壓范圍和噪聲電平���。假設(shè)有一個(gè)傳感器��,以250 mV p-p (88.2 mV rms)和25 V p-p噪聲的滿量程幅度輸出一個(gè)10 kHz 信號(hào)�����。進(jìn)一步假設(shè)系統(tǒng)中有一個(gè)可用的5 V電源�����。有了這些 信息�����,我們應(yīng)該能計(jì)算出第2步中的ADC輸入端的信噪 比���。為簡(jiǎn)化數(shù)據(jù)處理和避免混淆�,假設(shè)我們將該解決方案 設(shè)計(jì)為在室溫下工作����。

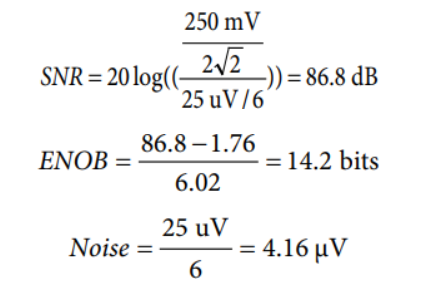

第2步:計(jì)算ADC的需求

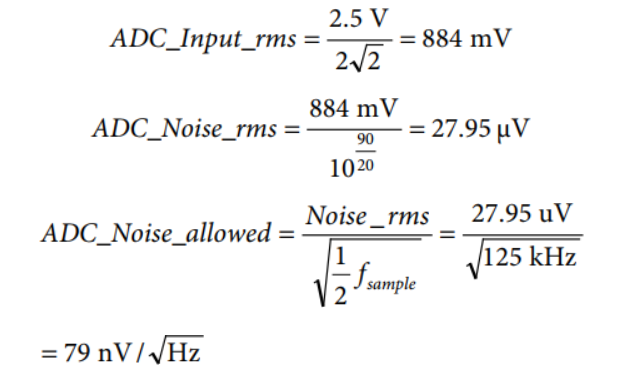

我們需要何種ADC、采樣速率如何����、多少位、噪聲指標(biāo)如 何����?若從第一步知道了輸入信號(hào)幅度以及噪聲信息,我們 就能計(jì)算出增益模塊輸入端的信噪比(SNR)���。我們需要選 擇一個(gè)有較高信噪比的ADC����。在選擇ADC時(shí),知道SNR將 有助于我們計(jì)算有效位數(shù)(ENOB)�。此關(guān)系表達(dá)式如下。好 的ADC數(shù)據(jù)手冊(cè)總會(huì)標(biāo)出SNR和ENOB���。此例中所需要的 86.8 dB SNR和14.2位ENOB決定了我們應(yīng)選擇一個(gè)16位的模 數(shù)轉(zhuǎn)換器。此外���,奈奎斯特準(zhǔn)則要求采樣率(fs)應(yīng)至少兩 倍于最大輸入頻率(n)�,因此一個(gè)20 kSPS ADC應(yīng)該就已 足夠��。

下一步我們需要設(shè)計(jì)總體解決方案����,使得噪聲密度不超過(guò) 416 nV/√Hz。這就把信號(hào)調(diào)理電路的噪聲確定為輸入噪聲 的1/10��。

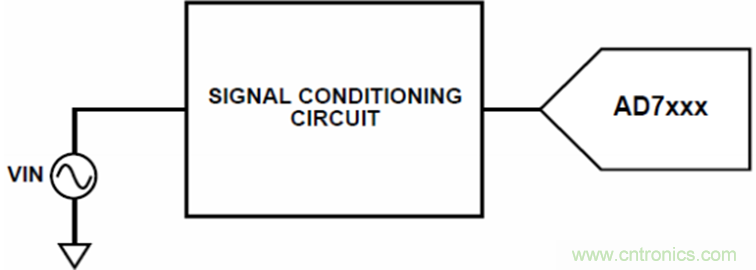

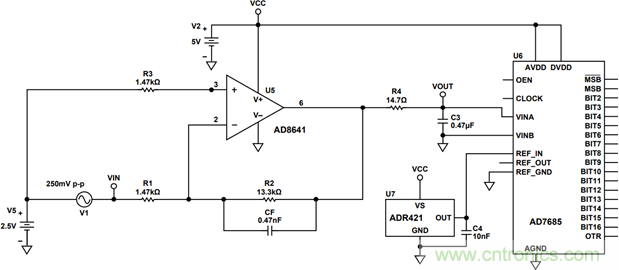

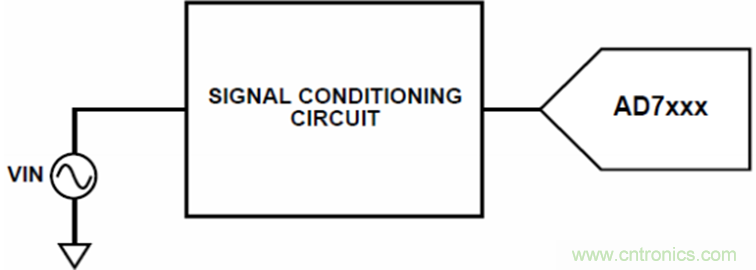

圖1. 典型信號(hào)調(diào)理鏈

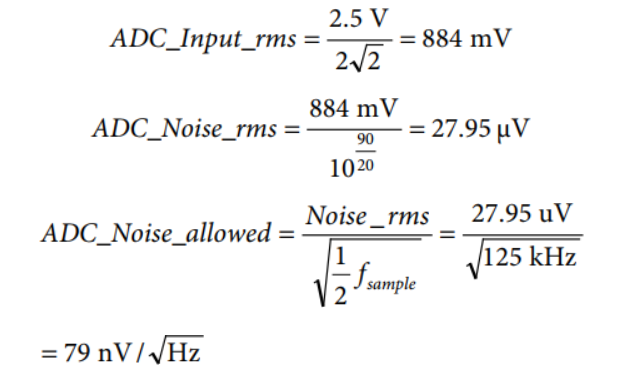

第3步:為信號(hào)轉(zhuǎn)換找到最佳ADC + 基準(zhǔn)電壓

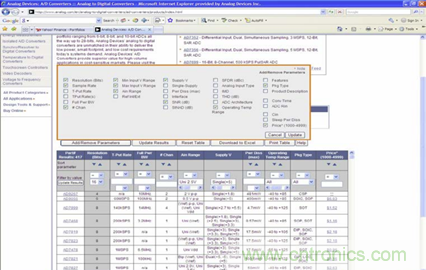

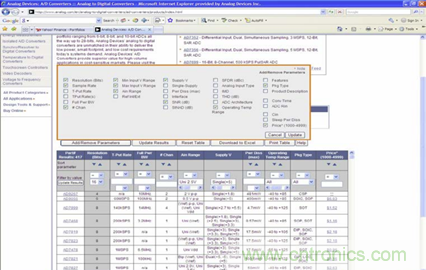

有了一系列的搜索條件���,我們就有許多種方法找到合適的 ADC�����。要找到一個(gè)16位ADC�����,最簡(jiǎn)單的方法之一就是使用 廠商網(wǎng)站上的搜索工具��。輸入分辨率與采樣速率�����,就可找 到許多推薦的ADC��。

許多16位的ADC滿足14.5位ENOB需求�。如果您想得到更 佳的噪聲性能,可使用過(guò)采樣迫使ENOB達(dá)到16位(由4n過(guò) 采樣得到n位增強(qiáng))���。通過(guò)過(guò)采樣��,您可以使用較低分辨率 的ADC:256過(guò)采樣的12位ADC(44過(guò)采樣)可得到16位噪聲 性能�����。在我們的例子中���,這意味著5.126 MHz采樣率的12位ADC(20 kSPS × 256)��,或是42過(guò)采樣的14位ADC�;若1.28 MSPS 則更佳�����。然而這些選擇的成本卻和AD7685(16位����、250 kSPS ADC)相當(dāng) 。

從列表中我們選擇了AD7685(16位 PulSAR® ADC ADC)�。該轉(zhuǎn)換 器具有90 dB SNR和250 kSPS采樣率�����,符合我們的需要����。此 ADC推薦搭配使用ADR421/ADR431精密XFET®基準(zhǔn)電 壓源。2.5 V的輸入范圍超過(guò)了我們需要的250 mV p-p輸入 特性

圖2. 典型的ADC選型表

AD7685基準(zhǔn)輸入具有動(dòng)態(tài)輸入阻抗�,因此需進(jìn)行去耦以使 寄生電感最小(方法是在引腳附近放置一個(gè)陶瓷去耦電容, 并用較寬的低阻抗走線進(jìn)行連接)����。一個(gè)22 F陶瓷芯片電 容可提供最佳性能����。

第4步:為運(yùn)算放大器找到最大增益并定義搜索條件

有了ADC的輸入電壓范圍將有助于我們?cè)O(shè)計(jì)增益模塊�。為 了最大化動(dòng)態(tài)范圍,我們需要在給定的輸入信號(hào)和ADC輸 入范圍內(nèi)選取盡可能高的增益����。這意味著我們可以將該例 子中的增益模塊設(shè)計(jì)成具有10倍的增益。

雖然AD7685很容易驅(qū)動(dòng)����,但驅(qū)動(dòng)放大器需要滿足某些要 求。例如�,為保持AD7685的SNR和轉(zhuǎn)換噪聲性能,驅(qū)動(dòng)放 大器產(chǎn)生的噪聲必須盡可能低�����,但要注意增益模塊可同時(shí) 放大信號(hào)和噪聲����。若要使得噪聲在增益模塊前后都保持不 變,我們需要選擇具有更低噪聲值的放大器和相關(guān)元件���。 此外�����,驅(qū)動(dòng)器的THD性能應(yīng)與AD7685相當(dāng)�����,并且必須使 ADC電容陣列以16位水平(0.0015%)建立滿量程階躍��。來(lái)自 放大器的噪聲可使用外部濾波器進(jìn)一步過(guò)濾����。

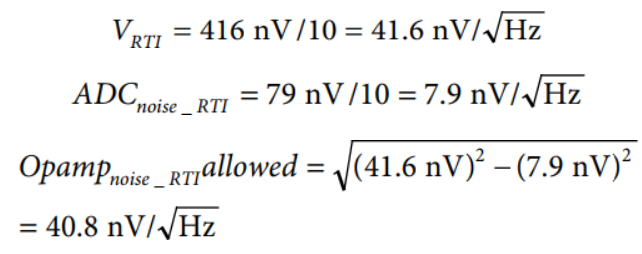

運(yùn)算放大器的輸入端允許多大的噪聲?牢記我們?cè)O(shè)計(jì)的總 體解決方案的噪聲密度不超過(guò)416 nV/rt-Hz��。我們?cè)O(shè)計(jì)的 增益模塊應(yīng)具有更低的本底噪聲��,系數(shù)為10��,因?yàn)槲覀兊?增益為10��。這將確保來(lái)自放大器的噪聲遠(yuǎn)低于傳感器的本 底噪聲�����。計(jì)算噪聲裕量時(shí)�,我們可假設(shè)運(yùn)算放大器輸入端 的噪聲大致等于運(yùn)算放大器的總噪聲加上ADC的噪聲。

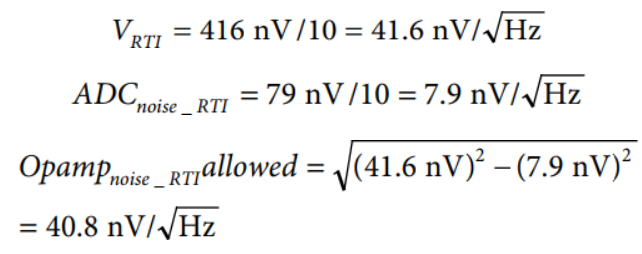

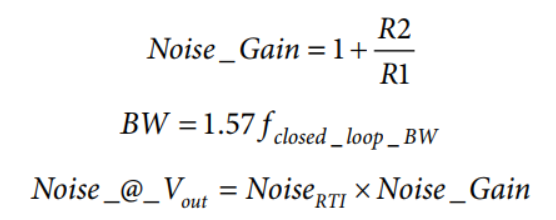

第5步:找到最佳放大器并設(shè)計(jì)增益模塊

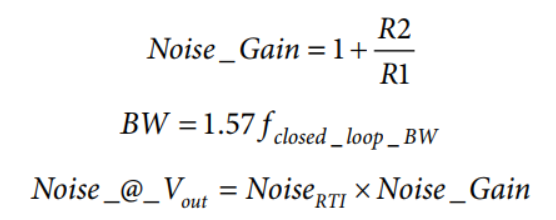

知道了輸入信號(hào)帶寬后�����,運(yùn)算放大器選型的第一步是選擇 一個(gè)具有合理的增益帶寬積(GBWP)的運(yùn)算放大器�,并且 該放大器可以最小的直流和交流誤差處理該信號(hào)。為得到 最佳的增益帶寬積�����,需要知道信號(hào)帶寬���、噪聲增益以及增 益誤差���。下面給出這些術(shù)語(yǔ)的定義。一般而言����,若想保持 增益誤差小于0.1%,推薦選用增益帶寬比輸入信號(hào)帶寬大 100倍的放大器���。另外���,我們需要一個(gè)可快速建立且驅(qū)動(dòng) 能力良好的放大器����。注意�����,我們的噪聲預(yù)算要求運(yùn)算放大器輸入端的總噪聲低于40.8 nV/√Hz��,而ADC規(guī)定的指標(biāo)為7.9 nV/√Hz�。總結(jié)運(yùn)算放大器的查找條件如下:UGBW > 1 MHz���、5 V單電源�����、良好的電壓噪聲�、電流噪聲����、THD特 性��、低直流誤差(不降低ADC性能)。

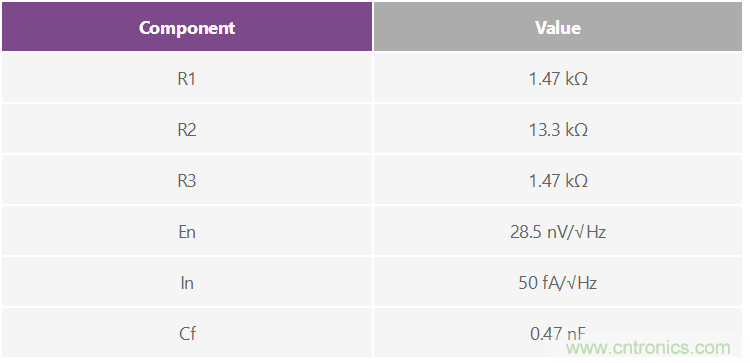

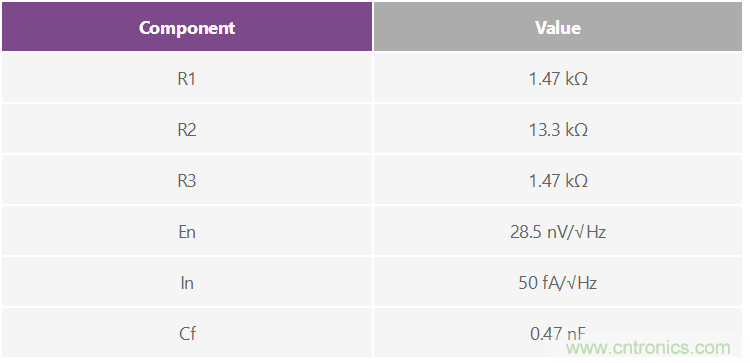

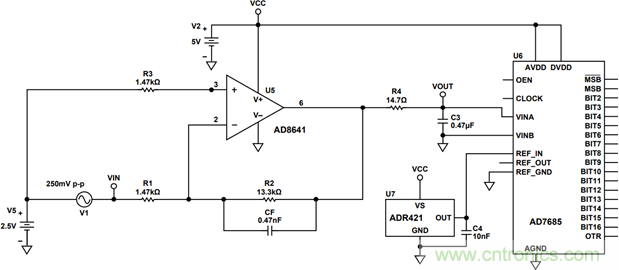

搜索ADC時(shí)采用相似的查找方法�����, 本例我們選擇AD8641�����。AD8641為低功耗����、精密JFET輸入放大器,具有 極低的輸入偏置電流和軌到軌輸出特性�����,可在5 V至26 V電 源下工作�����。相關(guān)數(shù)據(jù)在下表中列出��。我們可采用表中的元 件值對(duì)運(yùn)算放大器進(jìn)行同相配置�����。

表1. 圖3 所示完整解決方案 的元件值

圖3. 完整的解決方案

所有有源和無(wú)源元件都各自產(chǎn)生噪聲,因此選擇不降低性 能的元件尤其重要�。例如,購(gòu)買一個(gè)低噪聲運(yùn)算放大器并 在其周圍放置大電阻就是一種浪費(fèi)���。牢記一個(gè)1 kΩ的電阻 器可產(chǎn)生4 nV的噪聲���。

如前所述,可考慮在ADC和該增益模塊之間使用一個(gè)RC 濾波器�����,這樣應(yīng)該有助于縮小帶寬并優(yōu)化SNR�。

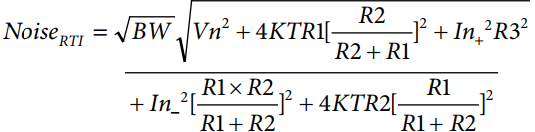

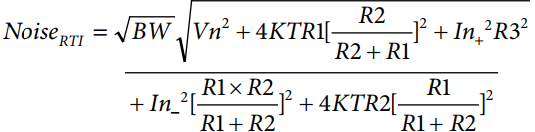

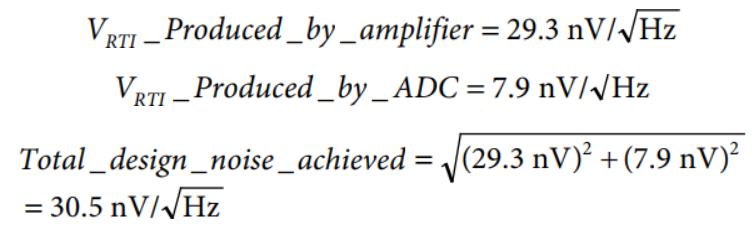

第6步:根據(jù)設(shè)計(jì)目標(biāo)檢查解決方案總噪聲

充分了解所設(shè)計(jì)電路中的各種誤差源是極其重要的。為了 獲得最佳SNR��,我們需要寫出前述方案的總噪聲方程���。方 程如下式所示�����。

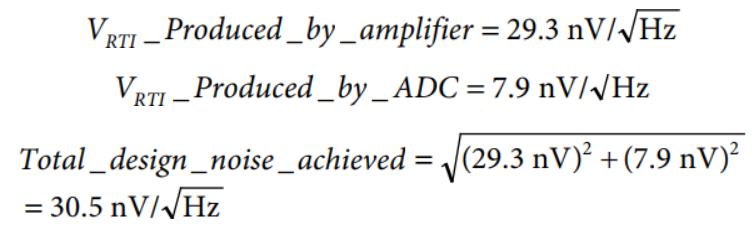

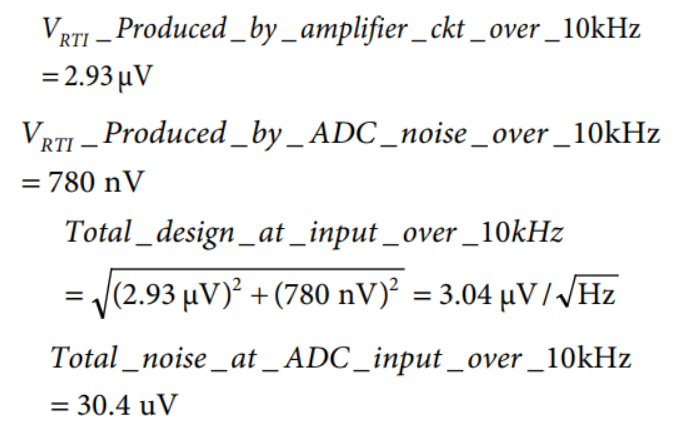

我們可算出運(yùn)算放大器輸入端的總噪聲���,并確保其低于41.6 nV/√Hz,一如我們所預(yù)期的那樣����。

為了在整個(gè)帶寬上對(duì)總噪聲進(jìn)行積分,我們可看到在濾波 器帶寬上的ADC輸入端的總噪聲是3.05 μV����,低于設(shè)計(jì)所需 的4.16 μV。由于AD8641的轉(zhuǎn)折頻率低于100 Hz��,故此例中 的低頻噪聲(1/f)可忽略不計(jì)���。

保持良好的信噪比需要關(guān)注信號(hào)路徑中每一處細(xì)節(jié)的噪 聲�,并有良好的PCB布局�����。避免在任何ADC下方布設(shè)數(shù)字 線路���,否則會(huì)將噪聲耦合至芯片管芯�,除非在ADC下方鋪 一個(gè)接地層用作屏蔽�����。諸如CNV或時(shí)鐘之類的快速開關(guān)信 號(hào)不應(yīng)靠近模擬信號(hào)路徑。應(yīng)避免數(shù)字信號(hào)與模擬信號(hào) 交疊����。

第7步:運(yùn)行仿真并驗(yàn)證

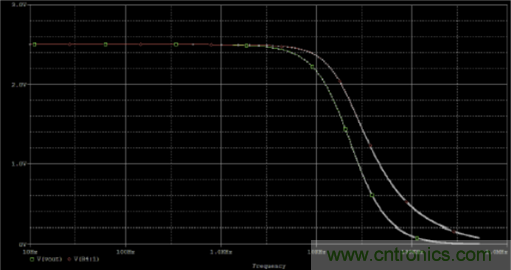

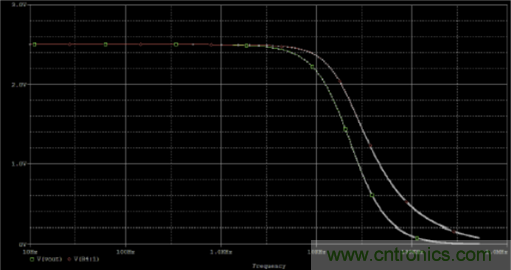

剛開始驗(yàn)證電路設(shè)計(jì)時(shí),使用PSpice宏模型(可從ADI網(wǎng)站 下載)比較合適�。快速仿真顯示出我們?yōu)榻鉀Q方案所設(shè)計(jì)的 信號(hào)帶寬���。圖4顯示了位于AD7685輸入端可選RC濾波器之 前和之后的響應(yīng)��。

圖4. 圖3所示電路的帶寬仿真

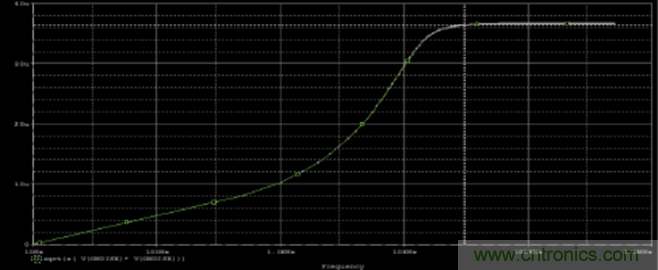

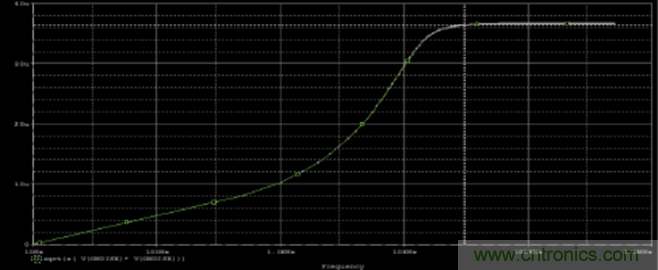

如圖5所示�����,10 kHz帶寬上的總輸出噪聲接近31 μV rms���, 略低于41 μV rms的設(shè)計(jì)目標(biāo)。在量產(chǎn)之前需要制作原型并 驗(yàn)證整套解決方案�。

圖5. 圖3電路的噪聲響應(yīng)仿真

總結(jié)

如今許多設(shè)計(jì)要求低功耗、低成本�,而許多系統(tǒng)既負(fù)擔(dān)不 起最昂貴的器件,也無(wú)法承受低噪聲器件的更高功耗��。為 了從信號(hào)調(diào)理電路得到最低的本底噪聲和最佳性能,設(shè)計(jì) 者必須了解元件級(jí)別的噪聲源�����。保持良好的信噪比需要關(guān) 注信號(hào)路徑每一處細(xì)節(jié)的噪聲�����。通過(guò)遵循以上步驟�����,便 可成功調(diào)理小型模擬信號(hào)�����,并使用超高分辨率ADC將其 轉(zhuǎn)換����。

參考電路

1. 應(yīng)用筆記AN-202��,IC放大器用戶指南:去耦�、接地及 其他一些要點(diǎn)。ADI公司��。

2. 應(yīng)用筆記AN-347, 如何排除干擾型噪聲——方法及原 理:一種理性方法�����。ADI公司�����。

3. Barrow, J和A. Paul Brokaw���。1989.“低頻和高頻電路接 地”��,Analog Dialogue�。 (23-3) ADI公司���。

4.研討會(huì):傳感器信號(hào)調(diào)理電路中的噪聲優(yōu)化(第一部分)��。

5. 研討會(huì):傳感器信號(hào)調(diào)理電路中的噪聲優(yōu)化(第二部分)���。

推薦閱讀: