【導(dǎo)讀】目前,大部分傳導(dǎo) EMI 問題都是由共模噪聲引起的。而且,大部分共模噪聲問題都是由電源中的寄生電容導(dǎo)致的。以下將著重討論當(dāng)寄生電容直接耦合到電源輸入電線時(shí)會(huì)發(fā)生的情況。

1. 只需幾 fF 的雜散電容就會(huì)導(dǎo)致 EMI 掃描失敗。從本質(zhì)上講,開關(guān)電源具有提供高 dV/dt 的節(jié)點(diǎn)。寄生電容與高 dV/dt 的混合會(huì)產(chǎn)生 EMI 問題。在寄生電容的另一端連接至電源輸入端時(shí),會(huì)有少量電流直接泵送至電源線。

2. 查看電源中的寄生電容。我們都記得物理課上講過,兩個(gè)導(dǎo)體之間的電容與導(dǎo)體表面積成正比,與二者之間的距離成反比。查看電路中的每個(gè)節(jié)點(diǎn),并特別注意具有高 dV/dt 的節(jié)點(diǎn)。想想電路布局中該節(jié)點(diǎn)的表面積是多少,節(jié)點(diǎn)距離電路板輸入線路有多遠(yuǎn)。開關(guān) MOSFET 的漏極和緩沖電路是常見的罪魁禍?zhǔn)住?/div>

3. 減小表面面積有技巧。試著盡量使用表面貼裝封裝。采用直立式 TO-220 封裝的 FET 具有極大的漏極選項(xiàng)卡 (drain tab) 表面面積,可惜的是它通常碰巧是具有最高 dV/dt 的節(jié)點(diǎn)。嘗試使用表面貼裝 DPAK 或 D2PAK FET 取代。在 DPAK 選項(xiàng)卡下面的低層 PCB 上安放一個(gè)初級(jí)接地面板,就可良好遮蔽 FET 的底部,從而可顯著減少寄生電容。

有時(shí)候表面面積需要用于散熱。如果您必須使用帶散熱片的 TO-220 類 FET,嘗試將散熱片連接至初級(jí)接地(而不是大地接地)。這樣不僅有助于遮蔽 FET,而且還有助于減少雜散電容。

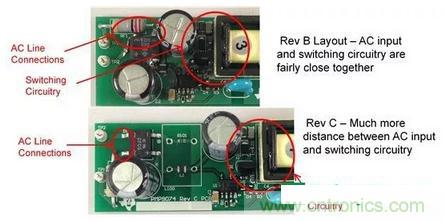

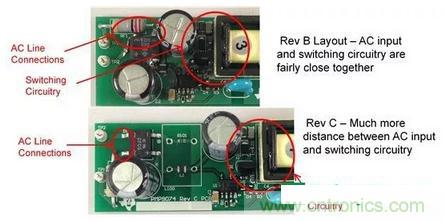

4. 讓開關(guān)節(jié)點(diǎn)與輸入連接之間拉開距離。見圖 1 中的設(shè)計(jì)實(shí)例,其中我忽視了這個(gè)簡(jiǎn)單原則。

圖1:讓輸入布線與具有高 dV/dt 的節(jié)點(diǎn)靠得太近會(huì)增加傳導(dǎo) EMI。

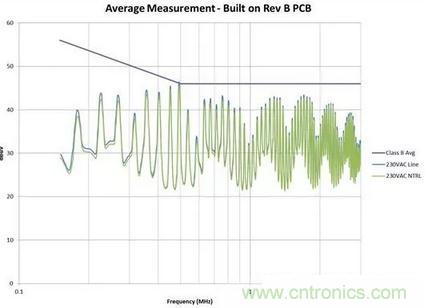

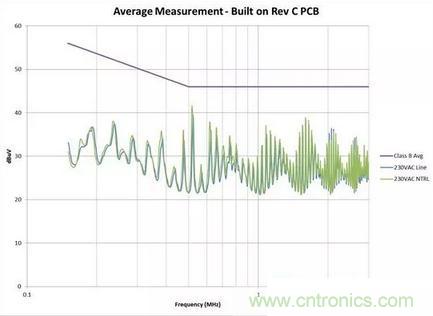

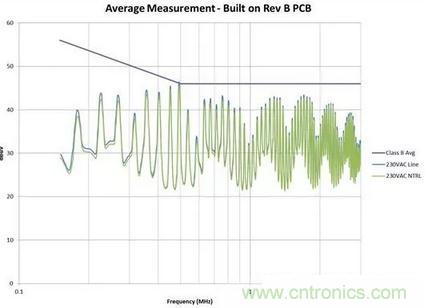

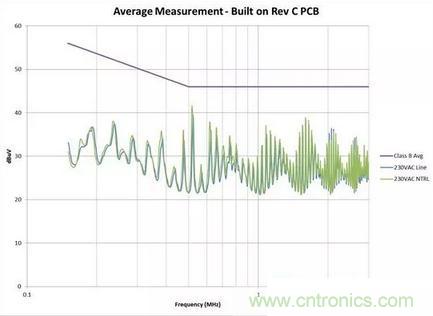

我通過簡(jiǎn)單調(diào)整電路板(無電路變化),將噪聲降低了大約 6dB。見圖 2 和圖 3 的測(cè)量結(jié)果。在有些情況下,接近高 dV/dt 進(jìn)行輸入線路布線甚至還可擊壞共模線圈 (CMC)。

圖2:從電路板布局進(jìn)行 EMI 掃描,其中 AC 輸入與開關(guān)電路距離較近

圖3:從電路板布局進(jìn)行 EMI 掃描,其中 AC 輸入與開關(guān)電路之間距離較大

您是否有過在顯著加強(qiáng)輸入濾波器后 EMI 改善效果很小甚至沒有改善的這種遭遇?這很有可能是因?yàn)橛幸恍﹣碜阅硞€(gè)高 dV/dt 節(jié)點(diǎn)的雜散電容直接耦合到輸入線路,有效繞過了您的 CMC。為了檢測(cè)這種情況,可臨時(shí)短路 PCB 上 CMC 的繞組,并將一個(gè)二級(jí) CMC 與電路板的輸入電線串聯(lián)。如果有明顯改善,您需要重新布局電路板,并格外注意輸入連接的布局與布線。