【導讀】MOSFET作為主要的開關功率器件之一,被大量應用于模塊電源。本文主要闡述了MOSFET在模塊電源中的應用,分析了MOSFET損耗特點,提出了優(yōu)化方法;并且闡述了優(yōu)化方法與EMI之間的關系。

一、引言

MOSFET作為主要的開關功率器件之一,被大量應用于模塊電源。了解MOSFET的損耗組成并對其分析,有利于優(yōu)化MOSFET損耗,提高模塊電源的功率;但是一味的減少MOSFET的損耗及其他方面的損耗,反而會引起更嚴重的EMI問題,導致整個系統(tǒng)不能穩(wěn)定工作。所以需要在減少MOSFET的損耗的同時需要兼顧模塊電源的EMI性能。

二、開關管MOSFET的功耗分析

MOSFET的損耗主要有以下部分組成:1.通態(tài)損耗;2.導通損耗;3.關斷損耗;4.驅動損耗;5.吸收損耗;隨著模塊電源的體積減小,需要將開關頻率進一步提高,進而導致開通損耗和關斷損耗的增加,例如300kHz的驅動頻率下,開通損耗和關斷損耗的比例已經是總損耗主要部分了。

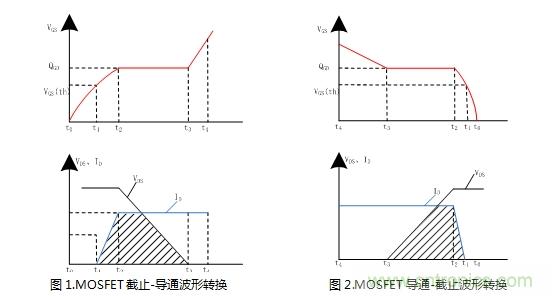

MOSFET導通與關斷過程中都會產生損耗,在這兩個轉換過程中,漏極電壓與漏極電流、柵源電壓與電荷之間的關系如圖1和圖2所示,現(xiàn)以導通轉換過程為例進行分析:

t0-t1區(qū)間:柵極電壓從0上升到門限電壓Uth,開關管為導通,無漏極電流通過這一區(qū)間不產生損耗;

t1-t2區(qū)間:柵極電壓達到Vth,漏極電流ID開始增加,到t2時刻達到最大值,但是漏源電壓保持截止時高電平不變,從圖1可以看出,此部分有VDS與ID有重疊,MOSFET功耗增大;

t2-t3區(qū)間:從t2時刻開始,漏源電壓VDS開始下降,引起密勒電容效應,使得柵極電壓不能上升而出現(xiàn)平臺,t2-t3時刻電荷量等于Qgd,t3時刻開始漏極電壓下降到最小值;此部分有VDS與ID有重疊,MOSFET功耗增大;

t3-t4區(qū)間:柵極電壓從平臺上升至最后的驅動電壓(模塊電源一般設定為12V),上升的柵壓使導通電阻進一步減少,MOSFET進入完全導通狀態(tài);此時損耗轉化為導通損耗。

關斷過程與導通過程相似,只不過是波形相反而已;關于MOSFET的導通損耗與關斷損耗的分析過程,有很多文獻可以參考,這里直接引用《張興柱之MOSFET分析》的總結公式如下:

三、MOSFET的損耗優(yōu)化方法及其利弊關系

3-1. 通過降低模塊電源的驅動頻率減少MOSFET的損耗[稍微提一下EMI問題及其解決方案]

從MOSFET的損耗分析可以看出,開關電源的驅動頻率越高,導通損耗、關斷損耗和驅動損耗會相應增大,但是高頻化可以使得模塊電源的變壓器磁芯更小,模塊的體積變得更小,所以可以通過開關頻率去優(yōu)化開通損耗、關斷損耗和驅動損耗,但是高頻化卻會引起嚴重的EMI問題。金升陽DC/DC R3產品,采用跳頻控制方法,在輕負載情況下,通過降低模塊電源的開關頻率來降低驅動損耗,從而進一步提高輕負載條件下的效率,使得系統(tǒng)在待機工作下,更節(jié)能,進一步提高蓄電池供電系統(tǒng)的工作時間,并且還能夠降低EMI的輻射問題;

3-2.通過降低、來減少MOSFET的損耗

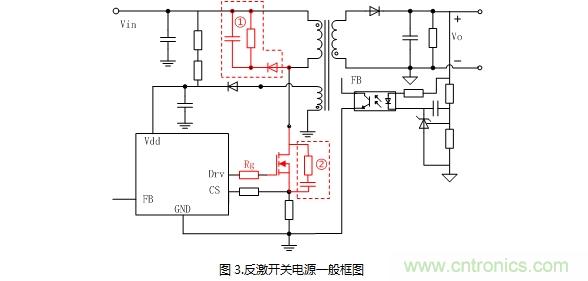

典型的小功率模塊電源(小于50W)大多采用的電路拓撲結構為反激形式,典型的控制電路如圖3所示;從MOSFET的損耗分析還可以知道:與開通損耗成正比、與關斷損耗成正比;所以可以通過減少 、來減少MOSFET的損耗,通常情況下,可以減小MOSFET的驅動電阻Rg來減少、時間,但是此優(yōu)化方法卻帶來嚴重的EMI問題;以金升陽URB2405YMD-6WR3產品為例來說明此項問題:

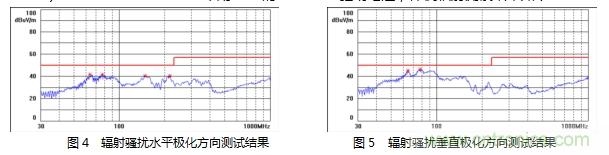

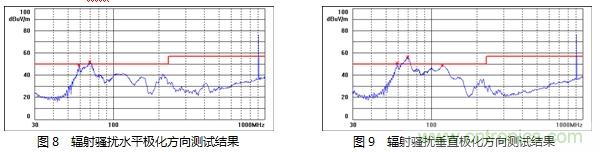

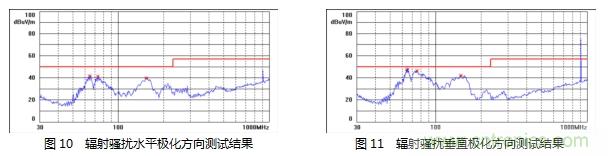

1)URB2405YMD-6WR3采用10Ω的MOSFET驅動電阻,裸機輻射測試結果如下:

2)URB2405YMD-6WR3采用0Ω的驅動電阻,裸機輻射測試結果如下:

從兩種不同的驅動電阻測試結果來看,雖然都能夠通過EN55022的輻射騷擾度的CLASS A等級,但是采用0歐姆的驅動電阻,在水平極化方向測試結果的余量是不足3dB的,該方案設計不能被通過。

3-3.通過降低吸收電路損耗來減少損耗

在模塊電源的設計過程中,變壓器的漏感總是存在的,采用反激拓撲式結構,往往在MOSFET截止過程中,MOSFET的漏極往往存在著很大的電壓尖峰,一般情況下,MOSFET的電壓設計余量是足夠承受的,為了提高整體的電源效率,一些電源廠家是沒有增加吸收電路(吸收電路如圖3標注①RCD吸收電路和②RC吸收電路)來吸收尖峰電壓的。但是,不注意這些吸收電路的設計往往也是導致EMI設計不合格的主要原因。以金升陽URF2405P-6WR3的吸收電路(采用如圖3中的②RC吸收電路)為例:

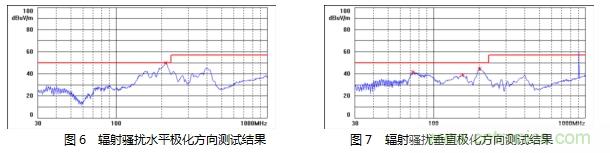

1)驅動電阻Rg為27Ω,無RC吸收電路,輻射騷擾度測試結果如下:

2)驅動電阻為27Ω;吸收電路為電阻R和C 5.1Ω 470pF,輻射騷擾度測試結果如下:

從兩種不同的吸收電路方案測試結果來看,不采用吸收電路的方案,是不能通過EN55022輻射騷擾度的CLASS A等級,而采用吸收電路,則可以解決輻射騷擾度實驗不通過的問題,通過不同的RC組合方式可進一步降低輻射騷擾。

四、總結

MOSFET的功耗優(yōu)化工作實際上是一個系統(tǒng)工程,部分優(yōu)化方案甚至會影響EMI的特性變化。上述案例中,金升陽R3系列產品將節(jié)能環(huán)保的理念深入到電源的開發(fā)過程中,很好地平衡了電源整體效率與EMI特性,從而進一步優(yōu)化了電源參數。將電源參數進一步優(yōu)化,更能兼容客戶系統(tǒng),并發(fā)揮真正的電子系統(tǒng)“心臟”作用,源源不斷的輸送能量。

【推薦閱讀】