【導讀】目前提高效率已成為關鍵目標,為了獲得更好的EMI而采用慢開關器件的權衡并不值得。而鑒于與傳統(tǒng)平面MOSFET技術相比,超級結MOSFET可顯著降低導通電阻和寄生電容。 可很大程度的提高效率,但是弊端就是會形成高頻噪聲和輻射EMI。那怎么辦呢?本文教大家一個方法:調(diào)整調(diào)整PCB布局來降低輻射EMI,噪聲。那么如何調(diào)整PCB布局呢?請看下文。

基于最近的趨勢,提高效率成為關鍵目標,為了獲得更好的EMI而采用慢開關器件的權衡并不值得。超級結可在平面MOSFET難以勝任的應用中提高效率。與傳統(tǒng)平面MOSFET技術相比,超級結MOSFET可顯著降低導通電阻和寄生電容。 導通電阻的顯著降低和寄生電容的降低雖然有助于提高效率,但也產(chǎn)生電壓(dv/dt)和電流(di/dt)的快速開關轉(zhuǎn)換,形成高頻噪聲和輻射EMI。

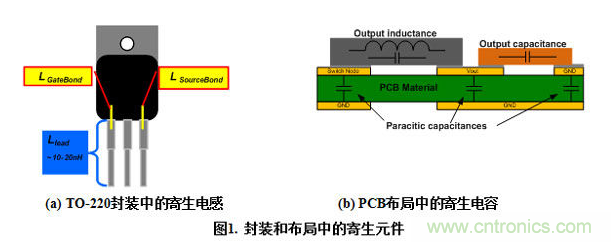

為驅(qū)動快速開關超級結MOSFET,必須了解封裝和PCB布局寄生效應對開關性能的影響,以及為使用超級結所做的PCB布局調(diào)整。主要使用擊穿電壓為500-600V的超級結MOSFET。在這些電壓額定值中,工業(yè)標準TO-220、TO-247、TO-3P和TO-263是應用最廣泛的封裝。封裝對性能的影響有限,這是因為內(nèi)部柵極和源極綁定線長度是固定的。只有引腳的長度可以改變,以減少封裝的源極電感。如圖1(a)所示,10 nH的典型引線電感看起來不大,但這些MOSFET的di/dt可輕松達到500 A/μs! 假定di/dt為500A/μs,10nH引線電感上的電壓為VIND = 5 V;而10nH引線電感的關斷di/dt為1,000 A / μs,可產(chǎn)生VIND = 10 V的電壓。大多數(shù)應用和設計都未考慮到此附加電感也會產(chǎn)生電壓,但這一點不可忽視。以上簡單計算顯示,封裝的總源極電感,即綁定線和引腳電感必須降低至可接受的數(shù)值。噪聲的另一個來源是布局寄生效應。有兩種可見的布局寄生效應: 寄生電感和寄生電容。1 cm走線的電感為6-10 nH,通過在PCB頂部添加一層并在PCB底部添加GND層,可降低此電感值。另一類型是寄生電容。圖1(b)顯示了布局中容性寄生效應的原理。寄生電容由兩條相近走線之間或走線與另外一側的地平面之間引起。另一種電容為器件和地平面間的電容。PCB 板兩面上的兩個并行走線能夠增加電容,同時還能減少回路電感,從而減少電磁噪聲輻射。下次設計需要超級結MOSFET時,請考慮這些布局提示。

相關閱讀: