【導讀】不久前,Dialog半導體公司與格芯(GLOBALFOUNDRIES)簽訂了協(xié)議,向其授權導電橋式隨機存取存儲器(Conductive Bridging RAM;CBRAM)技術。CBRAM屬于通用的存儲器技術,應用范圍非常廣,從可穿戴設備到智能手機等。其性能優(yōu)勢主要體現在低功耗。

CBRAM技術由Dialog于2020年收購的Adesto Technologies首創(chuàng)并獲得專利。有了這項專利許可,格芯將在其22FDX平臺上提供這種配置,并在未來幾年將其擴展到其他平臺。

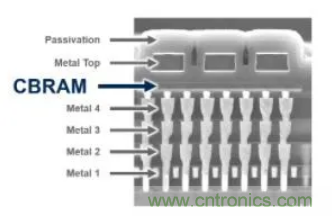

存儲器行業(yè)正在經歷工業(yè)和技術層面的深刻發(fā)展。新的技術知識催生了NVM(非易失性存儲器)元件在電阻上做了改變,并擴展了功能,以適用于光學和電氣設備。CBRAM存儲器是通過采用專利金屬化技術,在標準CMOS互連金屬層之間采用電介質疊層而創(chuàng)建的。CBRAM工藝改變了其存儲單元的電阻,提供了更高的可靠性。

CBRAM技術

Dialog的CBRAM技術適用于像所有物聯(lián)網解決方案一樣要求低功耗的應用。應用范圍包括從5G到人工智能,這些領域對讀/寫速度有很高要求,但同時要求降低生產成本。像工業(yè)應用這種需要對嚴苛環(huán)境有一定耐受能力的應用也偏愛使用該技術,該技術也可用于汽車行業(yè)。

近期,Dialog半導體公司工業(yè)應用IC副總裁Raphael Mehrbians在接受EE Times Europe采訪時,分析了CBRAM的重要性,談到了Dialog在收購Adesto之后采取的戰(zhàn)略。與格芯的合作證明了該技術得以很好地使用。

與傳統(tǒng)的嵌入式NVM不同,CBRAM技術不需要高電壓來改變記憶單元狀態(tài)。“這不僅使它能夠集成到標準邏輯中,還意味著進出陣列的數據路徑的電壓相對較低。為了從存儲器中讀取數據,將低電壓施加到選中的柵極,使用典型的傳感技術即可提取記憶單元的電阻。” Mehrbians說。

CBRAM產品的截面展示了其易于在標準CMOS工藝中集成(圖片來源:Dialog半導體公司)

● 該技術的主要電氣特性可以總結如下:

● CBRAM單元由1個選擇的晶體管和1個可編程非易失性電阻組成。

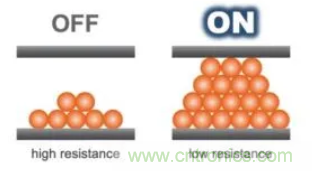

● CBRAM是一種電化學單元,它通過原子的電動運動來改變狀態(tài)。

● 邏輯1由具有導通時的低電阻單元表示。

● 邏輯0由具有截止時的高電阻單元表示。

● 通過施加相反極性的電壓脈沖將其編程為1和將其擦除為0。

● 高可靠性、100K 擦寫次數、10年數據存儲。

● 高熱穩(wěn)定性,兼容回流焊

● 寫 @ <3V

● 讀 @ <0.8V

正如Dialog所指出的,該技術的主要優(yōu)勢是功耗和成本。“CBRAM技術的固有特點是低電壓和低功耗。對于需要低電壓/低功耗NVM的嵌入式系統(tǒng)而言,這是很重要的優(yōu)勢。CBRAM簡單的單元結構僅通過增加幾道后道工序的掩膜即可方便地插入標準CMOS邏輯中,顯著低于傳統(tǒng)嵌入式閃存所需的數量。與其他NVM技術相比,后道工序的插入還提供了優(yōu)越的可擴展性。”Mehrbians說。

CBRAM將于2022年在格芯的22FDX平臺上作為嵌入式NVM選項提供投入生產。當電源斷開時,像RAM(隨機訪問存儲器)這樣的易失性存儲器會丟失它們存儲的數據,而NVM會在電源斷開后保存存儲在其中的數據。

“傳統(tǒng)嵌入式NVM的挑戰(zhàn)包括:擴展到28nm以下的先進工藝節(jié)點、傳統(tǒng)CMOS的成本顯著增加、 以及在訪問時間和功耗方面的性能。”Mehrbians說。

圖2:CBRAM的工作原理(圖片來源:Dialog半導體公司)

他補充說:“該技術適用的應用包括先進MCU、連接性產品和安全性應用。這些通常是更智能的終端設備所要求的,這些設備需要更多的智能(AI),以及安全性和先進通信協(xié)議,如NB-IoT。”

Dialog強調了嵌入式NVM與外部存儲器相比的優(yōu)勢,主要是因為IO沒有外露。在CBRAM中,實際上不可能通過物理分析來檢測記憶單元的狀態(tài)。此外,記憶單元的狀態(tài)不受磁場和輻射的影響(圖1和2)。

通過IP定制,客戶可以修改CBRAM單元來優(yōu)化他們的SoC設計,提高安全性,或者可以對單元進行調整以用于新的應用。

作者:Maurizio Di Paolo Emilio,EE Times Europe

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯(lián)系小編進行處理。

推薦閱讀: