【導(dǎo)讀】首先來看通過二極管并聯(lián)LDO的電路圖。采用二極管并聯(lián)LDO連接方法,由于輸出路徑中有二極管,因此輸出電壓僅下降二極管正向電壓(以下簡稱“VF”)的量。所以,要想得到預(yù)期的輸出電壓,需要采取諸如將二極管VF添加到LDO的輸出電壓設(shè)置值中等措施。

在上一篇文章《什么是LDO線性穩(wěn)壓器的并聯(lián)?》中,提到了有兩種并聯(lián)LDO的方法。本文中將介紹第一種方法:使用二極管并聯(lián)LDO的方法。

使用二極管并聯(lián)LDO

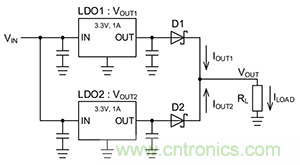

首先來看通過二極管并聯(lián)LDO的電路圖。采用二極管并聯(lián)LDO連接方法,由于輸出路徑中有二極管,因此輸出電壓僅下降二極管正向電壓(以下簡稱“VF”)的量。所以,要想得到預(yù)期的輸出電壓,需要采取諸如將二極管VF添加到LDO的輸出電壓設(shè)置值中等措施。另外,每個二極管的VF會有個體波動,而且還會因負(fù)載電流和溫度而異,因此,無法期待精確的輸出電壓精度。

通過二極管連接兩個LDO輸出時的電路

如上一篇文章所述,這個電路也是由輸出電壓高的LDO供給電流,但由于流過的電流因二極管的VF而異,因此可以在一定程度上吸收兩個LDO之間的電壓差。輸出電壓的平衡關(guān)系可以通過以下公式來表示:

VOUT1-VF1(IOUT1)=VOUT2-VF2(IOUT2)

VOUT1:LDO1的輸出電壓

VOUT2:LDO2的輸出電壓

VF1(IOUT1):IOUT1的D1的VF

VF2(IOUT2):IOUT2的D2的VF

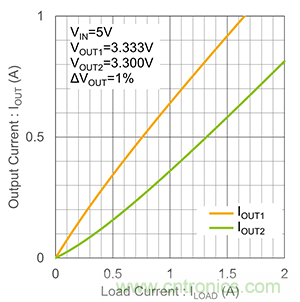

例如,從圖中可以看出使用3.3V、1A輸出的LDO,且LDO1的輸出電壓比LDO2高1%時,各LDO供給負(fù)載的輸出電流是如何分配的。

在負(fù)載電流為1A的節(jié)點,即使LDO的輸出電壓差僅為1%,但電流分配卻有很大差異:LDO1為0.64A,LDO2為0.36A。

輸出電壓差為1%時的輸出電流分配

接下來,圖中給出了兩個LDO間的輸出電壓差對輸出電流的影響。

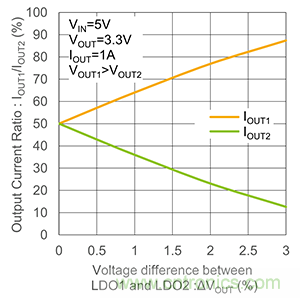

下圖表示LDO1比LDO2的輸出電壓高時各LDO的輸出電流之比。當(dāng)兩個LDO的輸出電壓完全相同時,輸出電流的比率為50%(平均分配輸出電流),但隨著輸出電壓差的增加,電流比率的差也會隨之增加。例如假設(shè)LDO1的輸出電壓波動+1%、LDO2的輸出電壓波動-1%,則LDO1的電流輸出為77%、LDO2的電流輸出為23%,電流分配很不平衡。

輸出電壓差對輸出電流比率的影響

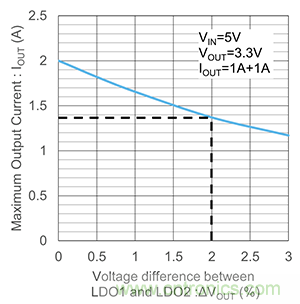

從下圖中可以看出當(dāng)使用最大推薦輸出電流值為1A的LDO時,LDO間的輸出電壓差對LDO并聯(lián)電路的輸出電流的影響。

如果LDO之間完全沒有電壓差,則兩個LDO的輸出電流相等,因此可以輸出2A(1A+1A)的電流。但隨著LDO輸出電壓差的增加,能夠輸出的電流值越來越小。在LDO1的輸出電壓波動+1%、LDO2的輸出電壓波動-1%的條件下,使用最大推薦輸出電流值為1A的LDO時,當(dāng)兩個LDO中的一個達(dá)到1A時該LDO將達(dá)到最大輸出狀態(tài),因此相對于2A的輸出電流能力,最多只能輸出1.37A的電流。

輸出電壓差對最大輸出電流的影響

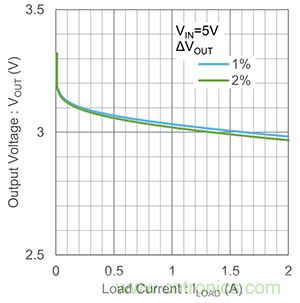

最后請看負(fù)載調(diào)節(jié)圖表。

與LDO輸出相比,輸出電壓下降了二極管VF的量,并且二極管VF隨負(fù)載電流的增加而增加,因此輸出電壓進(jìn)一步降低。

除了各LDO本來就有的負(fù)載調(diào)節(jié)器之外,二極管VF的影響也很大,而且輸出電壓的變化也很大,因此,如前所述,負(fù)載調(diào)節(jié)器并不理想。

負(fù)載調(diào)節(jié)

下一篇文章將介紹另一種方法:使用鎮(zhèn)流電阻進(jìn)行LDO并聯(lián)。

關(guān)鍵要點:

?在使用二極管進(jìn)行LDO并聯(lián)的方法中,由于輸出路徑中有二極管,因此輸出電壓會下降二極管VF的量,因此需要采取在LDO的輸出電壓設(shè)置中添加VF部分等相應(yīng)的對策。

?每個二極管的VF存在個體差異,而且還會因負(fù)載電流和溫度而異,因此,無法期待精確的輸出電壓精度(負(fù)載調(diào)節(jié)器)。

?盡管使用二極管可以緩和輸出電壓差的問題,但無論如何,由于兩個LDO的輸出電壓存在壓差,各LDO的輸出電流分配還是具有很大波動。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請電話或者郵箱聯(lián)系小編進(jìn)行侵刪。