【導(dǎo)讀】我們有能力創(chuàng)造一些能保持前代性能并且更好更小的電子設(shè)備,例如今天的可穿戴設(shè)備、智能手機(jī)或平板電腦,這是由于很多因素超過摩爾定律而快速發(fā)展,從而能夠從底層的嵌入組件發(fā)展到今天把它們封裝在一起。關(guān)于后者,扇出晶圓級(jí)封裝(FOWLP)正在迅速成為新的芯片和晶圓級(jí)封裝技術(shù),并被預(yù)測會(huì)成為下一代緊湊型,高性能的電子設(shè)備的基礎(chǔ)。

我們有能力創(chuàng)造一些能保持前代性能并且更好更小的電子設(shè)備,例如今天的可穿戴設(shè)備、智能手機(jī)或平板電腦,這是由于很多因素超過摩爾定律而快速發(fā)展,從而能夠從底層的嵌入組件發(fā)展到今天把它們封裝在一起。關(guān)于后者,扇出晶圓級(jí)封裝(FOWLP)正在迅速成為新的芯片和晶圓級(jí)封裝技術(shù),并被預(yù)測會(huì)成為下一代緊湊型,高性能的電子設(shè)備的基礎(chǔ)。

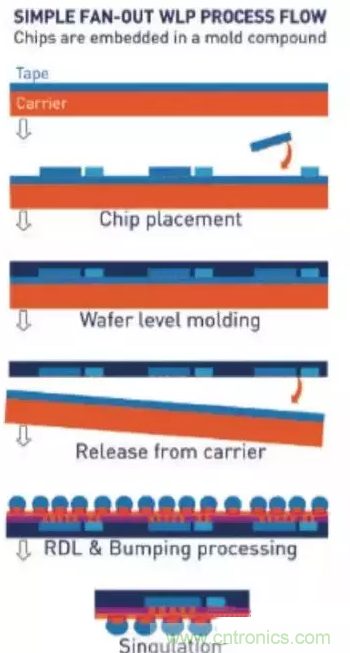

而用常規(guī)的倒裝芯片 WLP 方案中 I/O 端子散布在芯片表面面積,從而限制了 I/O 連接的數(shù)目,F(xiàn)OWLP 在一個(gè)環(huán)氧模制化合物(EMC)中嵌入每個(gè)裸片時(shí),每個(gè)裸片間的空隙有一個(gè)額外的 I/O 連接點(diǎn),這樣 I/O 數(shù)會(huì)更高并且的對(duì)硅利用率也有所提高。再分布層(RDLs)由物理氣相沉積(PVD)形成,并和隨后的電鍍以及微影圖案,重新規(guī)劃從裸片上的 I/O 鏈接到外圍環(huán)氧樹脂區(qū)域的路線。

圖 1 農(nóng)村配網(wǎng)和住宅小區(qū)

FOWLP 處理流程

利用 FOWLP,具有成千上萬 I/O 點(diǎn)的半導(dǎo)體器件可通過兩到五微米間隔線實(shí)現(xiàn)無縫連接,從而使互連密度最大化,同時(shí)實(shí)現(xiàn)高帶寬數(shù)據(jù)傳輸。去除基板顯著節(jié)約了成本。

伴隨 FOWLP,如今我們才有能力在這些模片上嵌入一些異構(gòu)設(shè)備包括基帶處理器,射頻收發(fā)器和電源管理 IC,從而實(shí)現(xiàn)了最新一代的超薄可穿戴和移動(dòng)無線設(shè)備。因?yàn)椴婚g斷的線和節(jié)約的空間,F(xiàn)OWLP 有潛力適用于更高性能的設(shè)備,包括內(nèi)存和應(yīng)用處理器,F(xiàn)OWLP 能夠應(yīng)用到新的市場,包括汽車和醫(yī)療應(yīng)用甚至更多。

今天業(yè)內(nèi)領(lǐng)先的 FOWLP 應(yīng)用產(chǎn)商包括了 Amkor, ASE, Freescale, NANIUM, STATS ChipPAC, 和臺(tái)積電,臺(tái)積電由于其廣泛報(bào)道的與蘋果公司生產(chǎn) iphone7 的 a10 處理器的合同,成為最受注目的供應(yīng)商 – 據(jù)說此部分歸功于臺(tái)積電成熟的基于 FOWLP 的 inFO 技術(shù)。

據(jù)研究公司 YoleDéveloppement 公司于 2015 年 9 月發(fā)布的名為“FO WLP Forecast update 09/2015”的報(bào)道,臺(tái)積電發(fā)布的 inFO 格式有望把 FOWLP 的工業(yè)封裝收益從 2015 年的$ 240M 在 2020 年增至$ 2.4B。隨著預(yù)期的 54%復(fù)合年增長率,Yole 預(yù)計(jì) FOWLP 將成為半導(dǎo)體工業(yè)里發(fā)展最快的先進(jìn)封裝技術(shù)。

發(fā)熱量低,高速處理

所有扇出晶圓以單裸片嵌入 EMC 為特征,旋轉(zhuǎn)介質(zhì)圍繞著 RDL。這些材料呈現(xiàn)一些獨(dú)有的問題,包括吸濕性,過量放氣和有限的耐熱性。如果不妥善處理,在金屬沉積階段的污染會(huì)危及接觸電阻。

而傳統(tǒng)的硅電路可承受的熱量高達(dá) 400℃,可以在一分鐘內(nèi)進(jìn)行脫氣。FOWLP 中使用的介質(zhì)和 EMC 耐熱性接近 120℃,溫度超過這個(gè)閾值會(huì)導(dǎo)致分解和過度晶圓翹曲。在這樣低的溫度下脫氣晶片,自然需要較長的時(shí)間量,并且大大減少了常規(guī)的濺射系統(tǒng)的吞吐量。

多晶片脫氣(MWD)的技術(shù)已經(jīng)成為一個(gè)引人注目的解決方法,在晶片單獨(dú)轉(zhuǎn)移到后續(xù)的預(yù)清潔和濺射沉積之前,高達(dá) 75 個(gè)的晶片可以并行在 120℃下脫氣,而不會(huì)破壞真空狀態(tài)。

用這種方法,晶片被動(dòng)態(tài)地在干凈,高度真空條件下泵浦,將加熱晶片的輻射熱直接傳遞給低于封裝應(yīng)用規(guī)定的溫度

在 MWD 內(nèi)每個(gè)晶片所花時(shí)間達(dá)到 30 分鐘,但因?yàn)樗鼈兪遣⑿刑幚淼模?ldquo;干”晶片每 60 至 90 秒輸出進(jìn)入到金屬沉積,每小時(shí)晶片輸出數(shù)在 30 到 50 之間。相比于單晶片脫氣技術(shù),此方法使 PVD 系統(tǒng)流量增大 2-3 倍。基于鈍化厚度增加的更低熱預(yù)算的材料出現(xiàn),更長時(shí)間的脫氣對(duì)系統(tǒng)容量不會(huì)產(chǎn)生影響。

這些好處是不容易實(shí)現(xiàn)的,除非我們能夠克服隨之而來的翹曲挑戰(zhàn)。環(huán)氧模晶片可以在固化后翹曲,翹曲的尺寸和形狀是由嵌入晶片的位置、晶片形狀和密度決定的。因此,一個(gè) FOWLP PVD 系統(tǒng)必須能夠使化溫度引起的形狀變化達(dá)到最小,和能夠容納彎曲度達(dá) 10mm 的晶片。工業(yè)中對(duì)于可接受的彎曲閾值可能低于 6mm,但是,在一個(gè) 6mm+翹曲的基板上完成均勻厚度的導(dǎo)體是不太容易。

完整至上

成功脫氣后,但在金屬沉積之前,F(xiàn)O 晶片在等離子體蝕刻模塊中預(yù)清潔。這有助于從觸頭去除微量氧化物層,但是由于觸頭周圍的有機(jī)介質(zhì)的混合物,將導(dǎo)致碳堆積于室壁。這些碳不易粘附到陶瓷腔室的表面,并且如果不仔細(xì)管理,可能會(huì)導(dǎo)致早期顆粒破裂。

新原位粘貼技術(shù)使這些沉積碳在預(yù)清洗過程中更好地吸附在室表面,實(shí)現(xiàn)超過 6000 片晶圓的保護(hù)性間隔維持。這種方法可以通過減少專用晶片糊劑的頻率,大大提高產(chǎn)量。使用傳統(tǒng)技術(shù),每生產(chǎn) 10 至 20 個(gè)晶片就要為室粘貼而暫停生產(chǎn)。

FOWLP 對(duì)于超小型、高 I/O 電子設(shè)備的好處,比主流 FOWLP 所面臨的上述技術(shù)壁壘要重要的多。有了克服阻礙 FOWLP 工藝的脫氣,翹曲和完整性這些困難的能力,電子產(chǎn)品制造商可以消除影響生產(chǎn)速度和產(chǎn)率的阻力,同時(shí)釋放 FOWLP 的全部潛力。