【導(dǎo)讀】工程師都知道最讓人頭疼的就是:由PCB設(shè)計所引起的信號完整性問題。如何解決呢?本文通過Mentor信號完整性工具“Hyperlynx” 進行仿真分析,總結(jié)了一套高速電路設(shè)計提供布局布線的分析方法,串行總線以及其它高速電路的布線設(shè)計提供了理論依據(jù)。

通用串行總線USB (Universal Serial Bus)協(xié)議從1.0版本發(fā)展到現(xiàn)在,由于數(shù)據(jù)傳輸速度快,接口方便,支持熱插拔等優(yōu)點使USB設(shè)備被越來越多人使用,目前,市場上以USB2.0為接口的產(chǎn)品越來越多,而繪制符合要求的PCB板在USB設(shè)備應(yīng)用中起重要作用。但在實際生產(chǎn)設(shè)計中,由于USB的傳輸速率較高,而系統(tǒng)中電路板上元器件的分布、高速傳輸布局布線等各類參數(shù),引起高速信號的完整性缺陷的,所以由PCB設(shè)計所引起的信號完整性問題是高速數(shù)字PCB(印制電路板)生產(chǎn)設(shè)計者必須關(guān)心的問題。本文通過Mentor信號完整性工具“Hyperlynx” 進行仿真分析,總結(jié)了一套高速電路設(shè)計提供布局布線的分析方法,串行總線以及其它高速電路的布線設(shè)計提供了理論依據(jù)。

1 通用串行總線

通用串行總線(USB)技術(shù)是為了彌補傳統(tǒng)微機外部總線的不足而設(shè)計的,隨著應(yīng)用的擴展,USB的傳輸速率不斷提高,USB2.0傳輸速度為高速480Mb/s。

對于USB信號的傳輸,信號完整性是核心指標(biāo)。USB總線應(yīng)用差分信號傳輸數(shù)據(jù),在傳輸過程采用NRZI編碼。在上位機與USB設(shè)備的交互中,根據(jù)數(shù)據(jù)傳輸雙工或半雙工的狀態(tài)不同,工作于差分態(tài)、靜止態(tài)和單終端三種狀態(tài),其相應(yīng)的電壓或電壓差也有所不同,傳輸協(xié)議以此判斷設(shè)備速率和信號數(shù)據(jù)。

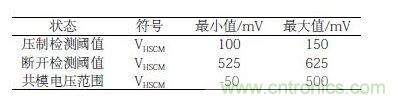

在高速系統(tǒng)中,差分線上高速信號的壓制檢測閾值、斷開檢測閾值和共模電壓也都有一定的范圍要求,如表1所示。其中,共模電壓典型值為200mV,另外,其差分輸入信號電平必須滿足高速接收眼圖的要求。

表1 高速信號的輸入電平

2 信號完整性分析

2.1 傳輸線基礎(chǔ)

USB總線采用差分方式傳輸信號,兩條傳輸線分別由不同的驅(qū)動器來驅(qū)動,其中一條用來傳輸本身的信號,另一條用來傳輸相應(yīng)的互補信號,接收端信號為兩者的電位差,用以識別傳輸線上包含的信息,從理論上來講,兩條任意的傳輸線都可以用來實現(xiàn)差分對。

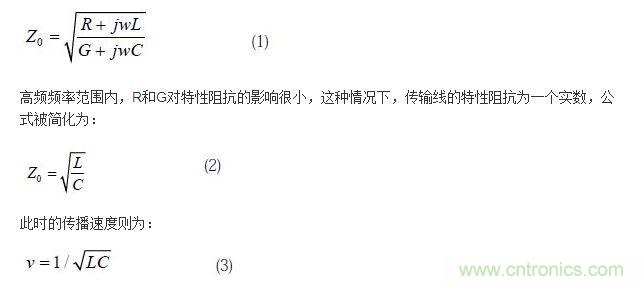

傳輸線內(nèi)的信號在傳輸過程中,將即時信號外加電壓與內(nèi)通電流的比值稱為信號的瞬態(tài)阻抗。當(dāng)傳輸線沿途的瞬態(tài)阻抗為恒定值時,這個值就被稱為傳輸線的特性阻抗,表達式為:

特性阻抗是阻抗匹配的一個重要參數(shù)。阻抗匹配關(guān)系到信號完整性問題,如反射、振鈴等參量的控制。差分對匹配一般采用兩種方式:π型和T型。

[page]

2.2 高速USB信號的眼圖

眼圖就是由多個周期的數(shù)字信號波形疊加而形成的圖形,形狀與眼睛類似,因此被稱為眼圖。數(shù)字信號的眼圖能清楚反映互連設(shè)計是否導(dǎo)致不能容忍的誤碼率。在高速串行應(yīng)用中,通行的做法是采用眼圖驗證串行鏈路是否滿足系統(tǒng)的性能要求的。

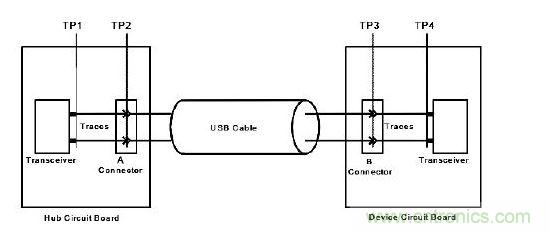

對于高速USB信號的發(fā)送和接收,USB使用眼圖來描述其各個位在傳輸時所需的電壓幅值和時間安排。圖1展示了高速USB系統(tǒng)的幾個眼圖測試點。其中,TP1和TP4對應(yīng)USB接口芯片的相應(yīng)管腳(D+和D-),它們分別被焊接在集線器和USB設(shè)備的電路板上;TP2對應(yīng)A型連接器的D+和D-管腳;TP3對應(yīng)B型連接器的D+和D-管腳(對于束縛電纜,其也可能是直接連接在電路板上)。

圖1 眼圖測試點

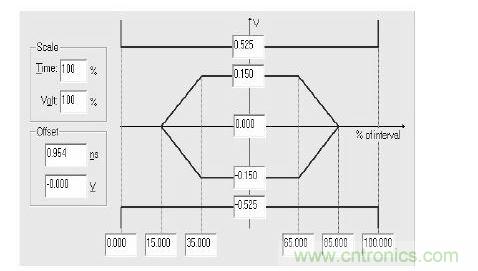

USB定義了6種眼圖模板,其中定義在集線器TP2點或在USB設(shè)備(使用非束縛電纜)TP3點處的眼圖模板,表示接收高速USB信號時所需的電壓分辨力,如圖2所示。

圖2 眼圖模板

[page]

3 信號完整性(SI)仿真

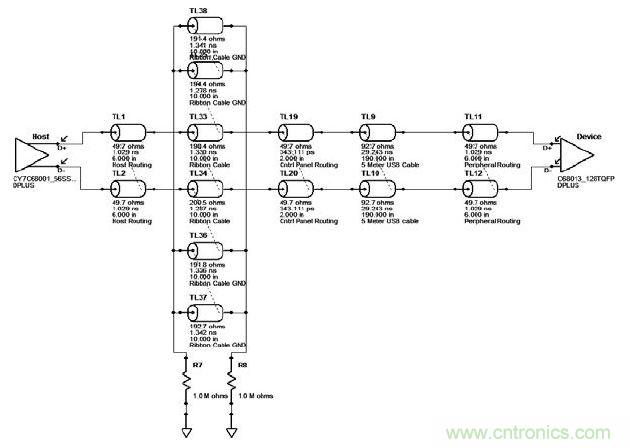

利用LineSim搭建USB2.0仿真原理圖,如圖3所示,其中包括主機控制器和外圍設(shè)備控制器,設(shè)置了從主機到外圍設(shè)備使用最大允許傳播延遲,模擬一個28AWG帶狀電纜和5米的USB電纜,以及外圍設(shè)備的布線。

圖3 USB仿真結(jié)構(gòu)模型

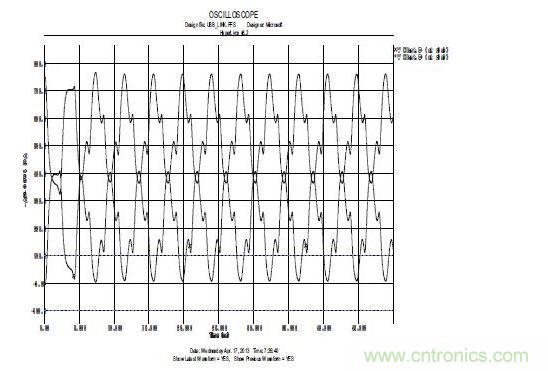

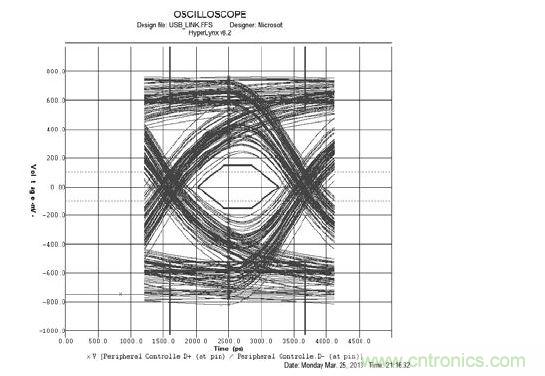

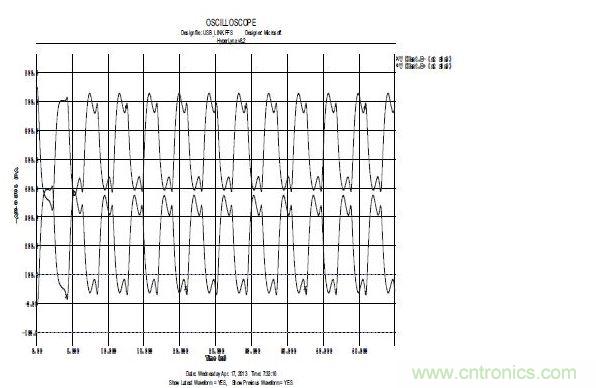

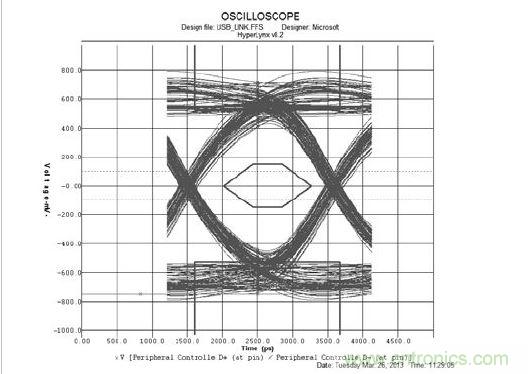

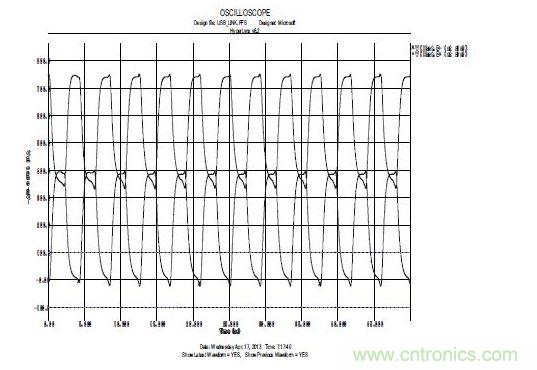

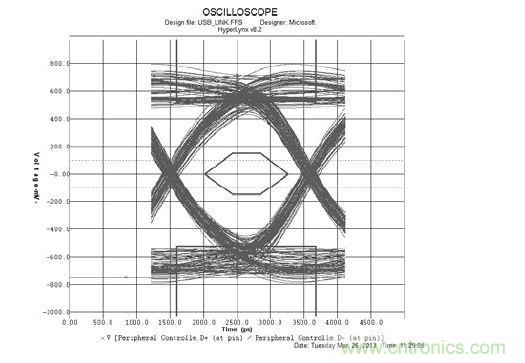

仿真得出差分信號的波形以及USB2.0接收端的眼圖,如圖4、圖5所示。其圖中弱的信號質(zhì)量是由于帶狀線的阻抗不連續(xù)產(chǎn)生,因此,將模型結(jié)構(gòu)中帶狀線的差分阻抗變化范圍為115 ohms~92ohms。調(diào)整之后差分信號波形如圖6所示,眼圖如圖7所示。

由上圖可以看出,經(jīng)過調(diào)整帶狀線的特征阻抗,差分信號波形有了明顯的改變,信號完整性問題得到了改善,眼圖寬度和高度均有增大,平均上升時間、平均下降時間均減小,平均下降速率和上升速率即斜率均增大,但是就其仿真來看,所得到的結(jié)果仍和理想的結(jié)果有一段距離,繼續(xù)改善模型結(jié)構(gòu)圖中其他相應(yīng)模塊的參數(shù),最終仿真得出了滿足USB2.0規(guī)范的眼圖和差分信號,如圖8和9所示。

圖4 差分信號波形

圖5 仿真結(jié)果

[page]

圖6 差分信號波形

圖7 仿真眼圖結(jié)果

圖8 差分信號波形

[page]

圖9 仿真眼圖結(jié)果

仿真數(shù)據(jù)結(jié)果為:

Peak-to-Peak Voltage:1.58V

Positive Overshoot: 229.4 mV;NegativeOvershoot: 198.2 mV

Avg fall time: 969.697ps;Avg rise time:960.398ps

Avg fall slew rate: 0.716 V/ns;Avg rise slewrate: 0.723 V/ns

Eye Width: 1.804ns;High level: 565.2mV;Low level: -592.2 mV

Eye Height: 862.6mV;High level: 565.2 mV;Low level: -592.2 mV

通過以上仿真過程及結(jié)果得出:眼圖的各項數(shù)據(jù)可以體現(xiàn)信號分析的性能指標(biāo)。最主要的是通過眼的寬度、眼的高度、平均上升時間、下降時間、平均上升速率和下降速率(即斜率)這些指標(biāo)能夠體現(xiàn)信號的優(yōu)劣程度。

4 結(jié)論

眼圖作為數(shù)字設(shè)計的參考依據(jù),圖中的眼寬、眼高、過沖、單位間隔和門限交叉抖動為重要參數(shù)依據(jù)。峰-峰值抖動=門限交叉抖動/單位間隔×100%。為了使接收器能夠正確地采樣數(shù)據(jù),眼圖必須滿足一定的高度和寬度,其具體參數(shù)由器件的特性決定,根據(jù)眼圖,可以知道實際情況是否滿足系統(tǒng)設(shè)計。

特性阻抗通常由PCB的層疊結(jié)構(gòu)和PCB走線寬度/間距決定的,首先明確好需要實現(xiàn)的信號的特性阻抗,確定關(guān)鍵信號的走線寬度/間距,選擇好板材的層疊結(jié)構(gòu),通常微帶線線寬、走線的銅皮厚度、微帶線到最近參考平面的距離以及PCB板材料的介電常數(shù)共同影響其特性阻抗,而影響差分線阻抗的主要參數(shù)為微帶線阻抗和兩根微帶線的線間距。當(dāng)兩根微帶線的線間距增加時,差分線的耦合效應(yīng)減弱,差分阻抗增大;線間距減少時,差分線的耦合效應(yīng)增強,差分阻抗減小。這在實際布線中的到了驗證,本文總結(jié)的USB電路布線設(shè)計方法可以為高速電路設(shè)計布局布線的分析方法,串行總線以及其它高速電路的布線設(shè)計提供理論依據(jù)。