【導讀】信號完整性是許多設計人員在高速數字電路設計中涉及的主要主題之一。信號完整性涉及數字信號波形的質量下降和時序誤差,因為信號從發(fā)射器傳輸到接收器會通過封裝結構、PCB走線、通孔、柔性電纜和連接器等互連路徑。

當今的高速總線設計如LpDDR4x、USB 3.2 Gen1/2 (5Gbps/10Gbps)、USB3.2x2 (2x10Gbps)、PCIe和即將到來的USB4.0 (2x20Gbps) 在高頻數據從發(fā)送器流向接收器時會發(fā)生信號衰減。本文將概述高速數據速率系統(tǒng)的信號完整性基礎知識和集膚效應、阻抗匹配、特性阻抗、反射等關鍵問題。

導讀

隨著硅節(jié)點采用10nm、7nm甚至5nm工藝,這可以在給定的芯片尺寸下實現高集成度并增加功能。在移動應用中,趨勢是更高的頻率和更高的數據速率,并降低工作核心電壓如0.9v、0.8V、.56V甚至更低以優(yōu)化功耗。

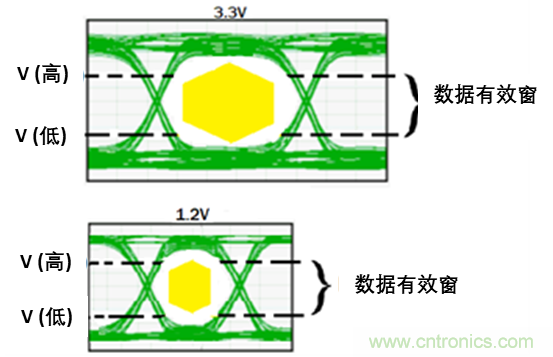

在較低的工作電壓下以較高的頻率工作會使閾值電平或給定位數據的數據有效窗口變小,從而影響走線和電源層分配功率以及“眼圖”的閉合度。

由較高頻率和較低工作電壓引起的閉眼,增加了數據傳輸誤差的機會,因而增加了誤碼率,這就需要重新傳輸數據流。重傳會導致處理器在較長時間處于有源模式以重傳數據流,這會導致移動應用更高的功耗并減少使用日 (DOU)。

圖1. 頻率和較低電壓對眼圖張開的影響

在給定的高頻設計中增加其他設計挑戰(zhàn)如信號衰減、反射、阻抗匹配,抖動等時,很明顯,信號損耗使接收器難以正確譯出信息,從而增加了誤差的機會。

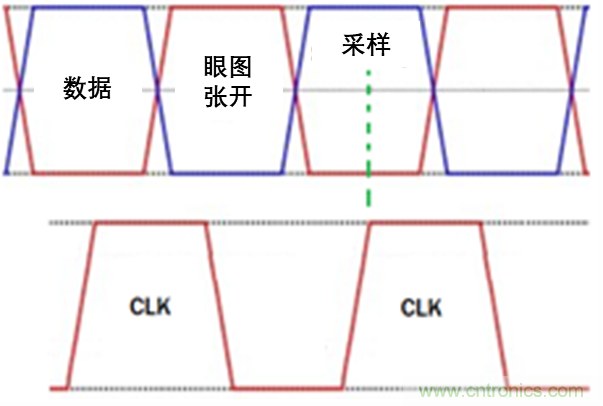

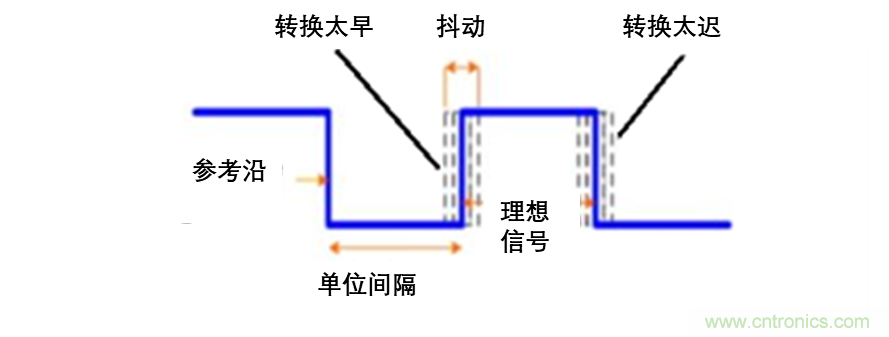

數據流中的時鐘采樣

在接收器處,數據是在參考時鐘的邊緣處采樣的。眼圖張開越大,就越容易將采樣CLK設置在給定位的中間以采樣數據。任何幅值衰減、反射或任何抖動,都將使眼圖更閉合并使數據有效窗口和有效位時間變得更窄,從而導致接收端出現誤差。

圖2. CLK采樣

現在,讓我們檢查何時需要將通道或互連視為傳輸線,并查看在智能手機或平板電腦等系統(tǒng)中傳輸損耗的一些主要原因。

高頻和傳輸線

低頻設計是指波長遠大于線長度且PCB走線和互連的電阻與頻率無關,因此傳輸線的影響可以忽略不計。

高頻設計是指波長遠小于線長度且走線的所有物理特性和互連尺寸都需要控制,以便具有一系列電氣特性的傳輸線可用于給定應用。

我們將互連視為傳輸線的時候是在最高頻率下工作時,走線長度可能超過該頻率波長的1/10。

此時,我們需要使用集總元件對走線建模,并考慮所有頻率相關元件,包括寄生電容和電感及其對信號衰減的影響。

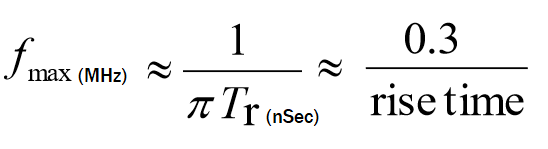

另一種確定在什么頻率下將互連線視為傳輸線的方法是考慮信號的上升時間 (tr)。

在大多數納米工藝節(jié)點中,高數據速率信號具有急劇的上升/下降時間,這要求將通道或任何互連視為傳輸線。當這些信號通過信道傳播時,其帶寬和傳輸受給定的信號上升時間控制。

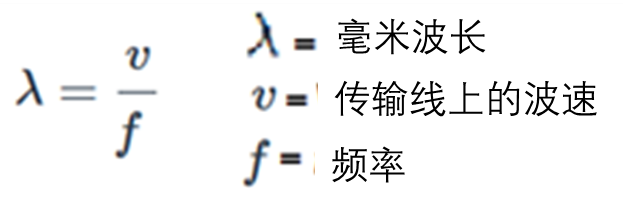

傳輸速度

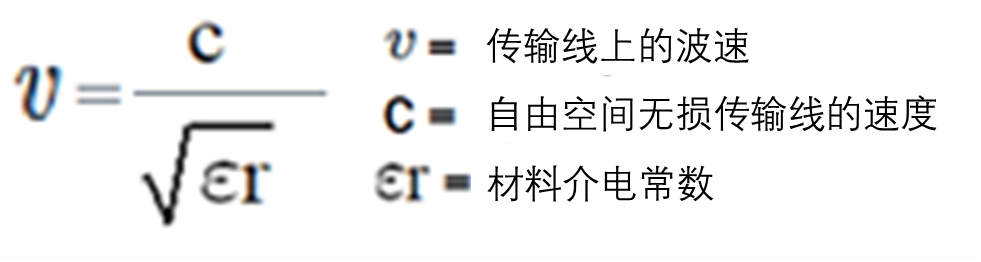

電信號是電磁波,其傳輸速度取決于其周圍材料的介電常數。傳輸速度的公式是

圖3. 傳輸線上的波速

自由空間(介電常數為1)無損傳輸的波速約為3 x 108 m/s,不同于介電常數為4的傳輸線的波速,后者導致波速降低一半或1.5 x 108 m/s。

在自由空間對比在PCB傳輸的波速差異將導致稱為傳播延遲 (Td) 的時間延遲,Td取決于傳播的媒介和信號必須傳播的距離。

Td(傳播延遲)=傳播距離/Vp(傳輸速度)

現在,當一個信號 (CLK) 在外層傳播而另一信號 (Data) 在內層傳播時,若我們在一側具有自由空間而在另一側具有介電常數時,情況會怎樣呢?

在許多設計中,高頻信號必須以互連電纜或撓性電纜作為傳輸路徑的一部分,這會對幅值和時序波形產生延遲和偏差。由于信號速度降低、串擾或介電材料吸收的任何能量而導致的時序偏差或任何其他損耗都會同時產生稱為抖動的時序和幅值偏差。

圖4. 抖動

在這里,設計人員必須匹配一系列信號之間的飛行時間。由于內層的DATA信號將傳播得較慢,因此我們必須減小DATA信號的長度以匹配CLK信號的飛行時間。

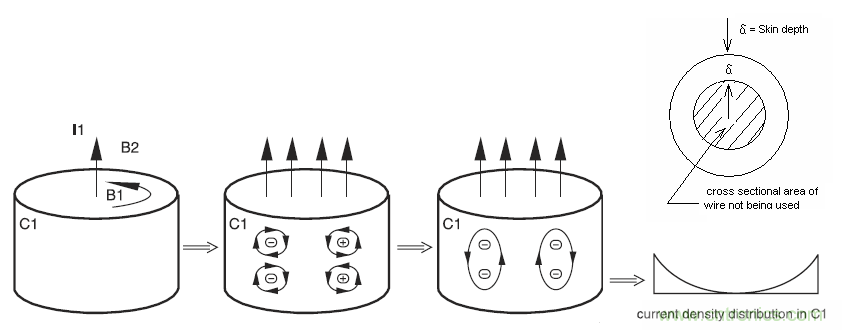

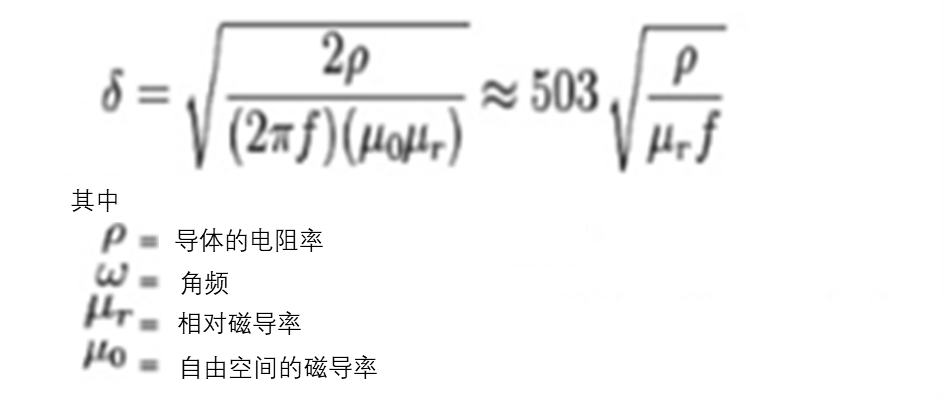

集膚效應

如果我們查看稱為C1的給定導體的一部分并通過它發(fā)送電流I(t),根據安培定律,將會產生與通過導體的電流成比例的磁通量。

如果我們僅考慮一個導體,附近沒有其他導體,那么通量線 (B1) 將在導體C1中沿與磁場B1相反的方向產生循環(huán)渦流。

圖5. 趨附效應引起的電流重新分布

隨著頻率增加,集膚效應將電流限制在導體厚度的較小部分,從而增加了有效電阻和相應的損耗。

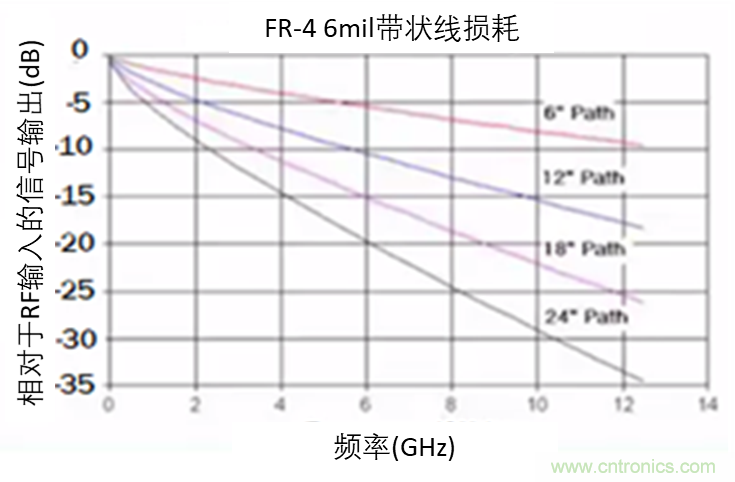

圖6. 由于頻率和走線路徑造成的信號損失

傳輸線和特征阻抗Zo

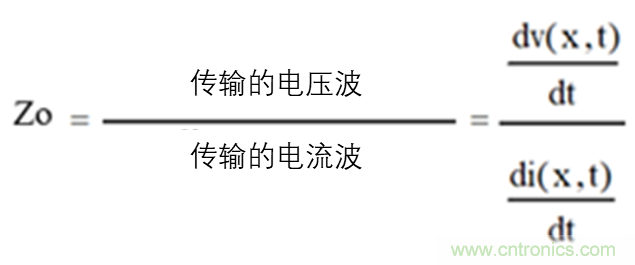

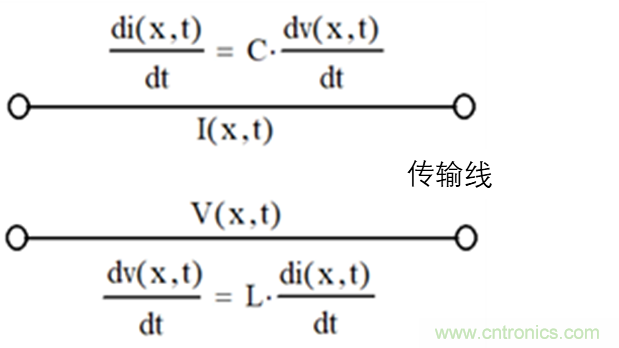

傳輸線上的電壓和電流一起傳播,并且是位置 (x) 和時間 (t) 的函數。傳輸線的特征阻抗 (Zo) 是與頻率相關的電阻,是傳輸的電壓波與傳輸的電流波之比

圖7. 傳輸線中的電壓和電流

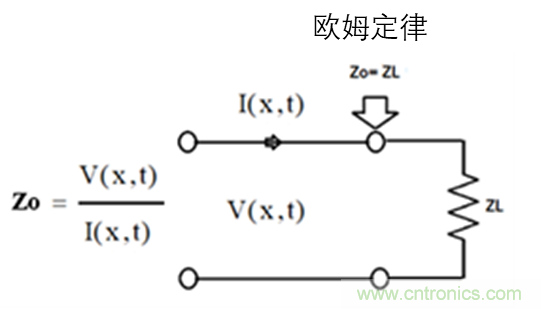

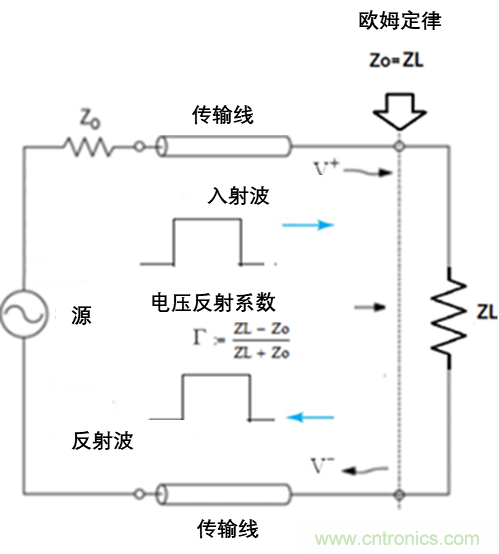

當電壓V (x,t) 和電流I (x,t) 一起傳播并達到端接阻抗時,歐姆定律要求V (x,t) /I (x,t) 等于端接阻抗 (ZL)。

圖8. 匹配Zo和ZL

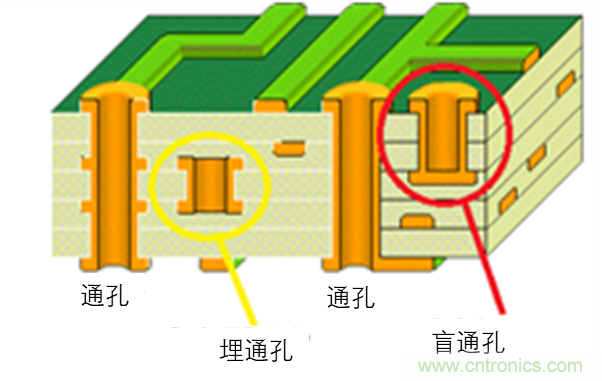

當高頻信號通過PCB中的路徑,通過或改變其從一層到另一層的路徑時,阻抗將發(fā)生變化。

觀察給定的PCB,我們可以看到有很多層、走線、通孔、連接,阻抗在任何給定點處都在變化,且自電容、互電容、自電感和互電感會產生寄生效應。

圖9. PCB層和阻抗變化

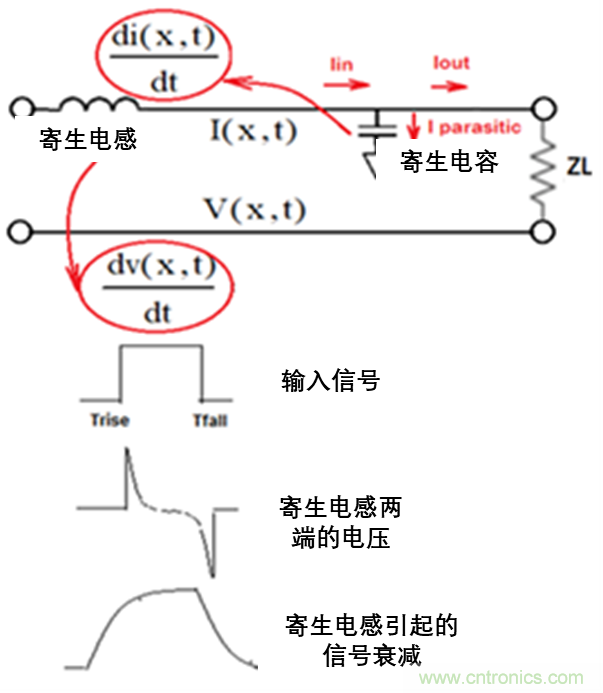

現在,讓我們引入一些集總元件,如寄生電感、電容、交流集膚電阻、直流電阻,它們存在于任何系統(tǒng)中。

可以看出,例如寄生電容 (Cdx) 如何改變電流分布,從而導致傳輸線的特征阻抗發(fā)生變化,并使Zo(傳輸電壓與傳輸電流之比)發(fā)生變化。

圖10. 含集總元件的傳輸線

隨著集膚效應降低傳入信號的幅值,寄生電感兩端的電壓會降低負載兩端電壓的上升和下降時間,從而影響信號質量和使信號衰減。

圖11. 寄生效應對Zo和信號完整性的影響

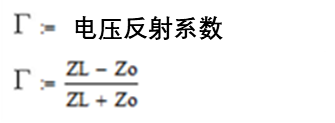

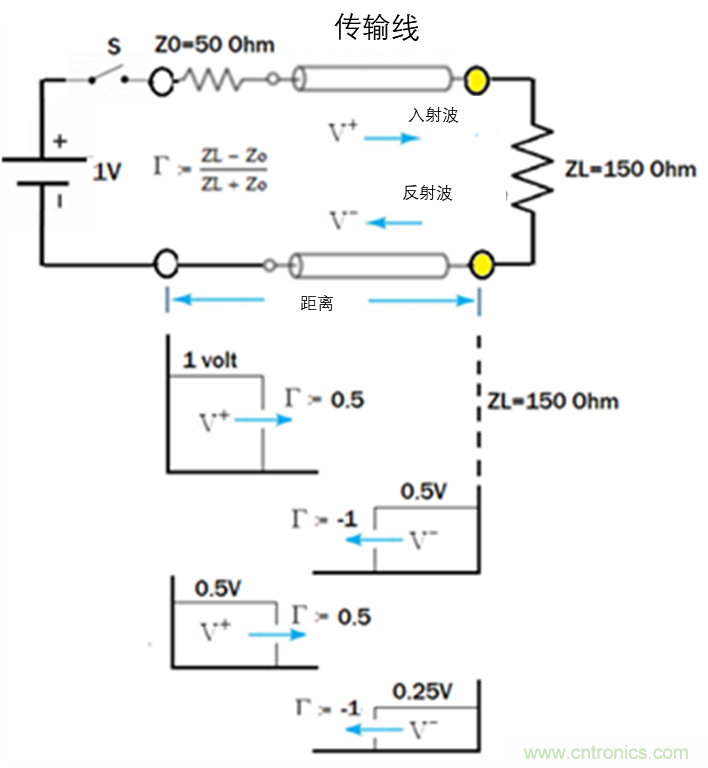

電壓反射系數

當高頻信號通過不同的路徑、通孔或改變其從一層到另一層的路徑時,阻抗將發(fā)生變化??刂七@些寄生信號并正確端接傳輸線,我們可以以最小的失真?zhèn)鬏斝盘枴?/div>

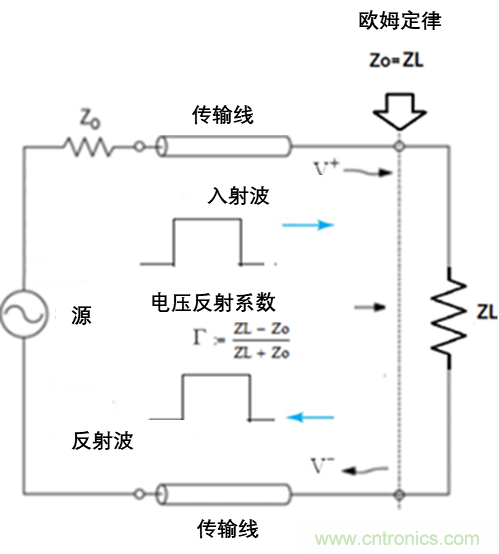

當終端阻抗 (ZL) 不等于線路的特征阻抗 (Zo) 時,必須有一對反射電壓和電流波,并且該反射信號將覆蓋在源信號上,導致失真。

請注意,當負載終端 (ZL) 等于傳輸線的特征阻抗 (Zo) 時,電壓反射系數等于零。這表明所有入射波都被匹配的負載終端吸收。

當電壓波和電流波一起傳播并達到端接阻抗時,總入射波加上V/I的任何反射波必須等于端接阻抗 (ZL)。

圖12. 入射波和反射波

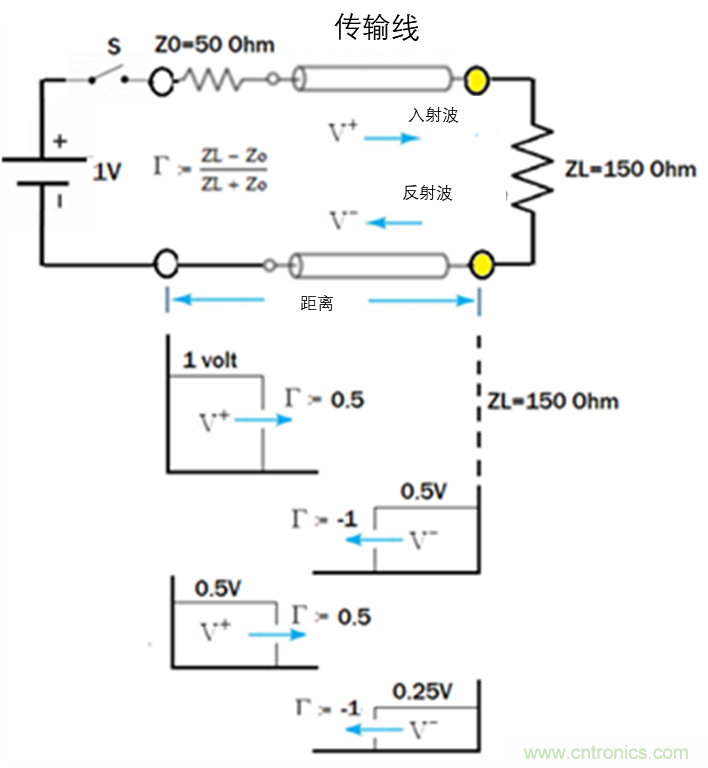

阻抗不匹配和反射

考慮一條50歐姆的傳輸線,端接150歐姆的端接電阻或一個過阻尼電路。為簡單起見,我們將電池的阻抗設置為0,這會將反射波強制返回負載。此外,設置波傳播給定長度的時間延遲(td=距離/Vp)?,F在,讓我們關閉開關 (s) ,看看負載發(fā)生了什么。

圖13. 連續(xù)反射波序列

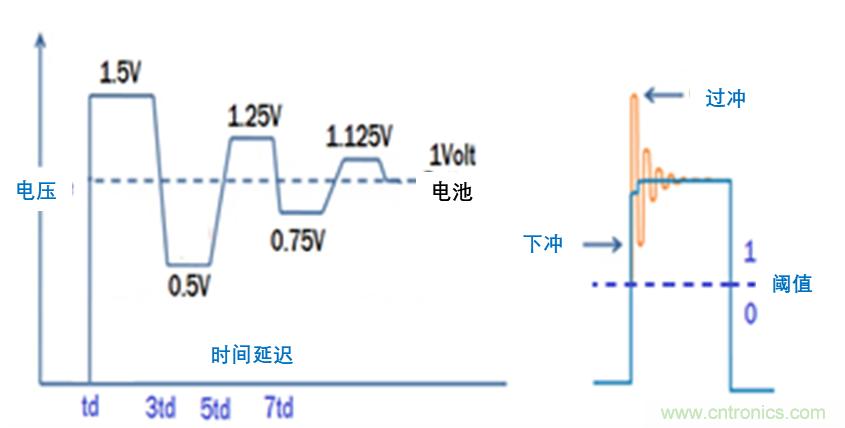

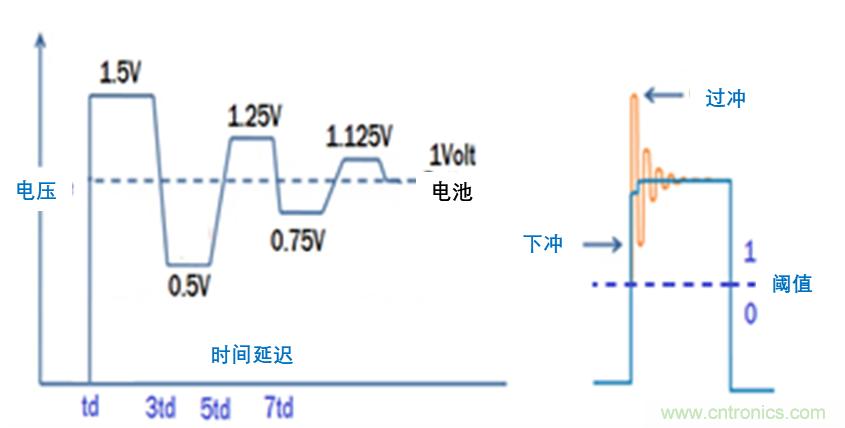

源和終端阻抗之間來回的連續(xù)反射波會導致信號覆蓋在源信號上,并在信號線上產生振鈴。

圖14. 反射引起的振鈴

在計算終端和源的反射系數時,我們可以得出到達終端的入射波量加上反射回源的反射波量。

圖14中具有較大電壓的過沖振鈴會給器件施加更多的輻射而使其過應力,并在相鄰走線之間產生更多的串擾。

另一方面,由振鈴或瞬態(tài)響應期間電壓軌下降引起的下沖都將增加更高的誤碼率。

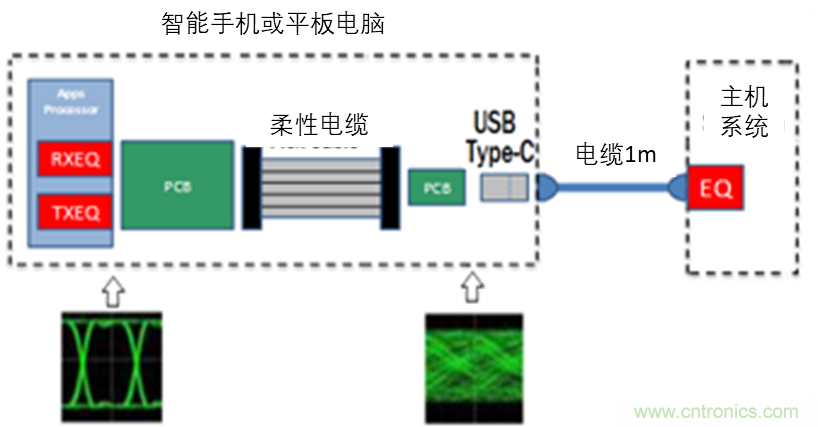

帶轉接驅動器和不帶轉接驅動器的系統(tǒng)

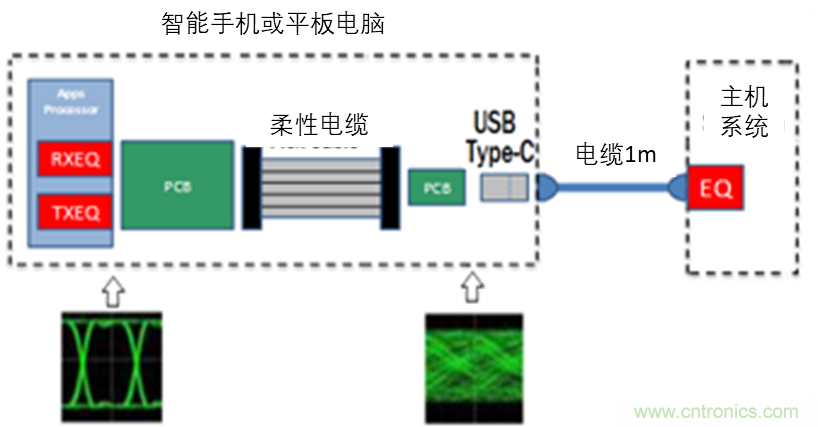

對于某些移動應用,如使用10Gbps數據速率的USB 3.1 Gen 2的移動應用,總損耗預算以dB為單位,包括所有互連通道損耗。損耗預算包括從硅到連接器的路徑中的任何損耗,如硅封裝、PCB走線、通孔、柔性、共模濾波器和連接器。

為了USB Type-C Gen 2系統(tǒng)保持好的信號質量而又不限制PCB的尺寸和設備的位置,轉接驅動器是最具性價比的方案。

考慮到像智能手機或平板電腦這樣的系統(tǒng),可以將其視為高頻數字信號從APP處理器封裝和引腳、PCB走線、通孔、連接器、柔性電纜和USB連接器傳輸而來,這些高數據速率信號可能在通過1m電纜之前就衰減。

圖15. 典型信號路徑及信號衰減

當信號通過信道傳播時,信號的幅值會衰減,且取決于信道的長度,這種衰減可能足以導致在高數據速率下出現信號完整性問題。

轉接驅動器作為信號調節(jié)器件,可以恢復在給定通道上已有損耗的信號,它可以增強恢復的信號的輸出,從而允許該信號傳播更長的距離和開眼以降低誤碼率。

圖16. 使用轉接驅動器

具有可編程差分輸出電壓的轉接驅動器確保驅動強度與線路阻抗、走線長度保持一致,并均衡信號和解決信號完整性問題。請記住,增加驅動器的差分輸出電壓將有助于改善接收信號,但同時也會增加噪聲和抖動。

總結

保持可接受的信號完整性,需要重視集膚效應、匹配的端接、反射、通孔、串擾、耦合及其對信號衰減的影響。

當走線的長度約為信號波長的1/10時,任何互連都應視為傳輸線。

影響信號完整性的因素,如信道損耗和由阻抗失配引起的信號反射,發(fā)生在數據從處理器通過PCB、通孔、柔性電纜或從PCB、通孔、柔性電纜到處理器的任何傳輸過程中。

在整個信號路徑中保持阻抗匹配對于接口至關重要,以防止反射并提供最大的功率傳輸。任何阻抗失配都會在線路上引起反射,增加抖動并可能損害信號質量。

如果沒有轉接驅動器,將很難或幾乎不可能在數據速率>10Gbps通過系統(tǒng)電氣和協議一致性測試。在不使用轉接驅動器進行短通道和長通道測試時,具有較高數據速率的給定信號的總傳輸通道距離可能會受到限制,并且不同設備之間的互操作性機會會降低。

推薦閱讀: