【導(dǎo)讀】在過去的20年間��,CareFusion Nicolet在EEG診斷系統(tǒng)領(lǐng)域的開發(fā)上一直扮演著先驅(qū)者的角色��。腦電圖(EEG)監(jiān)測可用于神經(jīng)系統(tǒng)分析,以進行睡眠研究��、腦功能區(qū)定位(Brain Mapping)和ICU病患大腦活動的監(jiān)測等�。隨著腦部研究和EEG診斷的持續(xù)突破�,人們期望EEG監(jiān)測裝置也能夠在傳統(tǒng)臨床環(huán)境以外的新環(huán)境中運作,而這些新的環(huán)境同時也引發(fā)新的設(shè)計挑戰(zhàn)��,本文將探討其中的一些挑戰(zhàn)��。

Harry Holt(ADI公司運算放大器應(yīng)用工程師):最近��,Bill�����、Matt和我就EEG前端設(shè)計的第一級——儀表放大器的各種利害權(quán)衡進行了一些討論。我們覺得將討論內(nèi)容與其它設(shè)計工程師分享可能會是有益的�。

Matt Du(ADI公司儀表放大器應(yīng)用工程師):對,Bill查看了我們的大量儀表放大器����,但最終結(jié)果是自行搭建儀表放大器。這在注重性能的應(yīng)用中是很少見的���,因此����,我們想闡明這一考慮過程���。Bill,你能大致說明一下你的設(shè)計目標(biāo)嗎����?

Bill Kolasa(CareFusion首席電氣工程師): 我們目前有一款基于儀表放大器的設(shè)計,它表現(xiàn)出色�����,但我們希望優(yōu)化某些性能特征�,同時降低其功耗��。

如同許多EEG和ECG設(shè)備設(shè)計者所知����,電極中的半電池電位差異可能會引起較大的直流失調(diào)���,測量系統(tǒng)必須能夠容忍此失調(diào)����。我們的現(xiàn)有系統(tǒng)在設(shè)計上可以處理高達±900 mV的失調(diào)����。為了應(yīng)付在現(xiàn)場的不同電極類型以及環(huán)境條件,我們希望將容差提高到±1300 mV�。

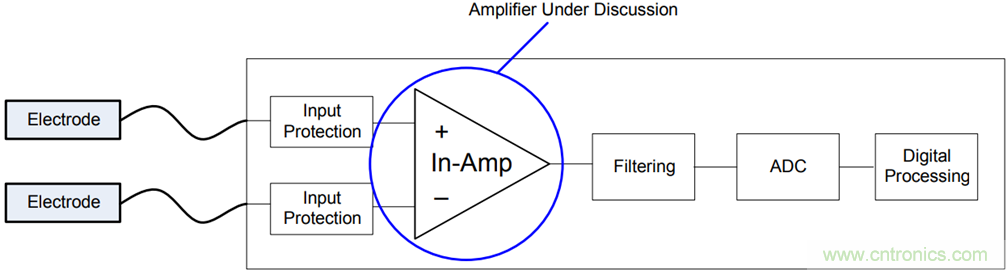

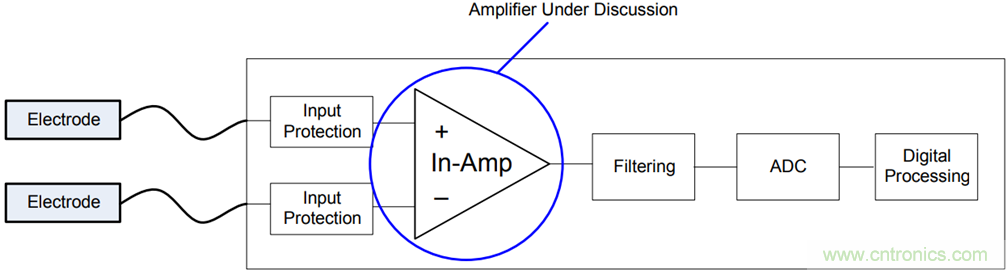

圖1. EEG信號鏈

與此同時,我們正在考慮電池供電設(shè)計的可能性����,因此需要大幅降低所有器件的功耗,其中也包括儀表放大器��。目前的功耗是每通道28 mW����,我們希望設(shè)法將其降低到10 mW或更低��。為了降低功耗��,我們允許噪聲提高����。

Matt:在我們的ECG和EEG客戶中�,這種權(quán)衡取舍非常常見。對于ECG和EEG前端設(shè)計����,噪聲、失調(diào)處理能力與功耗之間存在固有的取舍關(guān)系�。

大部分的儀表放大器具有因為減法器級的噪聲而導(dǎo)致的大量噪聲成分。在高增益應(yīng)用中�����,其影響不大��,因為此噪聲會在輸出端保持恒定�����,而與增益無關(guān)�����。因此�,當(dāng)折合到輸入端時,噪聲相當(dāng)小�。

不幸的是,在EEG和ECG應(yīng)用中����,增益會被來自于電極的較大失調(diào)所限制。如果你希望使用大增益以獲得良好的噪聲性能�����,那么必須采用大電源才能處理較大的失調(diào)���。

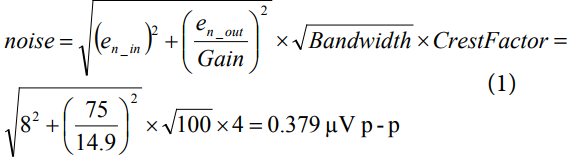

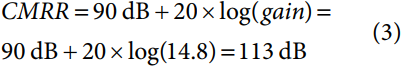

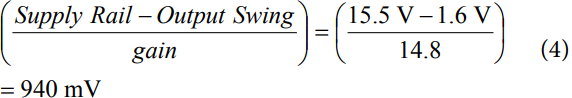

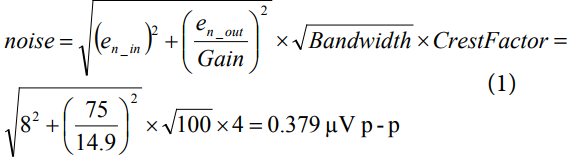

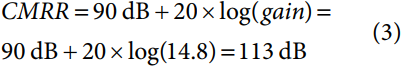

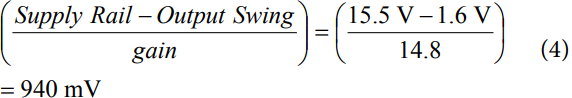

Bill:這就是我們在采用AD8221儀表放大器的先前設(shè)計當(dāng)中采取的措施�。輸出噪聲為75 nV/√Hz�����,輸入噪聲為8 nV/√Hz���。為了降低大量輸出噪聲在折合到輸入端時所造成的影響��,我們將AD8221設(shè)定至14.8的增益(噪聲計算詳情參見等式1和2)����。該增益也會將共模抑制提高23 dB,因為共模增益為1(參見等式3)�����。但是�����,為了以此增益來處理900 mV電極失調(diào)�,我們必須使用±15.5 V 直流電源(參見等式4)。我們的EEG放大器由64個這種通道組成����,對于電池供電應(yīng)用來說,功耗太大�。

我一直在等待ADI公司推出低輸出噪聲的儀表放大器���。什么時候能實現(xiàn)呢����?

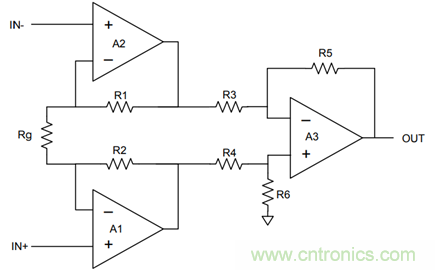

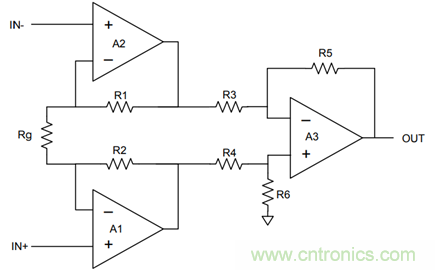

Matt: 儀表放大器的輸出噪聲主要由6個電阻決定(圖2 中的R1至R6),我們可以降低這些電阻的值�����,但這樣會有幾個缺點:1) 儀表放大器現(xiàn)在必須使用更多電流驅(qū)動這些電阻��。為了在這種較高驅(qū)動條件下保持良好的線性度����,我們必須構(gòu)建更強的放大器,它會消耗更多電流��。這樣您將面臨雙重不利的處境:一方面必須提供額外的電流流經(jīng)這些小值電阻����,另一方面必須提供更多電流以實現(xiàn)更強的放大器。

圖2. 標(biāo)準(zhǔn)儀表放大器配置

Bill:對于我的功耗問題�����,這似乎不是好消息�。

Matt: Rg增益設(shè)置電阻會變得更小,這在噪聲方面是件好事�����,但在較大差分過壓條件下,這還不夠好����。它會使放大器輸入端處理高增益下的大差分電壓的性能變差??梢酝ㄟ^增加電路來應(yīng)對,但這種電路會增加輸入噪聲��。

Bill:這對我們可能不是一個問題�,因為電極輸入上已經(jīng)存在保護電路。

Matt:隨著減法器電路中的電阻變小����,基準(zhǔn)電壓引腳的輸入阻抗也會變小。這意味著��,如果你希望用一個緩沖器驅(qū)動此引腳(這是此類應(yīng)用中十分常見的情況)���,那么在目標(biāo)頻率范圍內(nèi)�����,驅(qū)動放大器必須具有非常低的輸出阻抗。否則���,系統(tǒng)的CMRR相對于頻率的性能會下降����。相對于頻率的較低輸出阻抗需要較高功率的驅(qū)動放大器。

Bill:是的����,在我們的新設(shè)計中,我們要驅(qū)動那個引腳���,因此這會是一個問題����。我們花了些時間尋找緩沖器�����,它能提供與該引腳僅僅接地時相似的CMRR性能����。

回到最初的問題,我們使用AD8221����,采用±15.5 V電源供電���,電源電流為0.9 mA。我們希望通過降低儀表放大器耗用的電流和電源軌來降低功耗�����。于是����,我們開始尋找功耗更低但仍然能滿足其它性能要求的器件。

我們查看的一款儀表放大器是AD8235/AD8236AD8236����,它的功耗非常低,尺寸很小���,但噪聲太高����,最大供電軌為5 V�,無法滿足我們的直流失調(diào)要求。

Matt: 這些是基于CMOS的儀表放大器���,功耗40 A���,非常受功耗重于性能的ECG監(jiān)控應(yīng)用的歡迎,但不太適合CareFusion開發(fā)的診斷級EEG�����。

Bill:我們考慮的另一款器件是AD627���,它的功耗也非常小��,并且支持寬電源軌����。過去我們測試過它的噪聲���,知道相對于功耗而言���,它具有良好的性能。然而��,它采用的是SOIC封裝�,在今天來說��,尺寸較大�����,不利于縮小電路板的尺寸���。

Matt: 是的,也許我們得做點什么…

Bill:你們還有許多300 A到500 A電源電流及寬電源范圍的器件����,例如 the AD8226 和 AD8227。但是��,所有這些器件都具有至少20 nA的輸入偏置電流����,超過了本設(shè)計的低于5nA的額定要求。

Matt: 對于AD8226 和 AD8227等器件�,我們希望能夠測量低至負電源軌的電壓。我們使用一個較為簡單的輸入級來執(zhí)行測量��,不得不犧牲一些輸入偏置電流來達到目標(biāo)����。對于AD8221�,我們同時利用輸入偏置電流補償和Superbeta晶體管來將偏置電流降至數(shù)百pA典型值��,這讓我們的許多客戶感到滿意��,但不利的一面是����,我們放棄了輸入端的一些裕量��。

Bill�����,決定你的偏置電流要求的因素是什么�����?EEG電極的源阻抗是不是10 k左右����?對于AD8226AD8226,最大輸入偏置電流為27 nA���,因此電壓為270 uV�����,與來自電極的大失調(diào)相比���,這簡直微不足道��。你能告訴我們決定偏置電流要求的因素是什么嗎�?

Bill:5 nA要求來自于我們的一些放大器���,這些放大器必須應(yīng)付高得多的電極阻抗���。然而,該放大器具有低至DC的EEG顯示帶寬要求���。我們關(guān)心的是如何將電極阻抗變化引起的基線漂移效應(yīng)降至最低���。

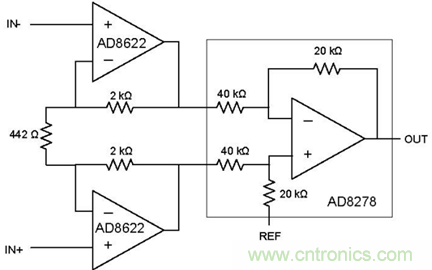

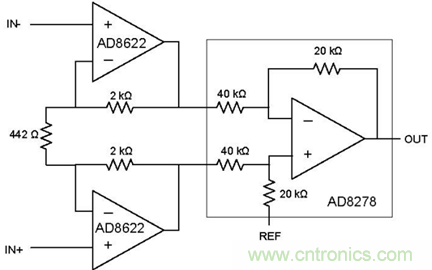

發(fā)現(xiàn)ADI公司以及其他廠商沒有任何一款儀表放大器滿足我們的要求之后,我們決定自行構(gòu)建�����。我們知道���,為了獲得100 dB以上的CMRR��,減法器級中的電阻必須匹配�����。過去我們試驗過匹配電阻網(wǎng)絡(luò)��,但發(fā)現(xiàn)這種網(wǎng)絡(luò)非常昂貴��。同時�����,我們似乎從來沒有獲得期望的CMRR性能�,可能是因為電路板的寄生電容影響��。我們發(fā)現(xiàn)差動放大器AD8278 具有我們需要的性能和功耗���。

Harry: 四電阻差動放大器比乍看起來更復(fù)雜��。對于理想的運算放大器��,CMRR受電阻匹配度限制(圖2中的R3-R6)�����。差動放大器的近似計算公式(參見參考文獻1)如下:

其中��,Ad為差動放大器的增益��,t為電阻的容差�����。因此�����,對于1倍增益和1%電阻���,CMRR = 50 V/V或大約34 dB��;對于0.1%電阻���,CMRR =500 V/V或大約54 dB。

Bill:我在你們的設(shè)計手冊中看到過類似的闡述(參見參考文獻2)�。

Harry: 上述公式適用于低頻情況。當(dāng)頻率較高時,CMRR可能會進一步下降���。例如����,如果因為PC板布局或內(nèi)部芯片布局的影響�����,兩個運算放大器輸入的輸入電容差為400 fF到500 fF��,電阻為10 k��,那么10 kHz時的交流CMRR會下降6 dB到7 dB�。如果系統(tǒng)中有一個20 kHz(或更高)開關(guān)調(diào)節(jié)器,這可能很重要�。

即使具有理想的電阻和平衡電容����,CMRR最終也會受運算放大器的限制。

差動放大器的性能主要分為兩類��。第一���,典型的高端電流檢測應(yīng)用需要在電流范圍的高端具有3%到5%的精度���。一個具有合理失調(diào)和1%電阻的低成本運算放大器可以達成此需求���。請記住,有一些低成本運算放大器可能具有低于50 dB的CMRR����,這一點常常被忽略掉。第二�,更精密的應(yīng)用,通常作為分立儀表放大器的第二級�����,處于0.1%到1%范圍����,具有超過70 dB到80 dB的CMRR。這可以利用一個良好的運算放大器�����、四個具有低溫度系數(shù)(TC)的匹配電阻(最好是比例匹配TC)�,以及謹慎的PCB電路板布局來實現(xiàn)。考慮到總成本與電路板空間�����,單芯片差動放大器看起來極具吸引力���。我能明白Bill為什么選擇AD8278���;我們?yōu)樗隽似D苦的努力。

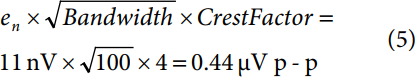

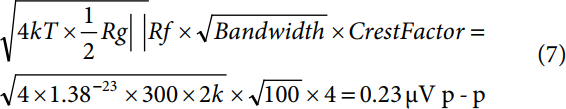

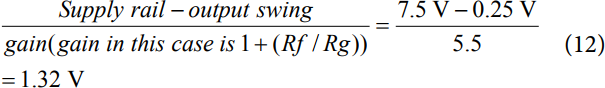

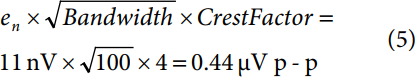

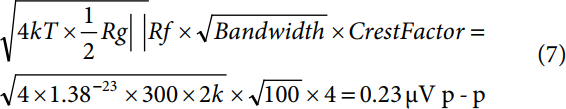

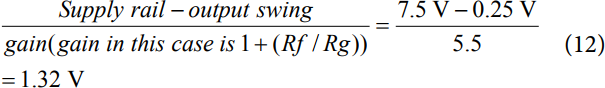

Bill:ADI公司提供了一系列增益為1/2�����、1或2的差動放大器��。比較AD8271 和 AD8278之后�����,我們選擇了AD8278�,因為它的功耗更低����。我們將其增益配置為1/2,這使得我們能夠提高輸入緩沖器的增益,降低電源軌(最終確定為±7.5V DC)�����,并且滿足噪聲和直流失調(diào)容差要求����。我們相信,將盡可能多的增益移動到輸入緩沖器可以使噪聲最低����。(關(guān)于新設(shè)計的噪聲、CMRR和失調(diào)容差�,請參見等式5至11)

Matt: AD8278 的增益可以配置為1/2或2。我們通常認為����,將放大器置于最高增益級可以獲得最佳的噪聲性能。然而��,由于AD8278是該設(shè)計的第二級����,因此將放大器置于較低增益級實際上有助于提高設(shè)計的噪聲性能。這樣����,Bill就可以在第一級中應(yīng)用更多增益�����。低噪聲設(shè)計的一個重要法則是讓第一級具有盡可能多的增益��,本設(shè)計當(dāng)然也不例外�����。

將更多增益放在第一級也有助于提高儀表放大器的CMRR性能��。我們可以根據(jù)先前關(guān)于電阻容差與CMRR關(guān)系的討論進行計算�����,將差動放大器的增益從1/2變?yōu)?時���,CMRR將提高6 dB,這與AD8278 數(shù)據(jù)手冊也是一致的�����。然而��,如果相反��,我們在第一級另外提供4倍的增益���,那么差分增益將提高4倍�,但共模增益保持不變��。換言之���,通過第一級放大����,我們可以獲得12 dB的額外CMRR�����,而將增益應(yīng)用于差動放大器時�,只能獲得6 dB的提高。注意����,這一技巧僅適用于第一級中的運算放大器具有良好CMRR的情況,因此��,使用高質(zhì)量運算放大器相當(dāng)重要。

相對于我們的集成儀表放大器����,使用G = 1/2的差動放大器級是Bill優(yōu)化分立設(shè)計的方法之一。通常����,對于我們的集成儀表放大器,我們必須將差動放大器的增益設(shè)置為G = 1或更高���,因為較低的差動放大器增益會限制儀表放大器處理寬共模電壓擺幅的能力�。

Bill:經(jīng)過大量搜索后����,我們選擇AD8622作為輸入緩沖運算放大器。該運放具有我們需要的全部特性:小封裝尺寸�、低功耗、低輸入偏置電流���、低0.1–10 Hz噪聲和寬電源軌����。還有一個我們認為重要的特性是單位增益穩(wěn)定性����。雖然我們的緩沖器以10倍增益工作�,但在儀表放大器配置中��,共模信號看到的增益是1�,因此可能會引發(fā)穩(wěn)定性問題(參見參考文獻3)�����。

Harry:對于前端運算放大器����,存在數(shù)十種甚至數(shù)百種選擇,因此�����,獲得確切的失調(diào)電壓��、偏置電流�����、電源電流等有助于優(yōu)化設(shè)計���。當(dāng)我們設(shè)計一個儀表放大器時�����,必須就一些因素進行大致的權(quán)衡�����,為了獲得最后10%的性能��,這種努力是值得的�。AD8622 是我們精密放大器產(chǎn)品線中的新成員,提供真正出色的特性組合����,包括電壓噪聲、低1/f轉(zhuǎn)折頻率���、電源電流��、增益頻寬����、失調(diào)電壓、失調(diào)電壓漂移等�。

我想贊揚Bill劃分系統(tǒng)的方式。有時候�����,我們看到一個四通道放大器的三部分被用于構(gòu)建儀表放大器���,這是很容易掉入的陷阱��。依據(jù)Vos、TCVos�、增益、帶寬�����、CMRR等來看�,第一級的需求與差動放大器級是完全不同的。此外���,為了獲得最后10%的性能���,第一級使用雙通道放大器,第二級使用單通道放大器非常有意義。為了在運算放大器中獲得低電壓噪聲��,需要消耗第二級當(dāng)中并不需要的大量電流��。假如第二級驅(qū)動一個重負載�,那么就需要比第一級運算放大器更多的驅(qū)動。四通道放大器的另一個缺點是:輸出運算放大器的熱量可能會反饋到第一級運算放大器����。詳細討論參見參考文獻4和5。

Bill:我們的第一選擇本來是使用集成儀表放大器���,藉以節(jié)省電路板空間����。然而��,使用精密差動放大器后�����,確實使我們可以對儀表放大器進行微調(diào)��,而不需要昂貴且占用電路板空間的電阻網(wǎng)絡(luò)�����。我們得以顯著降低功耗,同時仍然保持重要的性能特性�����,像是噪聲�����、CMRR以及直流輸入容差等��。

圖3. CareFusion儀表放大器簡圖

Harry:謝謝�,Bill�。Matt和我非常高興與您合作開發(fā)一款先進的設(shè)計。

附錄:BILL的計算公式

計算AD8221在0.1 Hz至100 Hz帶寬內(nèi)的期望峰峰值噪聲以揭示增益的影響(忽略電流噪聲����,因為電極阻抗很低)。

加上1/f噪聲(使用增益= 10��,來自數(shù)據(jù)手冊):

計算AD8221BR 的期望最小CMRR以揭示增益引起的提高��。

(使用增益= 1�,來自數(shù)據(jù)手冊):

計算AD8221的電極失調(diào)容差:

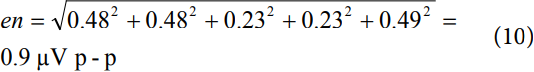

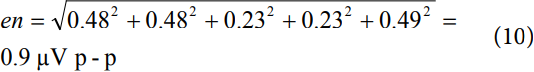

針對新儀表放大器設(shè)計(忽略電流噪聲,因為阻抗很低)。

AD8622 緩沖器的噪聲:

加上 1/f 噪聲:

½ Rg與Rf并聯(lián)的噪聲:

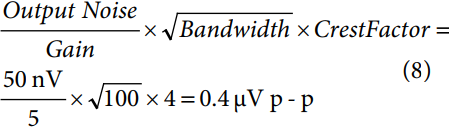

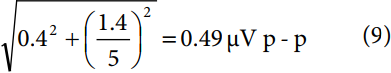

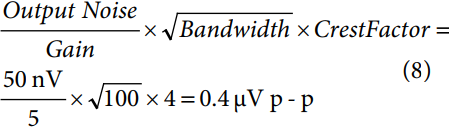

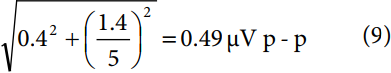

來自AD8278的噪聲:

加上1/f噪聲:

所有噪聲源求和:

新儀表放大器設(shè)計的期望最小CMRR:

新設(shè)計的電極失調(diào)容差(直流源連接到一個輸入端���,另一個輸入端接地)�����。

參考電路

1. Pallás-Areny, Ramón and Webster, John G. “Common Mode Rejection Ratio in Differential Amplifiers” IEEE Transactions On Instrumentation and Measurement, Vol. 40, No 4, August 1991, pp 669-676.

2. Analog Devices, Linear Circuit Design Handbook. p 2.9.

3. D. Rod White “Phase Compensation of the Three Op Amp Instrumentation Amplifier” IEEE Transactions on Instrumentation and Measurement, Vol. IM-36, September 1987.

4. Holt, Harry “Op Amps: To Dual or Not to Dual (Part 1)” EETimes.

5. Holt, Harry “Op Amps: To Dual or Not to Dual (Part 2)” EETimes.

推薦閱讀: