【導讀】對于以下的文章,我是很佩服的,我按照它們的思路把問題推演和考證了一下,參考了一些數(shù)據(jù),自己推導一下電容模型的阻抗曲線,試圖做的就是讓問題更明顯一些。打算把這個問題分成兩個部分,第一個就是原理上去驗證,第二個就是從實際的例子去推演。

看了很多關(guān)于旁路電容和去藕電容的文章,有代表性的如下:

1. 退耦電容的選擇和應用

2. 十說電容

3. 關(guān)于旁路電容和耦合電容

4. 關(guān)于旁路電容的深度對話

對于以上的文章,我是很佩服的,我按照它們的思路把問題推演和考證了一下,參考了一些數(shù)據(jù),自己推導一下電容模型的阻抗曲線,試圖做的就是讓問題更明顯一些。打算把這個問題分成兩個部分,第一個就是原理上去驗證,第二個就是從實際的例子去推演。

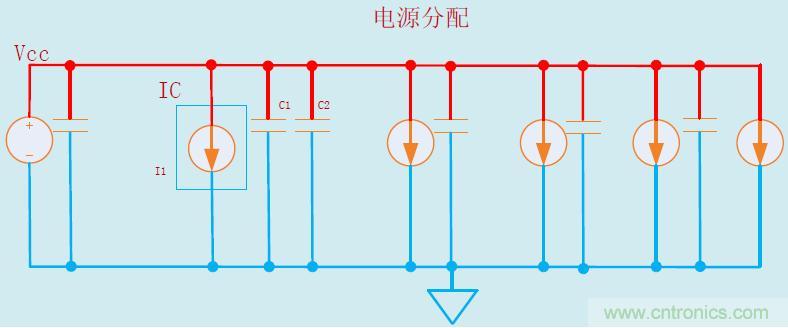

先看看此類電容的應用場合:

根據(jù)以上電路來說,由一個電源驅(qū)動多個負載,如果沒有加任何電容,每個負載的電流波動會直接影響某段導線上的電壓。

瞬間沖擊電流的產(chǎn)生原因

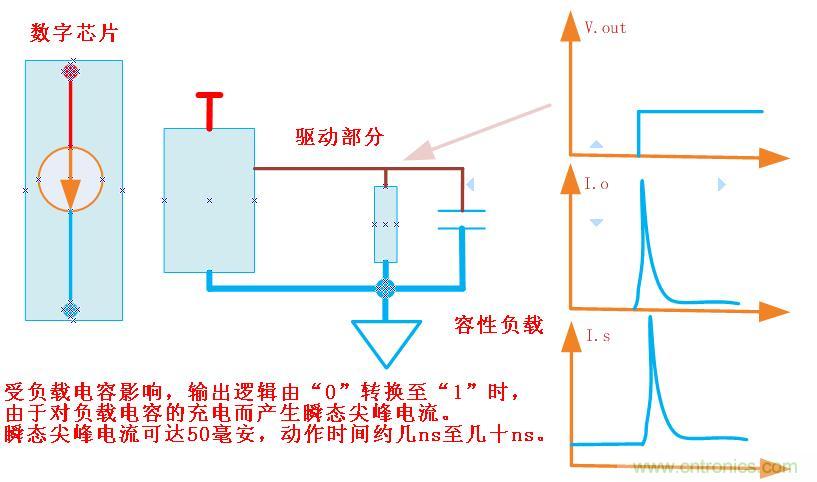

1.容性負載

來分析一下數(shù)字電路的電流波動,數(shù)字電路的負載并不是純阻性的,如果負載電容比較大,數(shù)字電路驅(qū)動部分要把負載電容充電、放電,才能完成信號的跳變,在信號上升沿比較陡峭的時候,電流比較大,對于數(shù)字芯片來說,新派驅(qū)動部分電流會從電源線上吸收很大的電流,由于線路存在著的電感,電阻(特別是芯片管腳上的電感,會產(chǎn)生反彈),這種電流相對于正常情況來說實際上就是一種噪聲,會影響前級的正常工作,下圖反應了工作情況

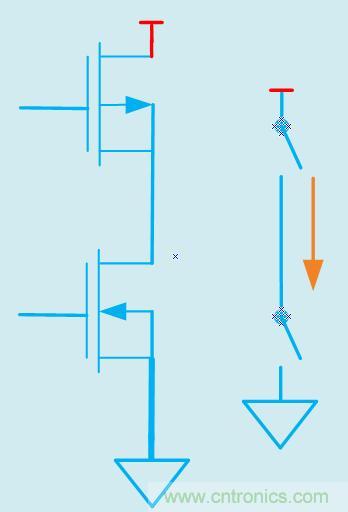

2.輸出級控制正負邏輯輸出的管子短時間同時導通,產(chǎn)生瞬態(tài)尖峰電流

PMOS和NMOS同時導通的時候出現(xiàn)的電流尖峰。

電壓塌陷噪聲

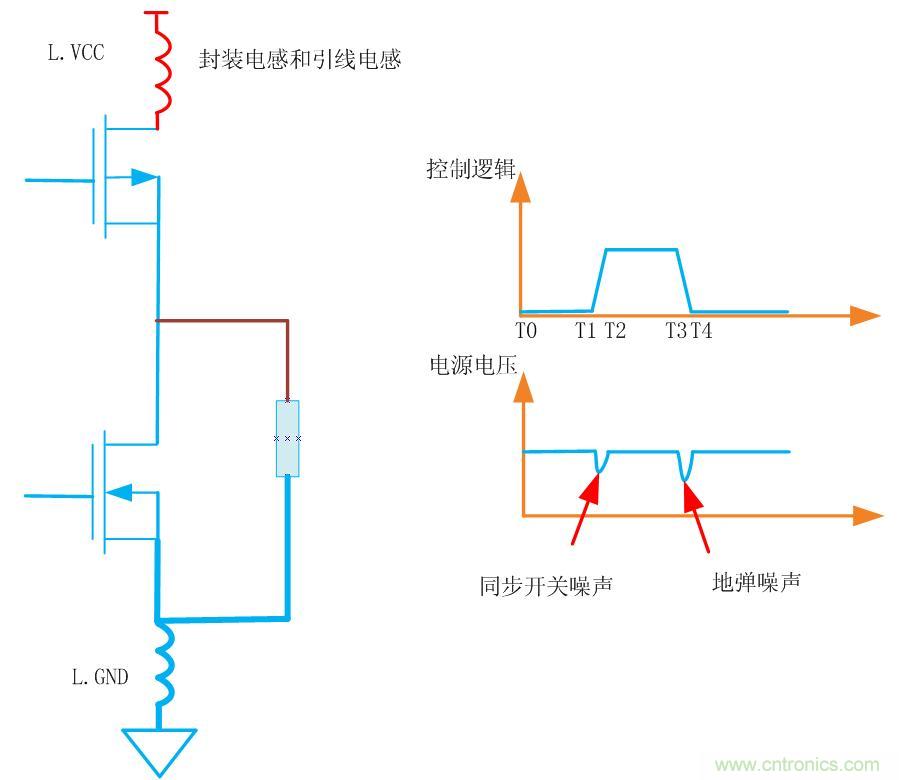

我們考慮數(shù)字電路內(nèi)部結(jié)構(gòu)一般由兩個Mos管組成,為了便于分析,我們假設(shè)初始時刻傳輸線上各點的電壓和電流均為零?,F(xiàn)在我們分析數(shù)字器件某時刻輸出從低電平轉(zhuǎn)變?yōu)楦唠娖?,這時候器件就需要從電源管腳吸收電流(上面一個分析的是容性負載,現(xiàn)在考慮的是阻性負載)。

從低到高(L=>H)

在時間點T1,高邊的PMOS管導通,電流從PCB板上流入芯片的VCC管腳,流經(jīng)封裝電感L.vcc,通過PMOS管和負載電阻最后通過返回路徑。電流在傳輸線網(wǎng)絡(luò)上持續(xù)一個完整的返回時間,在時間點T2結(jié)束。之后整個傳輸線處于電荷充滿狀態(tài),不需要額外流入電流來維持。

當電流瞬間涌過L.vcc時,將在芯片內(nèi)部電源和PCB板上產(chǎn)生一個電壓被拉低的擾動。該擾動在電源中被稱之為同步開關(guān)噪聲(SSN)或Delta I噪聲。

從高到低(L=>H)

在時間點T3,我們首先關(guān)閉PMOS管(不會導致脈沖噪聲,PMOS管一直處于導通狀態(tài)且沒有電流流過的)。同時我們打開NMOS管,這時傳輸線、地平面、L.gnd以及NMOS管形成一回路,有瞬間電流流過開關(guān)NMOS管,這樣芯片內(nèi)部至PCB地節(jié)點前處產(chǎn)生參考電平被抬高的擾動。該擾動在電源系統(tǒng)中被

稱之為地彈噪聲(Ground Bounce)。

實際電源系統(tǒng)中存在芯片引腳、PCB走線、電源層、底層等任何互連線都存在一定電感值,就整個電源分布系統(tǒng)來說來說,這就是所謂的電源電壓塌陷噪聲。

去藕電容和旁路電容

去藕電容就是起到一個小電池的作用,滿足電路中電流的變化,避免相互間的耦合干擾。關(guān)于這個的理解可以參考電源掉電,Bulk電容的計算,這是與之類似的。

旁路電容實際也是去藕合的,只是旁路電容一般是指高頻噪聲旁路,也就是給高頻的開關(guān)噪聲提高一條低阻抗泄防途徑。

所以一般的旁路電容要比去藕電容小很多,根據(jù)不同的負載設(shè)計情況,去藕電容可能區(qū)別很大,當旁路電容一般變化不大。關(guān)于有一種說法“旁路是把輸入信號中的干擾作為濾除對象,而去耦是把輸出信號的干擾作為濾除對象,防止干擾信號返回電源”,我個人不太同意,因為高頻信號干擾可以從輸入耦合也可以從輸出耦合,去藕的掉電可以是負載激增的輸出信號也可以是輸入信號源的突變,因此我個人覺得怎么區(qū)分有點糾結(jié)。

電容模型分析

如果電容是理想的電容,選用越大的電容當然越好了,因為越大電容越大,瞬時提供電量的能力越強,由此引起的電源軌道塌陷的值越低,電壓值越穩(wěn)定。但是,實際的電容并不是理想器件,因為材料、封裝等方面的影響,具備有電感、電阻等附加特性;尤其是在高頻環(huán)境中更表現(xiàn)的更像電感的電氣特性。

我們這里使用的電容一般是指多層陶瓷電容器(MLCC),其最大的特點還是由于使用多層介質(zhì)疊加的結(jié)構(gòu),高頻時電感非常低,具有非常低的等效串聯(lián)電阻,因此可以使用在高頻和甚高頻電路濾波無對手。

關(guān)于其特性分析和分類可以參考以前的文章:

Surface Mounted Capacitor(表貼電容) Ps:大部分是英文的,我有空把它翻譯整理過來。

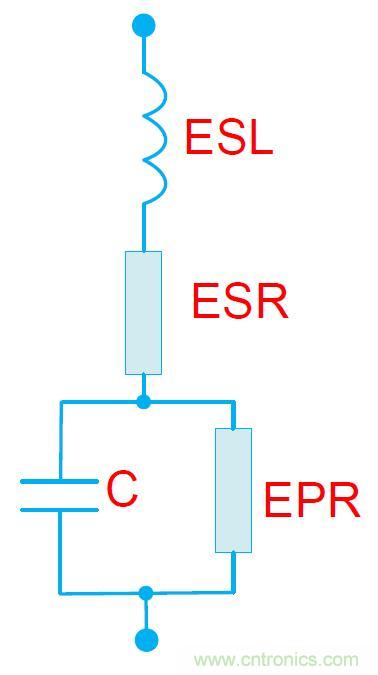

電容模型為

等效串聯(lián)電阻ESR:由電容器的引腳電阻與電容器兩個極板的等效電阻相串聯(lián)構(gòu)成的。當有大的交流電流通過電容器,ESR使電容器消耗能量(從而產(chǎn)生損耗),由此電容中常用用損耗因子表示該參數(shù)。

等效串聯(lián)電感ESL:由電容器的引腳電感與電容器兩個極板的等效電感串聯(lián)構(gòu)成的。

等效并聯(lián)電阻EPR:電容器泄漏電阻,在交流耦合應用、存儲應用(例如模擬積分器和采樣保持器)以及當電容器用于高阻抗電路時,Rp是一項重要參數(shù),理想

電容器中的電荷應該只隨外部電流變化。然而實際電容器中的EPR使電荷以RC時間常數(shù)決定的速度緩慢泄放。

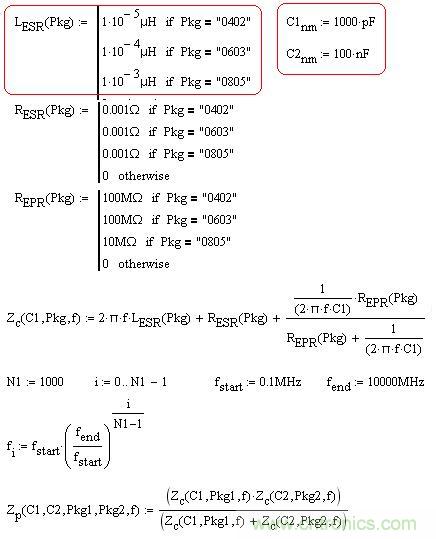

通過上述參數(shù),我們可以知道得到電容阻抗曲線

我找了Murata的電容做了對比

1000pF 0402

100nF 0603

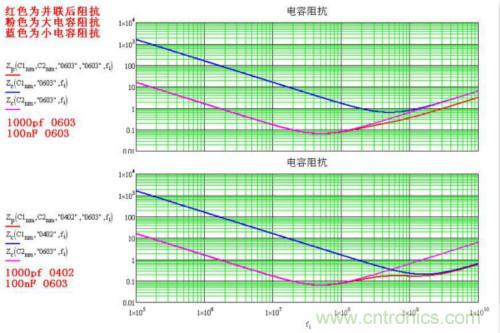

實際電容的阻抗是如圖所示的網(wǎng)絡(luò)的阻抗特性,在頻率較低的時候,呈現(xiàn)電容特性,即阻抗隨頻率的增加而降低,在某一點發(fā)生諧振,在這點電容的阻抗等于等效串聯(lián)電阻ESR。在諧振點以上,由于ESL的作用,電容阻抗隨著頻率的升高而增加,這是電容呈現(xiàn)電感的阻抗特性。在諧振點以上,由于電容的阻抗增加,因此對高頻噪聲的旁路作用減弱,甚至消失。電容的諧振頻率由ESL和C共同決定,電容值或電感值越大,則諧振頻率越低,也就是電容的高頻濾波效果越差。

ESL首先和電容的封裝直接相關(guān)的,封裝越大,ESL也越大。因此我們并聯(lián)三個電容以上對于濾除噪聲來說并不是很明顯的。這里有個問題,我們甚至希望可以得到0402的0.1uF的電容,但是這個是比較難得,因為封裝越小,操作電壓和容值都是有限制的,所以理智的做法就是用兩個電容。

通過曲線我們發(fā)現(xiàn),如果我們只是考慮1MHz以內(nèi)的噪聲的時候,在大多數(shù)情況下,旁路電容的規(guī)則可以簡化為只用0.1 μF電容旁路每一個芯片。不過我們要選擇0603的MLCC的電容,而且要注意電路布局。如果我們沿著電路板上的電流路線,可以發(fā)現(xiàn)電路板銅線上存在電感。在任何電流路徑上的電感與該路徑的閉環(huán)面積呈正比。因此,當你圍繞一個區(qū)域?qū)υ骷M行布局時,你需要把元器件緊湊地布局(為了使電感為最低)。

推薦閱讀: