【導讀】LIS公司生產(chǎn)各種FET(場效應(yīng)晶體管),特別值得一提的是他們有各種匹配雙器件產(chǎn)品,這種匹配器件封裝有其獨特優(yōu)勢。例如,如果您在設(shè)計一個雙聲道立體聲音頻產(chǎn)品,那么在同一個封裝中包含兩個或四個器件就可以使兩個音頻通道匹配更加緊密。

本文將探討如何在電壓控制電路中使用FET,分四部分連載,重點介紹幾種FET的使用方法:

● FET用作壓控電阻;

● FET用作電壓控制放大器和有源混頻器;

● FET用作壓控移相器來處理音樂;

● FET用作壓控帶通濾波器。

我們還將探討減少非線性或失真并自動偏置FET的方法。

FET電壓控制電阻

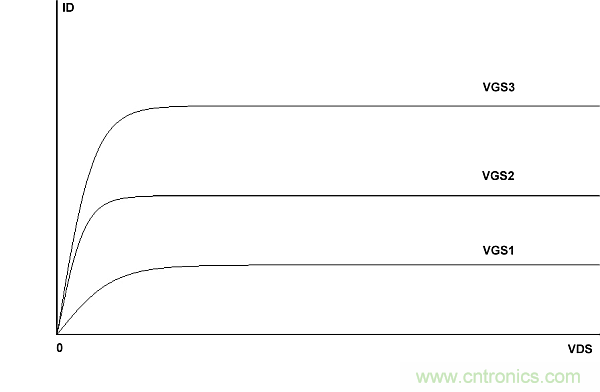

圖1顯示了一個N溝道FET的典型電流-電壓關(guān)系。

圖1:在不同的柵極至源極電壓VGS1/VGS2/VGS3下,典型的N溝道FET的I/V曲線。

FET一般有兩個區(qū)域:飽和區(qū)包括曲線的水平部分,這時FET用作電壓控制電流源;另一個區(qū)域包括傾斜的“彎曲部分”,稱為三極管或歐姆區(qū),此時FET用作壓控電阻。如果仔細觀察,我們會注意到圖1中的三極管區(qū)域顯示了非負的漏源電壓(VDS)。

注意:FET中的三極管或歐姆區(qū)有時稱為線性區(qū)。FET作為壓控電阻(VCR)工作在這個區(qū)域。理想情況下,VCR模式下的FET漏極和源極端子之間不存在DC電壓。

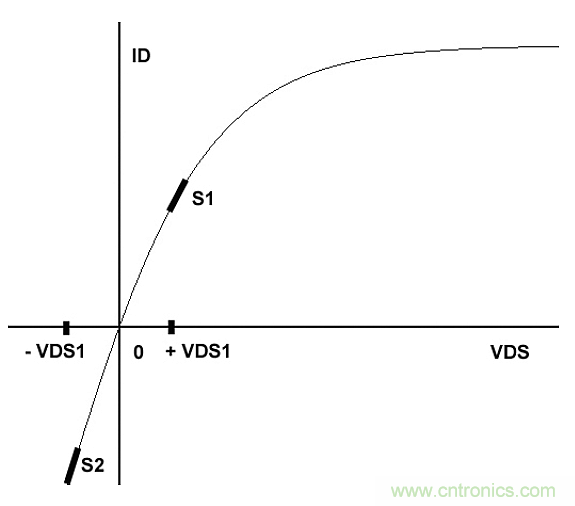

如果我們將針對特定柵-源電壓的VDS電壓范圍擴大,使其略包含負電壓,我們看到仍然存在電阻效應(yīng)(圖2)。

圖2:FET的三極管區(qū)擴展到負VDS電壓(- VDS1)仍然表現(xiàn)出電阻效應(yīng)。

斜率定義為:

斜率=ΔID / ΔVDS= gds = 漏極和源極間的電導

漏極和源極之間的電阻是電導的倒數(shù):

Rds = 1 / gds =ΔVDS/ΔID

我們看一下表示gds的兩個斜率S1和S2,會發(fā)現(xiàn)它們大致相同。但是如果仔細看,就會看出它們實際上有一點不同,S2的斜率比S1的斜率更陡一些。斜率越陡,電導率越高,電阻越低。例如,S2或-VDS1的高斜率區(qū)域附近的電阻低于S1或+ VDS1附近的電阻。電阻從+VDS1逐漸變化為-VDS1會導致失真,幸好失真可以減到很小。

例如,當漏極和源極兩端的小AC信號 < 500mV峰-峰值時,諧波失真可以保持在“合理的”低水平。如果漏極和源極之間的交流信號電壓在 - 250mV與+250mV之間,諧波失真將會“很小”,通常 < 3%。

這時你也許會問,有沒有FET只用作電壓控制電阻的?答案是肯定的(比如VCR11)。事實上,任何其它FET(比如JFET和MOSFET)都可用作電壓控制電阻。

基本的壓控電阻(VCR)電路

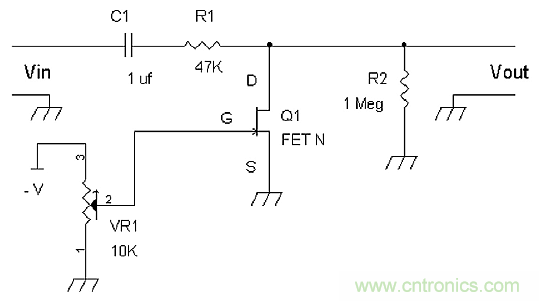

電壓控制電阻最簡單的一種用途是電子控制衰減器或“音量控制”。在圖3、圖4、圖5和圖6中,基本電路構(gòu)成一個分壓器。

在每一個電路中,F(xiàn)ET(Q1/Q2/Q3/Q4)的漏極和源極端子提供電壓控制電阻。當頻率大于20Hz時,C1的阻抗可被視為AC短路。

圖3:N溝道JFET衰減器電路。

在圖3中,將Q1的柵極電壓設(shè)置為0V或接地可實現(xiàn)最大衰減。R2將為Q1的漏極建立直流接地路徑。如果用導線代替C1,并且輸入信號源沒有明顯的DC偏置電壓(即 < 10mV DC),同時輸入信號源有一個直流接地路徑,它就可以被忽略。

當Q1柵極的負電壓導致Q1處于切斷狀態(tài)(即當柵極電壓→Vp時的夾斷電壓)時,發(fā)生最小衰減(即“貫通”)。

衰減器的傳遞函數(shù)是:

Vout/Vin = [Rds || R2] / [R1 + ( Rds || R2 )]

請注意,Rds是給定柵源電壓的漏源電阻。

如果Rds << R2,那么:

Vout/Vin = [ Rds] / [R1 + Rds ]

例如,如果Rds = 10k?,那么:

Vout/Vin = [10k?] / [47k? + 10k?] = 10k?/57k? = 10/57 = 0.1754

“耗盡型”N溝道JFET的漏極電流由Sedra和Smith的《微電子電路》給出:

其中,IDSS是Vgs = 0時的漏極電流。這一“最大”漏極電流在產(chǎn)品規(guī)格表中給出。

Vgs是N溝道器件的柵極到源極電壓,是非正電壓。

Vp 是夾斷電壓或切斷電壓。這是施加到柵極和源極以提供零漏極電流的電壓。產(chǎn)品規(guī)格表中給出了N溝道JFET的夾斷電壓Vp ≤ 0。而且,當Vgs = Vp時,漏極到源極電阻是無限的,因為沒有電流流入FET的漏極。

Vds是漏源電壓。這可以是漏極和源極之間的交流電壓,如圖3、圖4、圖5和圖6中的Vout。

對于歐姆、三極管或線性區(qū)的N溝道JFET,公式(1)至(5)僅在Vp≤Vgs≤ 0V時有效。

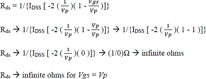

電導gds是通過求Id關(guān)于Vds的導數(shù)得到的。

電阻Rds是電導gds的倒數(shù):

公式(4)顯示Rds是基于固定參數(shù)IDSS、Vp和固定柵源電壓Vgs的非線性電阻,與漏極和源極兩端的(AC信號)電壓Vds有關(guān)。

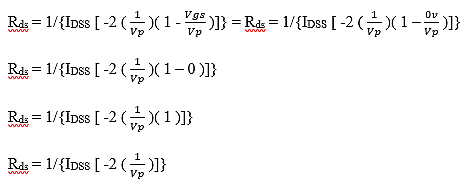

對漏極和源極兩端小信號初步近似,當Vds→0時:

公式(5)則是固定參數(shù)IDSS、Vp和固定柵源電壓Vgs的函數(shù)。電壓控制的“線性”電阻可由Vgs電壓設(shè)置。

例如,如果Vp = -1.5V, Vgs = -1.0V, 且IDSS = 0.005A = 5 mA,則:

根據(jù)公式(5),如果我們設(shè)定Vgs = Vp,那么漏源電阻將無窮大(即開路):

對于N溝道JFET,若想通過設(shè)置Vgs = 0V來得到最小電阻值,會發(fā)生什么呢?

若Vgs = 0V,公式便簡化為:

Rds = Vp/[-2IDSS]

例如,如果Vp = -1.5V,IDSS = 0.005A = 5mA, 且Vgs= 0V,那么:

Rds=-1.5v/[-2(0.005A)]=-1.5v/[-0.01A]=1.5v/0.01A=150?

Rds =150?

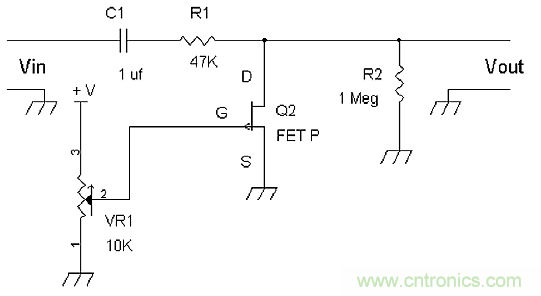

圖4示出了一個P溝道FET衰減器電路。它的工作方式與圖3相似,只是柵極的控制電壓為正值,切斷Q2獲得最小衰減。同樣,當柵極電壓為零或接地時,得到最大衰減。

圖4:P溝道JFET衰減器電路。

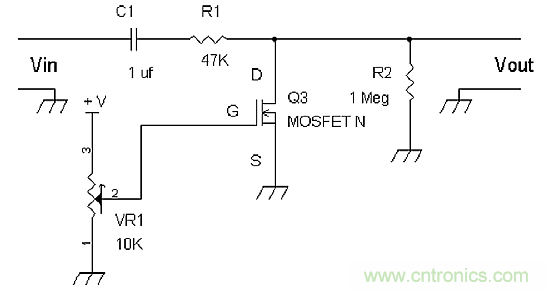

MOSFET用作電壓控制電阻

MOSFET也可被用作電壓控制電阻,如圖5所示。目前大多數(shù)MOSFET都是“增強型”,這意味著開通漏極電流以降低其Rds所需的柵極偏置電壓為正電壓。因此,如果柵極電壓為0V,則MOSFET關(guān)斷。

圖5:N溝道MOSFET衰減器電路。

采用N溝道增強型器件Q3,在0V電壓時,衰減器將輸入信號以最小衰減傳遞至Vout。如果將VR1設(shè)置為大于閾值電壓Vth的正電壓,那么Q3的漏源電阻將開始下降。請注意,對于N溝道MOSFET,閾值電壓Vth> 0V。

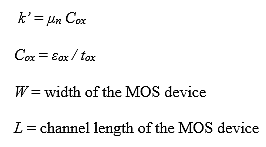

根據(jù)Gray和Meyer的《模擬集成電路的分析和設(shè)計》,N溝道MOSFET的漏極電流由公式(6)表征:

其中:

應(yīng)該注意的是,大多數(shù)分立MOSFET產(chǎn)品規(guī)格表不會列出k’ = μnCox,Cox = εox/ tox,W

和L,而只是給出典型的IV曲線和閾值電壓范圍圖。

N溝道JFET的公式(1)跟公式(6)非常相似。請注意,它們都包含“ - (Vds)(Vds)”項,這會導致非線性電阻。

重申一下,N溝道JFET的公式是:

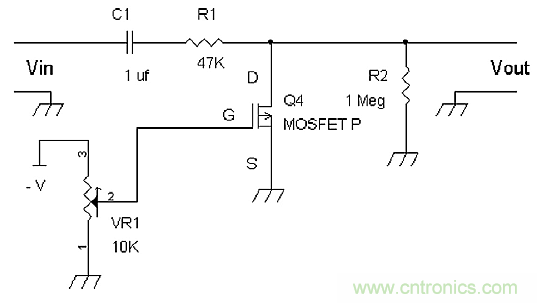

圖6示出了一個P溝道MOSFET電壓控制電阻電路。

圖6:P溝道MOSFET衰減器電路。

對于P溝道增強模式器件Q4,在零電壓時,衰減器將輸入信號以最小衰減傳遞至Vout。如果VR1設(shè)置為比閾值電壓Vth更負的電壓,那么Q4的漏源電阻將開始下降。注意,P溝道MOSFET的閾值電壓是負電壓(Vth< 0V)。

一般來說,圖5和圖6所示的衰減器電路允許小信號有適當?shù)闹C波失真,Vout的峰峰值

電壓 < 500mV。如果有失真,主要就是二次諧波失真。

平衡或推挽式VCR電路

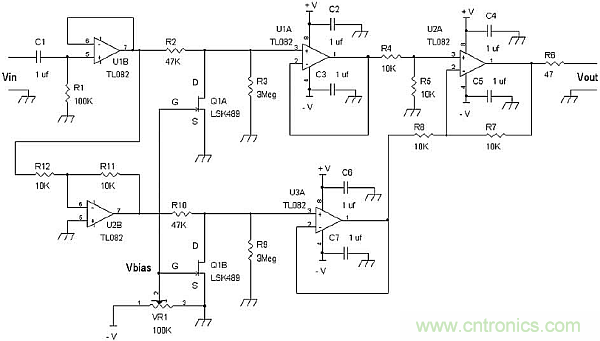

我們可以利用圖7所示的推挽電路進一步線性化或顯著減少二次失真。特別是雙配對FET(比如VCR11N、LSK489和LSK389等),可以消除偶次失真。

圖7:一個N溝道平衡配置示例,使用雙配對FET LSK489的Q1A和Q1B來降低失真。

推挽或平衡VCR衰減器電路可以消除或減少二次失真。在圖7中,U1B緩沖輸入信號Vin,并用Q1A(雙FET封裝的一半)驅(qū)動第一個電壓控制衰減器電路。Vbias是可變DC負電壓,可以改變Q1A的漏源電阻,通過串聯(lián)電阻R2提供電壓控制分壓電路。電壓跟隨放大器U1A緩沖Q1A漏極端子的電壓控制衰減信號。請注意,F(xiàn)ET輸入運算放大器(如TL082、TL062、LF353和AD712等)通常與高阻抗輸入電阻器(如R3和R9)一起使用。

運算放大器電路R12、R11和U2B構(gòu)成一個反相放大器,通過R10發(fā)送一個反相信號到第二個壓控衰減器電路。Q1B的柵極有相同的Vbias信號,允許Q1A和Q1B的漏極和源極具有匹配的衰減特性。電壓跟隨器U3A通過Q1B的漏極對電壓控制的衰減反相信號進行緩沖。由U2A、R4、R5、R7和R8組成的差分放大器從U1A和U3A中減掉輸出,通過Vout消除二次失真。

至此,同相的Q1A和Q1B的漏極都有二次失真,二次失真意味著一個x2函數(shù)。

應(yīng)注意的是,對負信號平方和對正信號平方得到的結(jié)果相同,即:

(- x)2 = (+ x)2

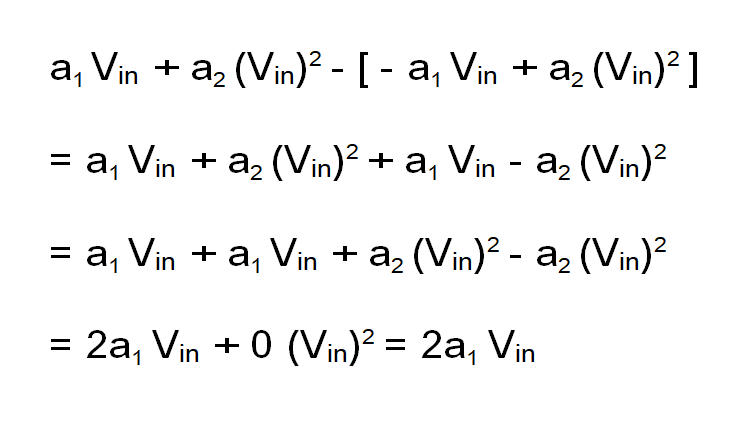

輸出信號可表征如下:

a1 = 線性分壓系數(shù)

a2 = 二次失真系數(shù)

對于非反相信號:

U1A pin 1 = a1 Vin + a2 (Vin)2

對于反相信號:

U3A pin 1 = a1 (- Vin) + a2 (- Vin)2

注意:(Vin)2 = (- Vin)2

所以,對反相信號,我們有:

U3A pin 1 = - a1 Vin + a2 (Vin)2

差分放大器U2A從U1A引腳1和U3A引腳1中減去同相和反相信號后,得到:

注意,a2 (Vin)2 - a2 (Vin)2 = 0

因此,差分放大器電路U2A引腳1的輸出 = 2a1 Vin,注意不存在二次失真項。這意味著我們得到一個放大了2倍的電壓控制衰減信號,并且沒有二次失真。

注意,圖7顯示了一個N溝道JFET的例子,但推挽或平衡操作的基本原理可以應(yīng)用于圖4、圖5和圖6中所示的P溝道JFET、N溝道MOSFET和P溝道MOSFET電壓控制衰減器電路。

或者,我們可以向基本的電壓控制電阻電路施加反饋來消除二次失真。當我們應(yīng)用這個反饋時,輸出信號會對稱地失真,這是由奇次失真引起的。

在第二部分中,我們將以示例詳細探討。

本文轉(zhuǎn)載自電子技術(shù)設(shè)計。

推薦閱讀: