【導(dǎo)讀】影響數(shù)據(jù)采集系統(tǒng)的主要因素包括:速度��、精度、功耗、封裝尺寸和元件成本�,其中哪些會(huì)成為關(guān)鍵因素取決于應(yīng)用場合�。本文介紹如何使用單個(gè)運(yùn)算放大器來驅(qū)動(dòng) 8 信道數(shù)據(jù)采集系統(tǒng)中的 ADC����,從而減少整個(gè)系統(tǒng)的成本和尺寸�����。

AD7329 八信道�、12 位加符號(hào)位、1 MSPS ADC 擁有真正的雙極輸入以及四個(gè)可獨(dú)立編程�����、可通過軟件選擇的輸入范圍:±4×VREF��、±2×VREF����、±VREF 和 0-to-4×VREF。它采用靈活的設(shè)計(jì)����,經(jīng)配置后可以滿足各種各樣的應(yīng)用需求。如圖 1 所示�����,AD7329 由 8 信道多路復(fù)用器以及隨后的采樣保持和逐次逼近 ADC、信道序列器�����、2.5 V 基準(zhǔn)電壓源和 SPI 兼容接口組成���。

圖 1. AD7329 功能框圖

模擬輸入信道通過多路復(fù)用器路由至 MUXOUT+ 和 MUXOUT– 引腳�。ADCIN+ 和 ADCIN– 引腳連接到采樣保持輸入開關(guān) (R1) 和采樣電容器 (C2)�����,如圖 2 所示���。需要注意的是���,輸入源必須提供所需的電流以驅(qū)動(dòng) ADC 輸入,并在 ADC 的 300 ns 采樣時(shí)間內(nèi)建立所需的精度��。當(dāng)采樣保持開關(guān)從“保持”變?yōu)?ldquo;采樣”時(shí)��,ADC 產(chǎn)生的瞬時(shí)反沖會(huì)影響輸入源�。在以最高采樣速率運(yùn)行的應(yīng)用中��,可能需要一個(gè)輸入緩沖放大器來驅(qū)動(dòng) ADC����,從而將輸入源與采樣保持開關(guān)隔離開來��。

圖 2. AD7329 模擬輸入結(jié)構(gòu)—單端模式

AD7329 的設(shè)計(jì)非常靈活���,允許在 MUXOUT+ 和 ADCIN+ 引腳之間放置一個(gè)運(yùn)算放大器。在圖 3 中���,超低噪聲���、超低失真的 AD797 運(yùn)算放大器將輸入源與 AD7329 的輸入結(jié)構(gòu)隔離開來,增加了輸入阻抗并減小了驅(qū)動(dòng) ADC 所需的電流���。此配置還允許單個(gè)運(yùn)算放大器以最大的采樣頻率驅(qū)動(dòng)八個(gè)模擬輸入信道��,因此減少了元件數(shù)量�����、板面積和系統(tǒng)成本����。

圖 3. MUXOUT 和 ADCIN 之間的緩沖器增加了輸入阻抗

通過配置運(yùn)算放大器以實(shí)現(xiàn)增益,如圖 4 所示��,使得 AD7329 能夠適應(yīng)毫伏范圍內(nèi)的信號(hào)���,同時(shí)保持出色的性能�����。微弱信號(hào)由 AD797 放大�����,并將經(jīng)過放大的信號(hào)應(yīng)用于 ADCIN+��。為了實(shí)現(xiàn)最佳性能��,可以選擇增益�,以便滿度輸入信號(hào)使用 ADC 的完整動(dòng)態(tài)范圍�。

圖 4. MUXOUT 和 ADCIN 之間的增益級(jí)有利于毫伏輸入

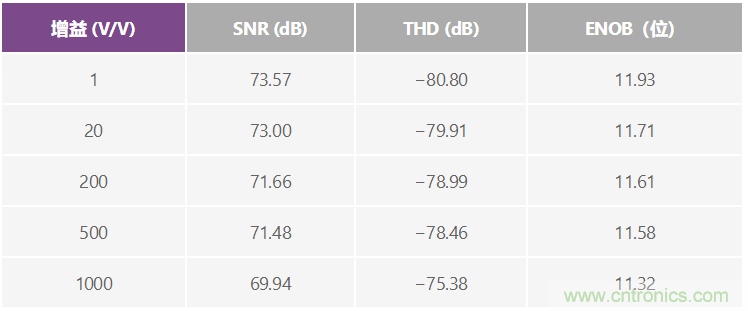

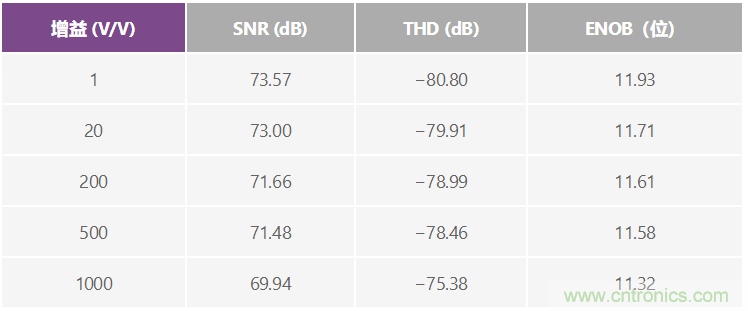

表 1 顯示了在 ±10 V 范圍內(nèi)獲得的性能和增益(采用 10 kHz 輸入和 1 MSPS 采樣速率)。值得注意的是�,在增益為 1000 時(shí),轉(zhuǎn)換器還可以實(shí)現(xiàn)大于 11 的有效位數(shù) (ENOB) ,從而實(shí)現(xiàn)與 21 位 ADC 相當(dāng)?shù)膭?dòng)態(tài)范圍���。此外�����,圖 3 中所示配置的所有優(yōu)勢也適用于此應(yīng)用場合���。

表 1. AC 性能和增益

某些應(yīng)用場合要求更改增益以適應(yīng)具有不同信號(hào)幅度的輸入信道��。在這些情況下����,可以采用 AD8250、AD8251��、AD8253 等可編程增益儀表放大器 (PGIA) 來取代運(yùn)算放大器�����。

參考電路

AN-0972�����,AD7329 如何幫助降低成本

推薦閱讀: