【導(dǎo)讀】本文將說明多路復(fù)用器輸入端的建立瞬變(由多路復(fù)用器輸出端的大尺度開關(guān)瞬變引起)導(dǎo)致需要較長(zhǎng)采集時(shí)間,使得多通道數(shù)據(jù)采集系統(tǒng)的整體吞吐量顯著降低。然后,本文將著重闡述使輸入建立時(shí)間最小化以及提高數(shù)據(jù)吞吐量和系統(tǒng)效率所需的設(shè)計(jì)權(quán)衡。

在多通道多路復(fù)用數(shù)據(jù)采集系統(tǒng)中,增加每個(gè)ADC的通道數(shù)量可改善系統(tǒng)的整體成本、面積和效率。現(xiàn)代逐次逼近寄存器模數(shù)轉(zhuǎn)換器(SAR ADC)具有高吞吐量和高能效,使得系統(tǒng)設(shè)計(jì)人員能夠?qū)崿F(xiàn)比以往更高的通道密度。

什么是多通道DAQ?如何衡量多通道DAQ的性能?

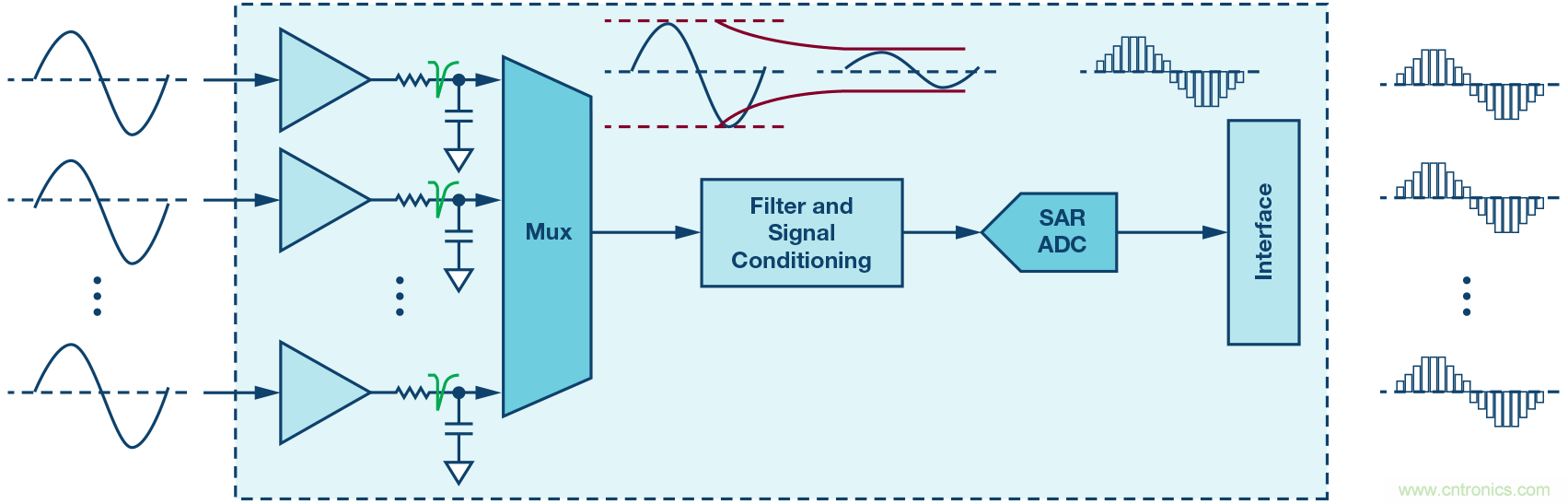

多通道數(shù)據(jù)采集(DAQ)系統(tǒng)是一個(gè)與多路輸入(通常是傳感器)接口的完整信號(hào)鏈子系統(tǒng),其主要功能是將輸入端的模擬信號(hào)轉(zhuǎn)換為處理單元可以理解的數(shù)字?jǐn)?shù)據(jù)。多通道DAQ系統(tǒng)的主要組成部分有模擬前端子系統(tǒng)(緩沖器、開關(guān)元件和信號(hào)調(diào)理模塊)、模數(shù)轉(zhuǎn)換器(ADC)及數(shù)字接口。對(duì)于高速精密轉(zhuǎn)換器,開關(guān)元件(通常是多路復(fù)用器)放置在ADC驅(qū)動(dòng)器和轉(zhuǎn)換器本身之前,以利用現(xiàn)代ADC的先進(jìn)性能。SAR ADC兼具高速度和高精度性能,是這些應(yīng)用最常用的ADC類型。

圖1. 典型的基于SAR ADC的多路復(fù)用數(shù)據(jù)采集系統(tǒng)框圖

用于工業(yè)和醫(yī)療應(yīng)用的高通道密度精密DAQ系統(tǒng)致力于將最多的通道壓縮到盡可能小的區(qū)域中。通過如下手段,多路復(fù)用DAQ系統(tǒng)一般可以實(shí)現(xiàn)高密度、高吞吐量和良好的能效:

1.使用高速精密SAR ADC

2.每個(gè)通道使用最低采樣速率

3.最大程度提高SAR ADC轉(zhuǎn)換器利用率,其中:

n為通道數(shù)。對(duì)每個(gè)轉(zhuǎn)換器而言,多通道數(shù)據(jù)采集系統(tǒng)的總吞吐量由下式給出:

這表明多通道DAQ系統(tǒng)的總吞吐量不僅取決于SAR ADC的速度和分辨率,還取決于此轉(zhuǎn)換器的利用情況。

延遲如何影響多通道DAQ系統(tǒng)的性能?

在有建立延遲的情況下,ADC的實(shí)際采樣和轉(zhuǎn)換周期會(huì)增加一項(xiàng)td,導(dǎo)致轉(zhuǎn)換器的實(shí)際最大采樣速率由下式給出:

其中TADC是ADC每個(gè)樣本的采樣周期(大多數(shù)ADC數(shù)據(jù)手冊(cè)通常都會(huì)提供,更常見的形式是SAR ADC采樣速率的倒數(shù),以"秒/樣本"為單位)。對(duì)于非零延遲td,多通道DAQ系統(tǒng)的實(shí)際最大采樣速率總是小于轉(zhuǎn)換器采樣速率,導(dǎo)致轉(zhuǎn)換器利用率始終低于100%。由此可以明白,采樣和轉(zhuǎn)換周期上增加的任何延遲都會(huì)降低轉(zhuǎn)換器的利用率。當(dāng)與前面關(guān)于總吞吐量的表達(dá)式聯(lián)系起來時(shí),多通道DAQ可以容納的最大通道數(shù)量就會(huì)減少??傊?,任何建立延遲都會(huì)降低多通道DAQ系統(tǒng)的通道密度和/或總吞吐量。

什么是多路復(fù)用器輸入切換毛刺和輸入建立時(shí)間?

當(dāng)多路復(fù)用器從一路輸入切換到另一路輸入時(shí),輸出仍然有前一輸入通道的記憶,其表現(xiàn)形式為多路復(fù)用器的輸出負(fù)載電容和寄生漏極電容中存儲(chǔ)的電荷。這對(duì)于高容性負(fù)載(例如ADC驅(qū)動(dòng)器和ADC本身)更為明顯,因?yàn)檫@些存儲(chǔ)的電荷沒有低阻抗路徑可以走。甚至可以說這些電荷被困住了,原因是輸出為容性,并且現(xiàn)代多路復(fù)用器采用先開后合(BBM)機(jī)制,故多路復(fù)用器具有高阻抗。只有切換到下一路輸入,這些電荷才能被釋放電。

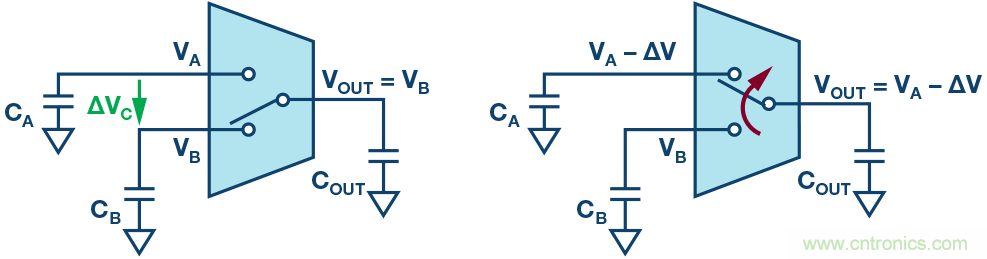

圖2. 切換前狀態(tài)(左),切換后,發(fā)生電荷共享,迅速引起電壓下降ΔV(右)

切換后,輸入電容CA將并聯(lián)到輸出電容COUT。然而,CA和COUT最初可能處于不同的電位,這將導(dǎo)致CA和COUT之間發(fā)生電荷共享。對(duì)于超高帶寬多路復(fù)用器,電荷共享幾乎立即發(fā)生,導(dǎo)致多路復(fù)用器輸入端出現(xiàn)高頻毛刺。此毛刺的幅度ΔV由下式給出:

其中ΔVC是切換之前電容電壓的差值。多路復(fù)用器輸入側(cè)發(fā)生的瞬態(tài)毛刺現(xiàn)象就是通常所說的反沖,其對(duì)于具有高容性負(fù)載(例如ADC、容性DAC和采樣電路等)的開關(guān)應(yīng)用更為普遍。這個(gè)話題在MT-088中已做簡(jiǎn)要說明。轉(zhuǎn)換器要產(chǎn)生有效數(shù)據(jù),毛刺必須穩(wěn)定在輸出的1 LSB以內(nèi),而輸入穩(wěn)定在1 LSB以內(nèi)(并保持在該范圍內(nèi)?。┧璧臅r(shí)間就是輸入建立時(shí)間(tS)。tS是前面描述的延遲td的組成部分,它對(duì)此項(xiàng)的貢獻(xiàn)可能是最大的。

當(dāng)ADC不像現(xiàn)在這樣快時(shí),這些毛刺及相應(yīng)的輸入建立時(shí)間微不足道,可以忽略不計(jì)。但是,隨著ADC速度的提高,轉(zhuǎn)換器采樣周期變得越來越短,接近輸入建立時(shí)間的量級(jí)。如前所述,當(dāng)ADC周期TADC等于輸入建立時(shí)間tS(事實(shí)上是td)時(shí),轉(zhuǎn)換器利用率大大降低至50%。這意味著我們只使用了轉(zhuǎn)換器的一半能力!需要重申輸入建立時(shí)間的重要性,它應(yīng)與精密轉(zhuǎn)換器的當(dāng)前技術(shù)同步發(fā)展,為提高多通道DAQ系統(tǒng)的性能鋪平道路。

如何最大程度縮短輸入建立時(shí)間?

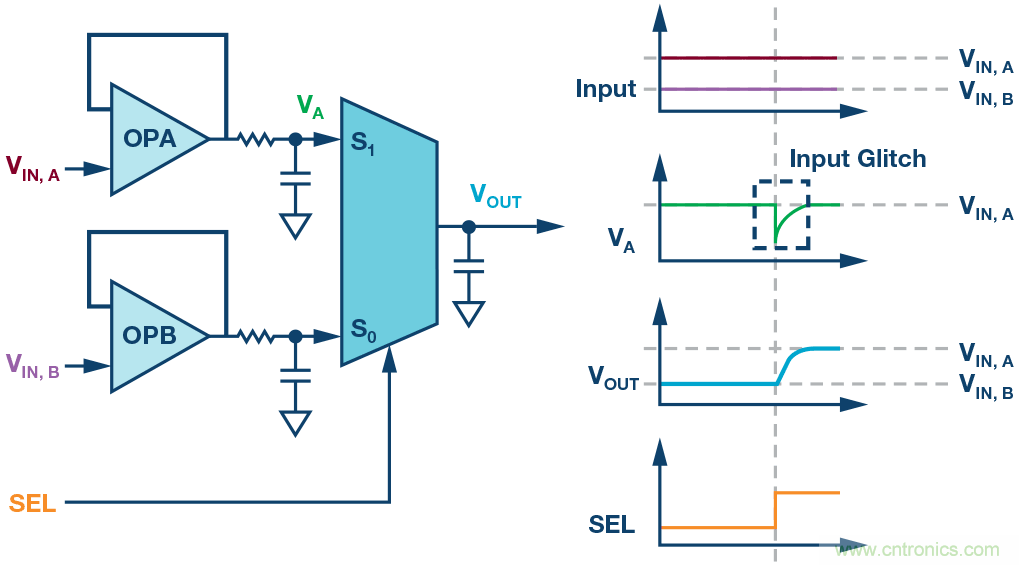

為使開關(guān)毛刺最小化,通常在緩沖放大器和多路復(fù)用器之間使用一個(gè)RC濾波器(參見 CN-0292),稱之為緩沖器網(wǎng)絡(luò)。圖3顯示了一個(gè)雙通道多路復(fù)用模擬前端子系統(tǒng)的信號(hào)鏈子系統(tǒng)及其相應(yīng)的開關(guān)時(shí)序圖。

圖3. 多通道DAQ系統(tǒng)的雙通道多路復(fù)用模擬前端子系統(tǒng)及相應(yīng)的時(shí)序圖

緩沖器RC作為主導(dǎo)極點(diǎn),假設(shè)多路復(fù)用器相對(duì)于放大器和緩沖器RC具有非常高的帶寬,那么輸入毛刺和建立瞬變可近似為具有一階(指數(shù))響應(yīng)。為了進(jìn)一步分析輸入毛刺,圖4詳細(xì)顯示了輸入毛刺瞬態(tài)響應(yīng)。

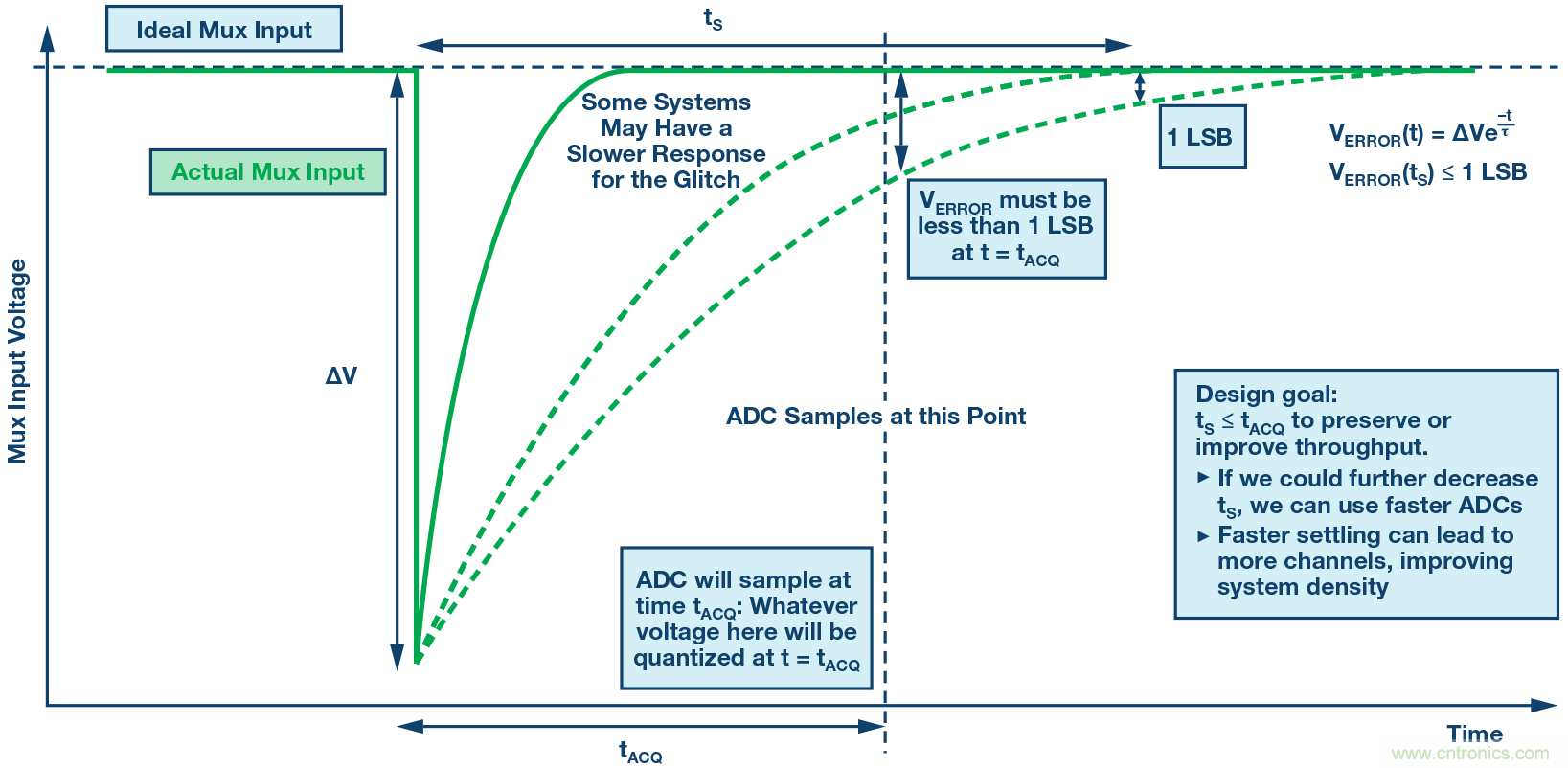

圖4. 分析切換期間的多路復(fù)用器輸入毛刺:時(shí)序定義和設(shè)計(jì)目標(biāo)

對(duì)于一階假設(shè),誤差VERROR的表達(dá)式是一個(gè)關(guān)于時(shí)間的遞減指數(shù)函數(shù)。VERROR的初始值(切換時(shí)的值)為毛刺幅度ΔV,其將以緩沖器RC值決定的速率衰減。VERROR穩(wěn)定在1 LSB以內(nèi)所需的時(shí)間被定義為輸入建立時(shí)間。

另一方面,轉(zhuǎn)換器以周期tACQ采樣(也稱為采集時(shí)間)。在tACQ過去后的ADC轉(zhuǎn)換階段,轉(zhuǎn)換器將量化任何可用的采樣數(shù)據(jù)。如果VERROR衰減速度過慢,導(dǎo)致其未穩(wěn)定在某一值(1 LSB到幾個(gè)LSB)以內(nèi),就會(huì)產(chǎn)生問題。這將導(dǎo)致當(dāng)前樣本被前一模擬輸入破壞,引起ADC通道之間的串?dāng)_??紤]到輸入建立時(shí)間,必須確保輸入建立時(shí)間小于轉(zhuǎn)換器采集時(shí)間,以使誤差最小。而且,進(jìn)一步減小tS還為使用更快轉(zhuǎn)換器以提高系統(tǒng)總吞吐量和密度提供了機(jī)會(huì)。

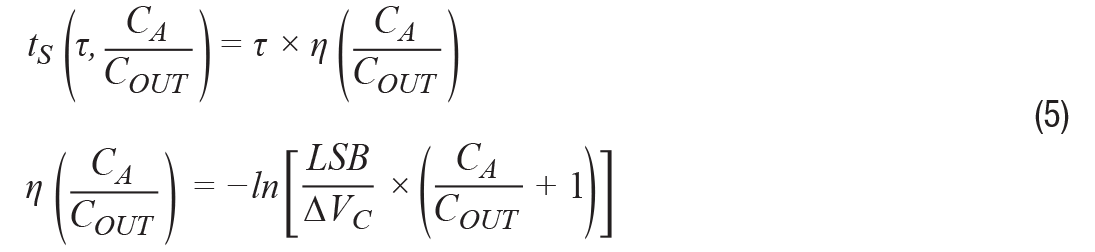

利用我們的數(shù)學(xué)技能,當(dāng)ΔVC為滿量程輸入范圍且VERROR達(dá)到至少1LSB(多路復(fù)用器輸出在目標(biāo)電平的1 LSB以內(nèi))時(shí),可以推出最差情況下的最快輸入建立時(shí)間表達(dá)式。多通道DAQ系統(tǒng)設(shè)計(jì)人員將擁有兩個(gè)設(shè)計(jì)抓手:緩沖器時(shí)間常數(shù)和CA/COUT比率,從而得出輸入建立時(shí)間的表達(dá)式:

這里可以看出,輸入建立時(shí)間是緩沖器時(shí)間常數(shù)τ和VERROR穩(wěn)定在1LSB以內(nèi)所需的時(shí)間常數(shù)數(shù)量η的線性函數(shù)。減少輸入建立時(shí)間的最直接方法是使用時(shí)間常數(shù)較小的緩沖器網(wǎng)絡(luò),這很有意義,因?yàn)檩^快的(高帶寬)緩沖器網(wǎng)絡(luò)會(huì)降低時(shí)間常數(shù)。然而,這種方法將帶來一組不同的涉及噪聲和負(fù)載的權(quán)衡。另一方面,η項(xiàng)最小化也可以達(dá)成類似的結(jié)果。

η是緩沖器電容(CA)與輸出電容(COUT)之比的函數(shù)。如果1 LSB等于滿量程輸入范圍除以2的N-1次方(N為位數(shù)),并且最差情況下ΔVC等于滿量程輸入范圍,則該表達(dá)式可以進(jìn)一步簡(jiǎn)化。

公式6可能不那么直觀,很難可視化,所以僅利用10位、14位、18位和20位分辨率的半對(duì)數(shù)圖來說明可能更好,如圖5所示。

圖5. 建立至1 LSB所需時(shí)間常數(shù)的圖形

可以看出,CA/COUT值越高,則建立時(shí)間越短;電容比非常高時(shí),建立時(shí)間甚至接近0。COUT實(shí)質(zhì)上是多路復(fù)用器的漏極電容和后續(xù)各級(jí)的輸入電容,因此只有CA保持比較靈活的自由度。對(duì)于10位分辨率,要使建立時(shí)間為0,CA須比COUT大至少1000倍;對(duì)于20位系統(tǒng),至少要比COUT大1,000,000倍!舉例來說,對(duì)于10位和20位系統(tǒng),為使建立時(shí)間為0,100 pF的典型負(fù)載分別需要100 nF和100μF的緩沖器電容。

總之,輸入建立時(shí)間最小化可以通過兩種方法實(shí)現(xiàn):

1.對(duì)緩沖器網(wǎng)絡(luò)使用高帶寬

2.相對(duì)于COUT,使用較高的CA值。

高帶寬和大緩沖器電容可最大限度地減少輸入建立時(shí)間,所以使用最高帶寬和最大電容就行了

非也!必須考慮RC負(fù)載效應(yīng)和放大器的驅(qū)動(dòng)能力!為了研究緩沖器網(wǎng)絡(luò)對(duì)緩沖放大器的負(fù)載影響,應(yīng)在頻域分析模擬前端子系統(tǒng)。

由于我們將輸入毛刺建立在一階響應(yīng)的思想上,所以緩沖器網(wǎng)絡(luò)極點(diǎn)應(yīng)該就是最主要的貢獻(xiàn)者。換句話說,緩沖器帶寬應(yīng)該小于緩沖放大器和多路復(fù)用器的帶寬,以避免多極點(diǎn)交互,確保一階近似成立。

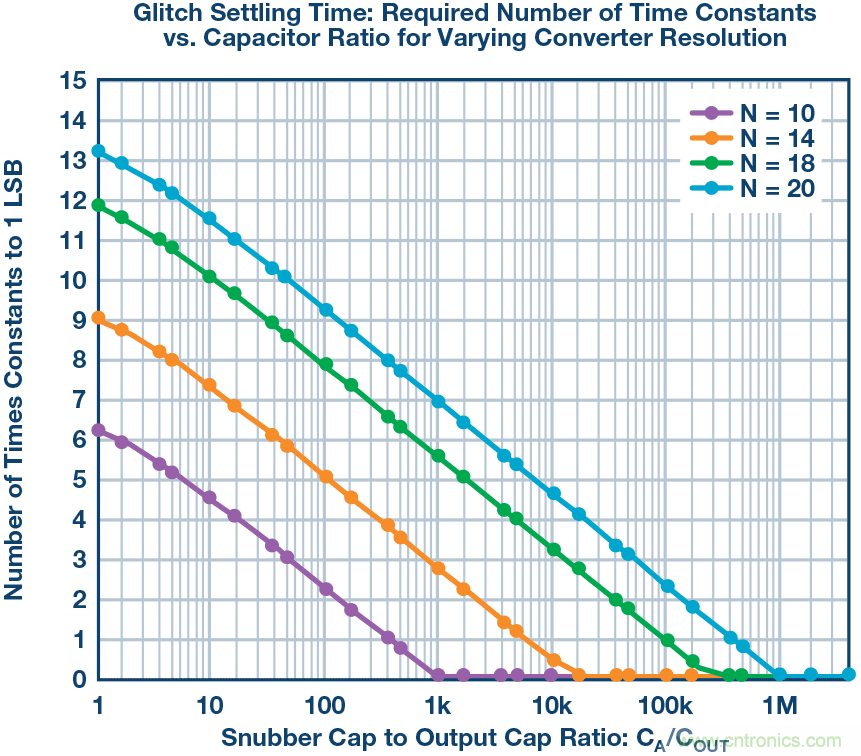

圖6. 緩沖和緩沖器等效電路(左)與放大器和緩沖器網(wǎng)絡(luò)的等效阻抗(右)

典型緩沖架構(gòu)由緩沖(G = 1)配置的精密放大器與緩沖器網(wǎng)絡(luò)級(jí)聯(lián)組成。在頻域中分析,此子系統(tǒng)的輸出取決于緩沖器輸入阻抗與緩沖器輸入阻抗和放大器閉環(huán)輸出阻抗之和的比率。檢查可知,為避免負(fù)載效應(yīng),緩沖器輸入阻抗應(yīng)該大于放大器閉環(huán)阻抗,如公式7所示。

也就是說,為避免緩沖器網(wǎng)絡(luò)成為緩沖放大器的負(fù)載,我們應(yīng)該:

1.增大緩沖器時(shí)間常數(shù) RACA,以有效降低帶寬

2.使用較小緩沖器電容 CA

3.選擇閉環(huán)輸出阻抗非常低的放大器

前兩個(gè)選項(xiàng)使我們清楚地了解到負(fù)載效應(yīng)和輸入建立時(shí)間之間的取舍。這限制了我們可以使用的緩沖器帶寬和電容的大小。第三個(gè)選項(xiàng)引入了一個(gè)性能參數(shù),選擇適當(dāng)?shù)木芊糯笃鲿r(shí)應(yīng)予以考慮。還應(yīng)考慮穩(wěn)定性和驅(qū)動(dòng)能力。

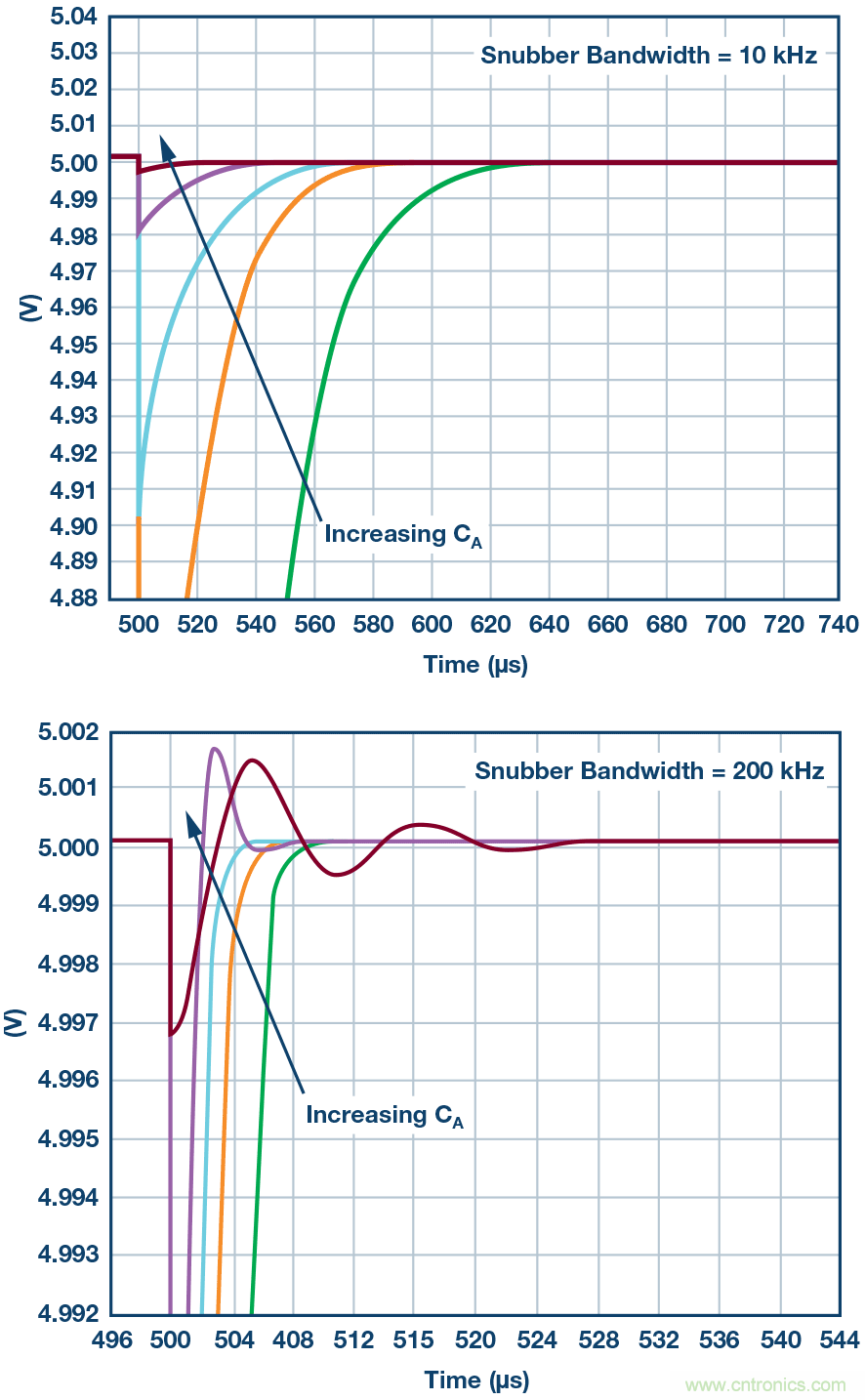

圖7顯示,對(duì)于具有足夠帶寬的精密放大器(例如-3 dB閉環(huán)帶寬約為970 kHz的ADA4096-2,結(jié)果與目前進(jìn)行的分析一致,但少數(shù)波形除外。對(duì)于10 kHz的緩沖器帶寬,最大CA產(chǎn)生最快的輸入建立時(shí)間。而對(duì)于200 kHz的緩沖器帶寬,增大CA仍然會(huì)加快建立時(shí)間,直至發(fā)生負(fù)載效應(yīng)。從結(jié)果中看到的欠阻尼響應(yīng)具有極小的毛刺幅度,但建立時(shí)間比較小CA所產(chǎn)生的響應(yīng)要長(zhǎng),盡管后者的毛刺幅度較高。這凸顯了仔細(xì)研究緩沖器如何加載放大器的重要性,在為系統(tǒng)選擇器件時(shí)務(wù)必考慮這一點(diǎn)。

圖7. 針對(duì)10 kHz(上方)和200 kHz(下方)緩沖器帶寬的多路復(fù)用器輸入,ADA4096-2放大器模型

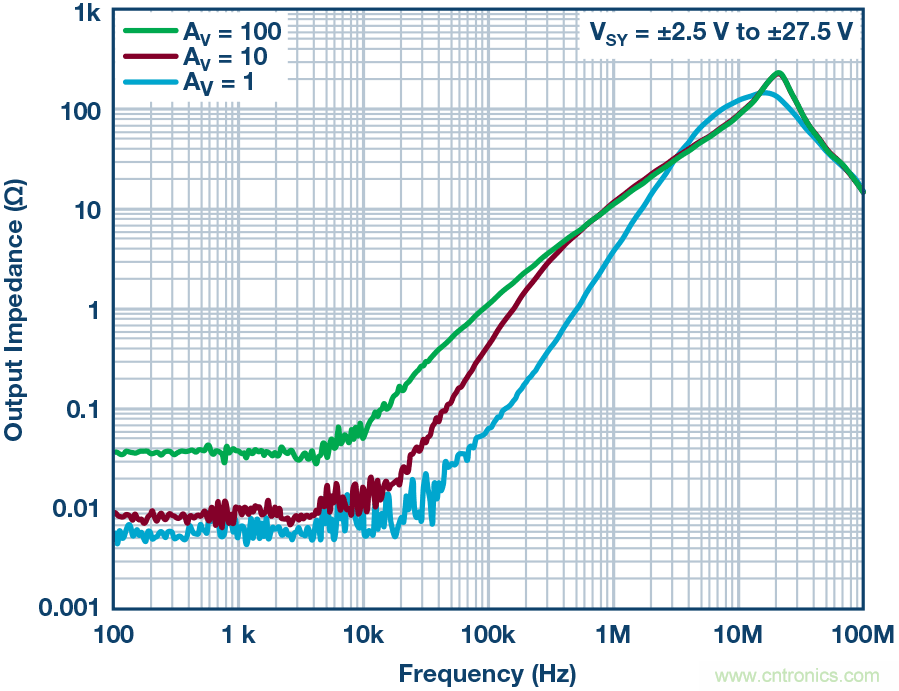

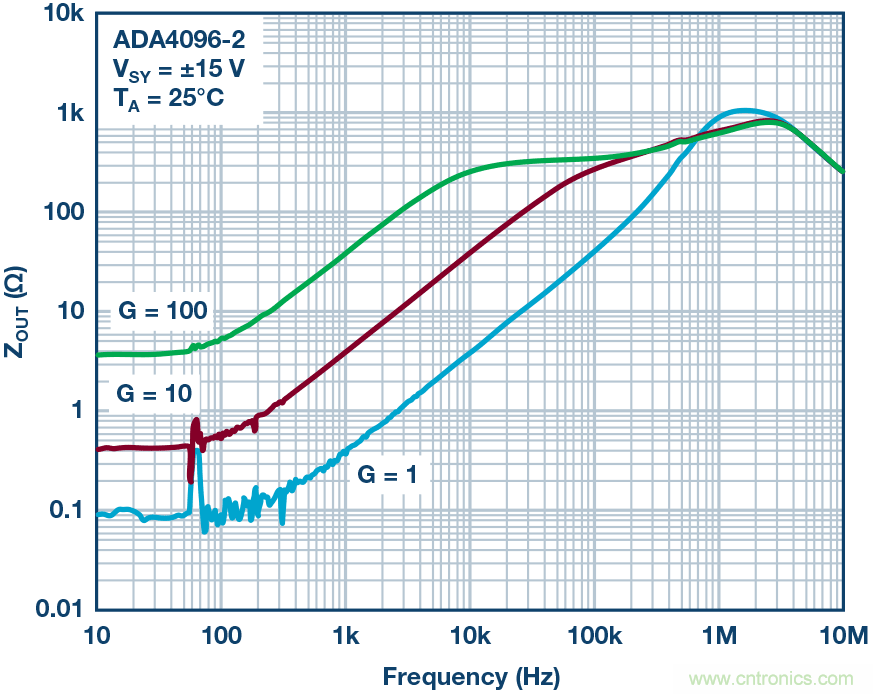

如前所述,需要注意的一個(gè)放大器參數(shù)是閉環(huán)輸出阻抗。運(yùn)算放大器的閉環(huán)阻抗通常與其開環(huán)增益AV成反比。我們還希望緩沖器網(wǎng)絡(luò)具有高帶寬以使建立時(shí)間最短,因此要求放大器的-3 dB帶寬甚至大于緩沖器帶寬。除了較低的噪聲、失調(diào)和失調(diào)漂移外,最適合用于多路復(fù)用DAQ系統(tǒng)以實(shí)現(xiàn)最小輸入建立時(shí)間的精密放大器還有兩個(gè)優(yōu)先特性:1)具有高帶寬,2)具有非常低的閉環(huán)阻抗。然而,這些優(yōu)勢(shì)的得來并非沒有代價(jià),而代價(jià)的表現(xiàn)形式就是功耗。例如,我們可以查看圖8所示的ADA4096-2和ADA4522-2的閉環(huán)阻抗。

圖8a. ADA4522-2數(shù)據(jù)手冊(cè)中的閉環(huán)阻抗圖

圖8b. ADA4096-2數(shù)據(jù)手冊(cè)中的閉環(huán)阻抗圖

考慮數(shù)據(jù)手冊(cè)中的閉環(huán)輸出阻抗圖,以及ADA4522-2的-3 dB閉環(huán)帶寬為6 MHz(標(biāo)稱值),顯然可知它是更適合該應(yīng)用的驅(qū)動(dòng)器。但當(dāng)功耗優(yōu)先時(shí),ADA4096-2的每個(gè)放大器的電源電流為60 μA(典型值),比ADA4522-2的每放大器830 μA(典型值)更具吸引力。盡管如此,這兩款精密放大器都可以使用,最終取決于應(yīng)用真正需要達(dá)成的目標(biāo)。

結(jié)語

我們?cè)趺醋鲎詈茫?/div>

為了最大限度地提高多通道DAQ系統(tǒng)的密度和吞吐量,輸入建立時(shí)間應(yīng)小于或等于ADC采集時(shí)間。任何額外的延遲都會(huì)降低多通道DAQ系統(tǒng)的性能。為使輸入建立時(shí)間最小化,需要提高緩沖器網(wǎng)絡(luò)的帶寬和電容,不過選擇元件值時(shí)必須小心,避免頻域中發(fā)生負(fù)載效應(yīng)。最后,選擇最合適的精密放大器需要權(quán)衡功耗、閉環(huán)輸出阻抗和-3 dB帶寬,按照應(yīng)用的真正需求確定其優(yōu)先地位。