【導讀】尤其在無線通信應用中,常常需要以非常短的時間切換PLL(鎖相環(huán))合成器的輸出頻率。在這類情況下,人們經常希望在相對較大的頻率跳變之后,以不到20µs時間實現穩(wěn)定的輸出頻率。本文將介紹,集成了VCO的超低噪聲和超低寄生0.37GHz至6.39GHz整數 N PLL合成器怎樣才能實現這樣的目標。

更具體地說,針對 20MHz 頻率階躍,我們選擇適當的 LTC6946 參數以使其輸出在盡可能短的時間里穩(wěn)定至最終頻率的 10kHz 之內。就本例而言,對于 LTC6946 我們可以采用一個 20MHz 的比較頻率(相位-頻率檢波器頻率,即fPFD)。舉個例子,這意味著如果基準輸入頻率 (fREF) 為 100MHz,則基準分頻器 (R) 必需設定為等于 5。

在 PLL 系統(tǒng)中實現一個穩(wěn)定環(huán)路的經驗法則是使環(huán)路帶寬 (LBW) 至少比fPFD小 10 倍。因此,而且為了優(yōu)化快速穩(wěn)定,在本例中我們可以設定 LBW = 2MHz。這與把 LBW 設定為等于頻率偏移的做法正相反,這里,PLL 的帶內相位噪聲與 VCO 的相位噪聲交叉以優(yōu)化整體相位噪聲性能。

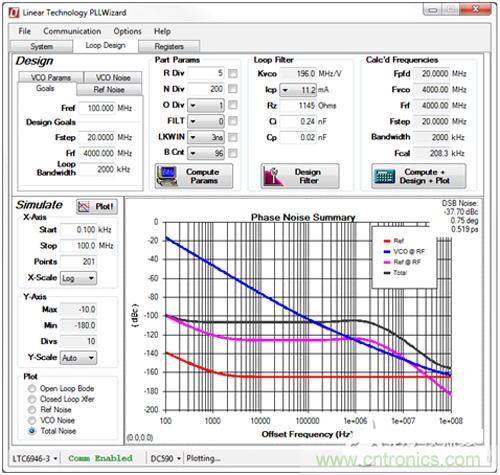

我們選擇由 LTC6946-3 產生 4GHz 輸出信號,并使用PLLWizard™軟件工具來確定,建立 LTC6946 周邊電路所需的濾波器組件值。PLLWizard 是一款免費工具,通過www.linear.com.cn/pllwizard提供,以輔助 LTC6946 的設計和仿真。

在 PLLWizard GUI 中輸入所希望的fPFD和 LBW 值并點擊幾下鼠標后,我們就有了環(huán)路濾波器組件值,我們可以將這些組件安裝到 LTC6946 電路中。圖 1 的屏幕截圖顯示,PLLWizard 工具是怎樣簡化 LTC6946 的設計過程的。為了核實我們的工作是否正確,我們在給定條件下仿真LTC6946 的預期相位噪聲。圖 1 包括 PLLWizard 的預測。

圖1:在 4GHz、20MHz fPFD和 2MHz LBW 時,PLLWizard 工具的設置以及對 LTC6946 相位噪聲的預測

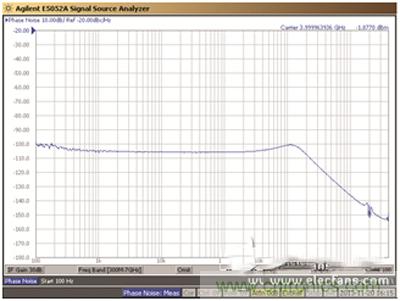

接下來,我們給電路加電,用 Keysight E5052A 信號源分析儀測量相位噪聲。圖 2 顯示,這一測量結果與上述仿真結果非常一致。

圖2:Keysight E5052A 信號源分析儀測得的 LTC6946 的輸出相位噪聲

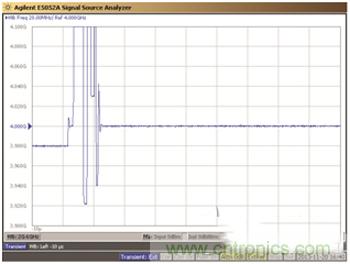

現在,我們來檢查一下,從 3.98GHz到 4.00GHz階躍 20MHz 之后,LTC6946 的輸出穩(wěn)定到與最終頻率值相差 10kHz 以內有多快。E5052A 可捕捉瞬態(tài)響應,如圖 3 所示。

圖3:在 20MHz 頻率跳變后,LTC6946 輸出的穩(wěn)定過程

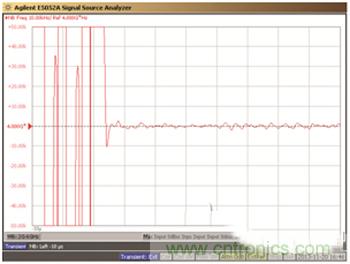

我們通過縮小上述測量中 E5052A 檢測器的帶寬來放大 y 軸,以更準確地確定穩(wěn)定時間。圖 4 說明了 LTC6946 的輸出是怎樣在不到15µs時間內穩(wěn)定到與最終頻率值相差不到 10kHz 的范圍內的。

圖4:在 20MHz 頻率階躍后,LTC6946 的輸出在不到15µs時間內穩(wěn)定

應該提到的是,集成了 VCO 的新式合成器 IC 用多個內部 VCO 子頻段來涵蓋其整個輸出頻率范圍。每次合成器 IC 的輸出頻率改變時,該 IC 都必須運行一次內部 VCO 校準例程,以確定正確的 VCO 子頻段。在 PLL 的 LBW 相對較大的情況下,如我們的例子中那樣,當切換頻率時,最終確定校準流程所需的時間會占穩(wěn)定時間的很大部分。由于 LTC6946-3 一般能夠在略多于10µs的時間內運行這種校準流程,所以我們能夠實現約為15µs的總穩(wěn)定時間。

圖 3 和圖 4 顯示,在 VCO 校準時,LTC6946 的輸出頻率跳來跳去。這里顯示這種行為是為了說明原因。在大多數實際情況下,人們不希望讓輸出頻率這樣跳來跳去。將 LTC6946 上的“MTCAL”寄存器設定為“1”(“1”是缺省值),就可通過在校準時抑制 RF 輸出來應對這種情況。建議“MTCAL”始終設定為“1”。

你可以遵照和修改本文提供的步驟,以確定適合您的應用參數。DC1705 (LTC6946 演示電路板) 為在各種濾波器和頻率配置情況下評估 PLL 的性能提供了一個全面的開發(fā)平臺。DC2026 Linduino® USB 控制器電路板在 PLL 演示電路板和使用 PLLWizard 工具的 PC 之間提供通信接口。

PLLWizard GUI 允許全面控制 DC1705。不過,為了在非常短的時間內設定 PLL IC以實現快速頻率切換,我們會編寫一些 Linduino 代碼,并以 DC2026 的最高 SPI 接口速度運行 DC2026。要通過 SPI 接口快速設定 PLL IC,使用 DC2026 和定制代碼是至關重要的,如果需要,還可以利用 Arduino IDE 提供一種代碼開發(fā)環(huán)境。

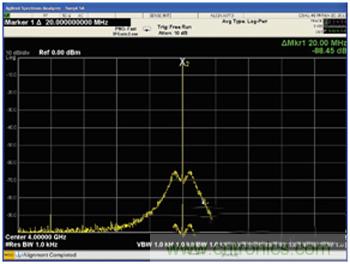

我們已經評估了我們的快速穩(wěn)定合成器的相位噪聲行為。然而,考慮到我們已經使環(huán)路帶寬相對較大,所以有人可能會問,寄生性能會受到怎樣的影響。有人可能會預期,使用典型的合成器 IC 時,寄生性能在這些條件下會受到損害。使用 LTC6946 時情況卻不是這樣的。在 2MHz 環(huán)路帶寬和 20MHz fPFD時,實現接近-90dBc 的基準雜散噪聲 (從 4GHz 載波偏移fPFD = 20MHz時不想要的信號) 是引人注目的,正如圖 5 顯示的 LTC6946 頻譜所確認的那樣。

圖5:LTC6946 的輸出頻譜,在 4GHz 輸出、環(huán)路帶寬為 2MHz 時展示了不同尋常的低雜散噪聲

LTC6946 以能夠產生低相位噪聲和低寄生輸出而聞名。我們在本文中展示了,使用 LTC6946,可以在不損害寄生性能的情況下,實現超快頻率切換。