【導(dǎo)讀】SI問題最常見的是反射,我們知道PCB傳輸線有“特征阻抗”屬性,當(dāng)互連鏈路中不同部分的“特征阻抗”不匹配時,就會出現(xiàn)反射現(xiàn)象。SI反射問題在信號波形上的表征就是:上沖/下沖/振鈴等。

1. SI問題的成因

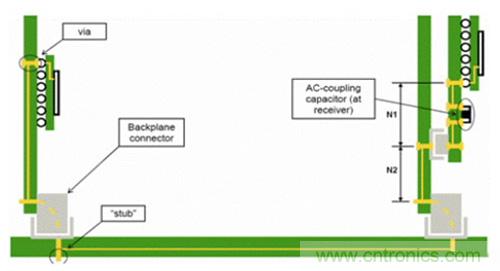

下圖所示是一個典型的高速信號互連鏈路,信號傳輸路徑包括:①發(fā)送端芯片(封裝與PCB過孔)②子卡PCB走線③子卡連接器④背板PCB走線⑤對側(cè)子卡連接器⑥對側(cè)子卡PCB走線⑦AC耦合電容⑧接收端芯片(封裝與PCB過孔)

圖1.典型高速信號互連鏈路

可以看出,實(shí)際電子產(chǎn)品的高速信號互連鏈路是比較復(fù)雜的,而且通常在不同部件連接點(diǎn)處是會產(chǎn)生阻抗失配的問題、從而造成信號的發(fā)射。

高速互連鏈路常見的阻抗不連續(xù)點(diǎn):

(1)芯片封裝:通常芯片封裝基板內(nèi)的PCB走線線寬會比普通PCB板細(xì)很多,阻抗控制不容易;

(2)PCB過孔:PCB過孔通常為容性效應(yīng),特征阻抗偏低,PCB設(shè)計(jì)最應(yīng)該關(guān)注與優(yōu)化;

(3)連接器:連接器內(nèi)銅互連鏈路的設(shè)計(jì)要同時受到機(jī)械可靠性與電氣性能的雙重影響,在兩者之間尋求平衡;

PCB走線反而一般情況下阻抗控制比其他互連部件更容易,重點(diǎn)關(guān)注層疊設(shè)計(jì)、板材選擇,但通常PCB加工板廠的阻抗控制公差為10%,要達(dá)到5~8%的阻抗公差控制往往需要花費(fèi)更高的加工成本。

2. 傳輸線反射基礎(chǔ)理論

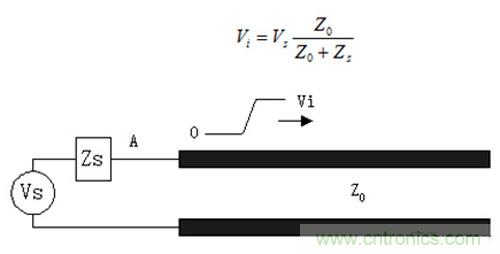

當(dāng)驅(qū)動器加信號到傳輸線時,信號的幅度依賴于驅(qū)動器的電壓與電阻和傳輸線阻抗。驅(qū)動器上的初始電壓通過自身電阻和傳輸線阻抗的分壓來控制。

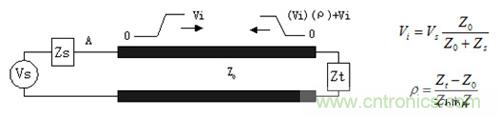

下圖描繪了加在長的傳輸線上的初始波形,初始的電壓Vi傳送到傳輸線上直到到達(dá)末端,Vi的幅度通過驅(qū)動器電阻和傳輸線阻抗的分壓來決定:

圖2.信號波形在長傳輸線的傳播

如果傳輸線的末端端接一個阻抗,而且這個阻抗與線的阻抗精確的匹配,那么幅度為Vi的信號將被端接到地,電壓Vi將仍保持在線上直到信號源轉(zhuǎn)換。在這種情況下Vi是dc穩(wěn)態(tài)值。否則,如果傳輸線的末端的阻抗不是線的特征阻抗,信號的一部分端接到地,信號的其余部分將被反射到傳輸線回到源。反射回的信號的量通過反射系數(shù)決定,反射系數(shù)由確定的點(diǎn)的反射電壓和輸入電壓的比決定。這個點(diǎn)定義為傳輸線上阻抗不連續(xù)。阻抗不連續(xù)可以是不同特征阻抗的傳輸線的一部分,也可以是端接電阻或者是到芯片緩沖器上的輸入阻抗。

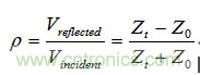

反射系數(shù)的計(jì)算:

其中Z0為傳輸線標(biāo)準(zhǔn)阻抗,Zt為傳輸線上某個不連續(xù)點(diǎn)的阻抗。

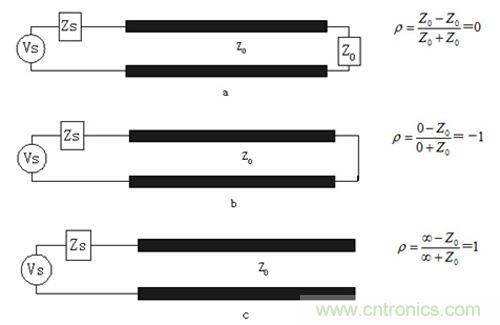

等式假設(shè)信號在特征阻抗為Z0的傳輸線上傳送遇到了不連續(xù)的阻抗Zt。注意如果Z0=Zt,反射系數(shù)為0,意味著沒有反射。Z0= Zt這種情況就稱為匹配的端接。

如下圖所示當(dāng)輸入波形遇到端接Zt,信號的一部分Viρ被反射回源端并且加在輸入波形上,整個輸入信號波形幅度為Viρ+Vi。反射的部分可能從源產(chǎn)生另一個反射,反射和逆反射一直持續(xù)直到傳輸線穩(wěn)定。

圖3.阻抗不匹配情況下的信號反射

當(dāng)傳輸線完全匹配、短路、開路時的反射系數(shù)如下圖所示:

圖4.(a)端接(b)短路(c)開路 三種情況下的反射系數(shù)

在實(shí)際應(yīng)用的互連鏈路中,理想的傳輸線是不存在的,也不可能存在完全匹配,因此信號的反射是必然存在的,設(shè)計(jì)的關(guān)鍵在于如何把互連鏈路中的各個部件阻抗差距盡量縮小,從而減小反射信號幅度、避免多級反射對信號質(zhì)量造成致命影響。