【導(dǎo)讀】電源完整性和信號(hào)完整性�����,在電路板設(shè)計(jì)中的重要程度不言而喻����,本文簡單介紹了電源完整性的仿真,在得到電源的阻抗曲線后���,如何設(shè)置去耦電容���,降低其在整個(gè)工作頻段中的阻抗��,從而達(dá)到降低EMI的目的�����。

首先,我們選擇一塊電路板����。版圖是公司的,所以這里涂黑了����,大概知道是塊板子就行了。

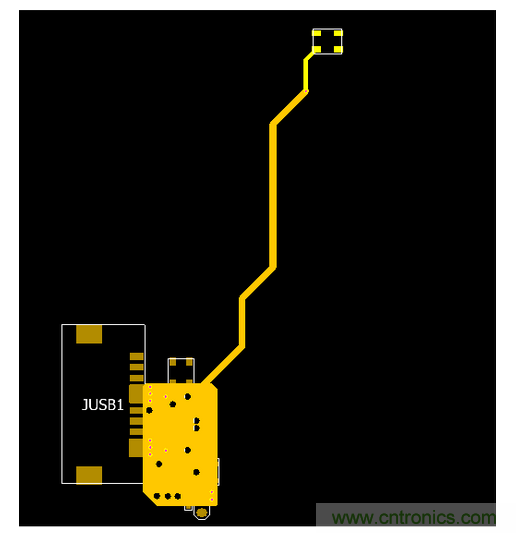

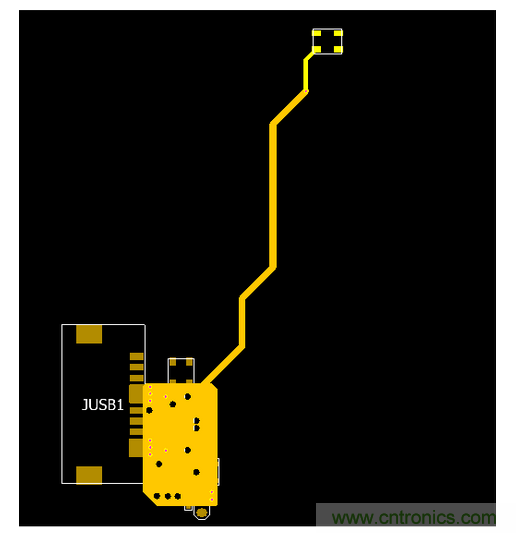

我們選擇一條5V的USB的走線�����,電源由右上角饋入��,在左下角經(jīng)過了4顆電容后到達(dá)USB接口�。

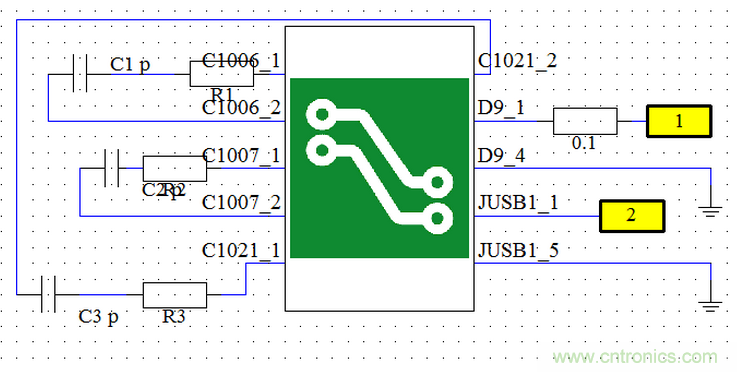

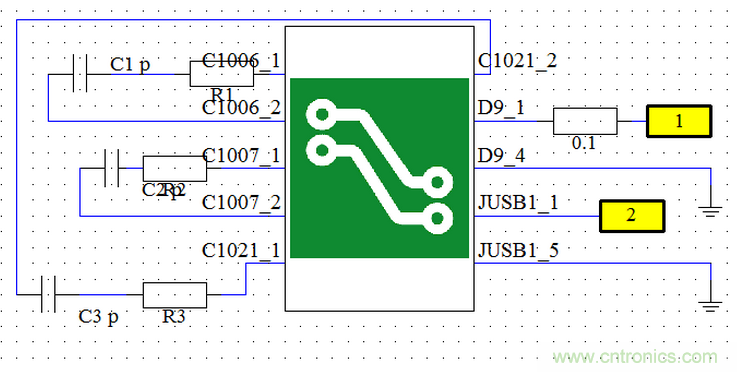

按照USB的標(biāo)準(zhǔn),目前USB3.0的傳輸速度受硬盤影響�����,最高不超過1Gbps�,因此我們關(guān)注的頻率在100kHz—2GHz,這里將其設(shè)置為仿真頻段,因?yàn)檫@根Net走線并不長�����,也沒有蛇形的彎曲部分���,所以預(yù)測其阻抗變化不是很大���,為了給老板省成本,這里直選了3顆電容�。首先得到仿真對(duì)象的 spice模型。

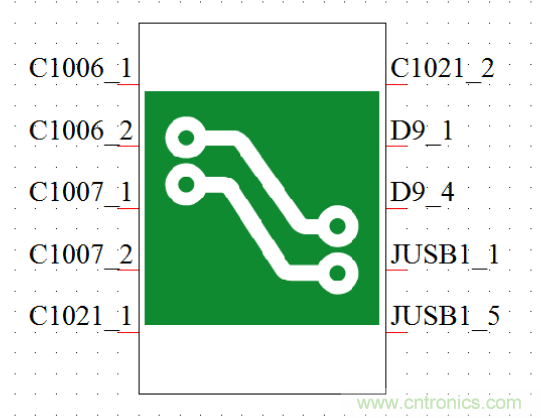

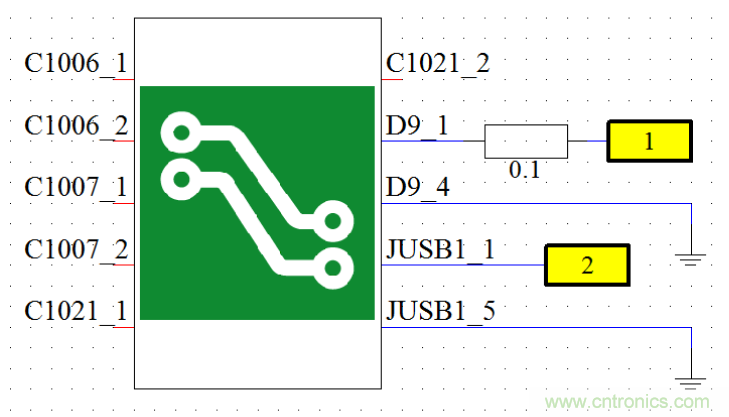

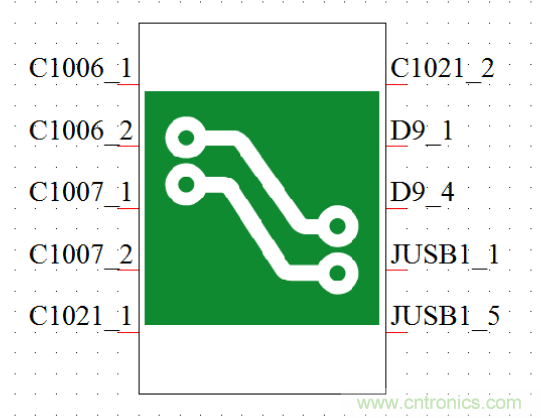

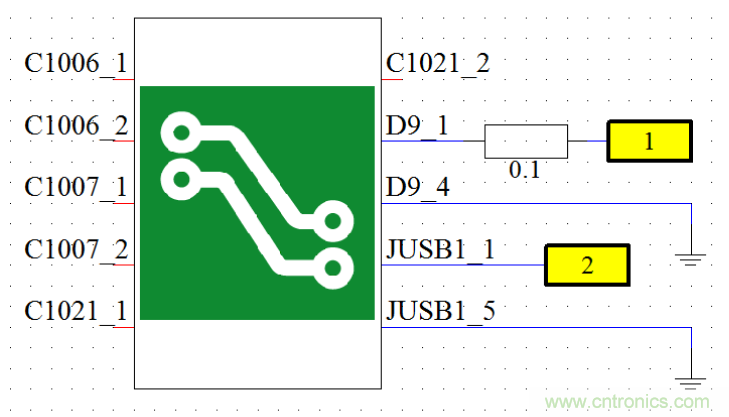

D9_1和JUSB1_1分別為饋入和饋出�����,相應(yīng)的D9_4和JUSB1_5為GND管腳���。設(shè)置電源內(nèi)阻為0.1Ω��,接下來進(jìn)行電路連接��,3顆電容的位置先空著�,查看這條Net的電源阻抗特性�����。

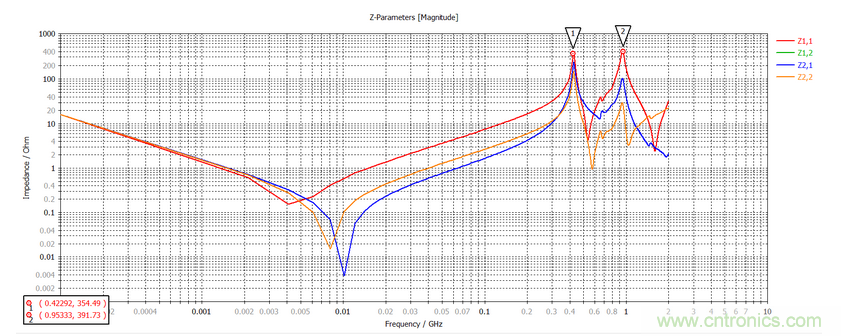

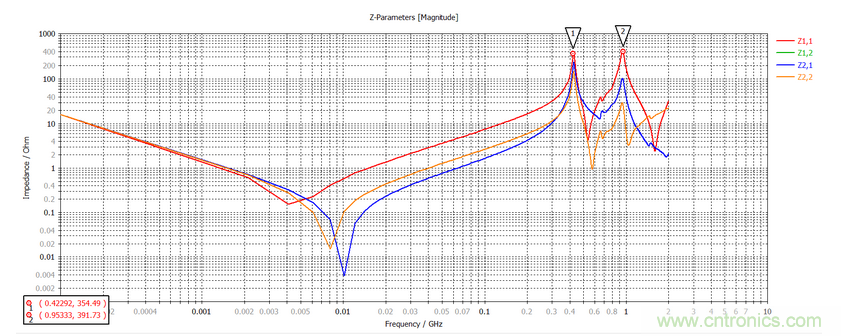

待仿真結(jié)束后���,得到這段電源走線的阻抗參數(shù)圖�,如下:

可以看到����,由于這根USB走線相對(duì)較短,且布線相對(duì)比較規(guī)范���,其阻抗在2GHz范圍內(nèi)變化并不是很大�����,最大391Ω�。電源信號(hào)在該頻段內(nèi)存在幾處明顯的諧振��,為了降低EMI���,需要加加去耦電容�。目標(biāo)希望其在整個(gè)頻段的阻抗降低到10Ω以下 ��。

接下來,將3顆電容連接起來��,分別為C1��、C2���、C3����,初始容值均設(shè)置為1000pf�,并串聯(lián)3顆電阻,分別為R1�、R2、R3����。優(yōu)化目標(biāo):100kHz—2GHz阻抗小于10Ω。

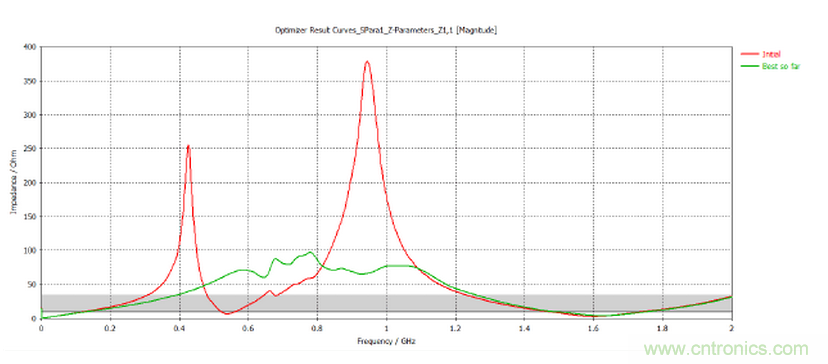

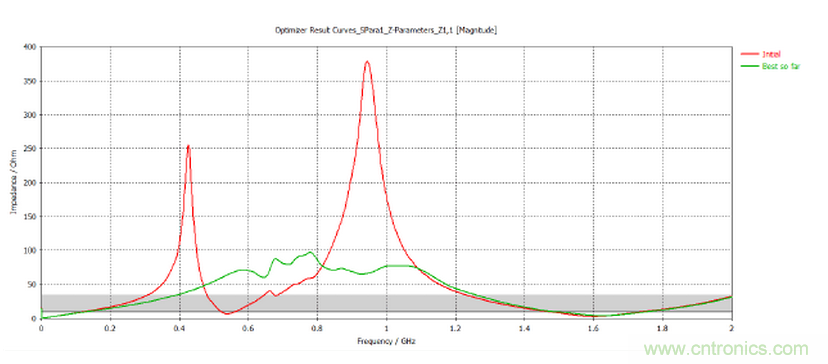

優(yōu)化后得到的結(jié)果:

C1 = 3111.65

C2 = 3122.21

C3 = 3111.49

R1 = 7.14841

R2 = 16.6401

R3 = 40.4783

上圖為1號(hào)端口的Z1_1曲線�����,綠色曲線為優(yōu)化后的結(jié)果���,紅色為初始結(jié)果��。用了3顆電容感覺還沒達(dá)到預(yù)定目標(biāo)���,但是從波形的平整度來看�����,確實(shí)要比開始好很多。

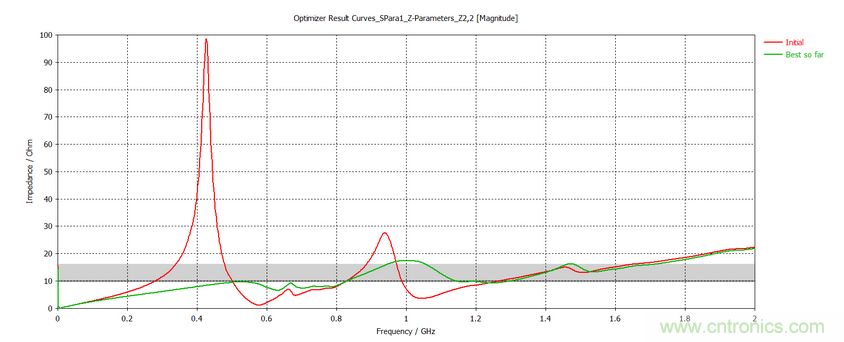

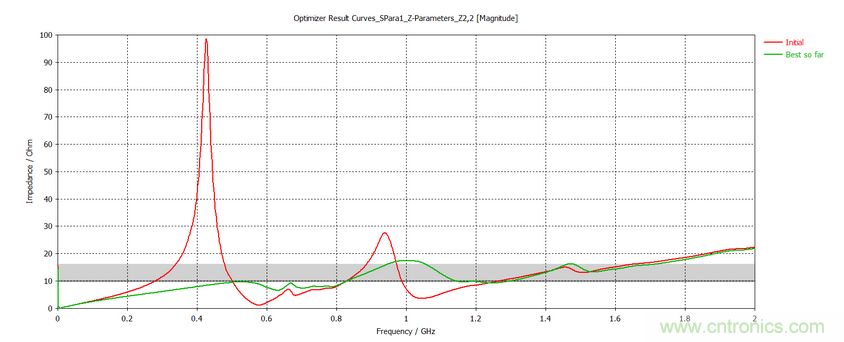

上圖為2號(hào)端口的Z2_2曲線�,綠色為優(yōu)化后的結(jié)果,基本上滿足要求了�,并且波形的平整度很不錯(cuò)。

總結(jié)��,layout板圖在初始的設(shè)計(jì)過程就應(yīng)該將電源完整性��、信號(hào)完整性以及EMC問題考慮進(jìn)去��,這樣會(huì)省去后續(xù)的大量的測試����、整改及修改板圖和工藝的時(shí)間及成本。

推薦閱讀: