【導(dǎo)讀】Σ-Δ型ADC是當(dāng)今信號采集和處理系統(tǒng)設(shè)計(jì)人員的工具箱中必不可少的基本器件。本文的目的是讓讀者對Σ-Δ型號ADC拓?fù)浣Y(jié)構(gòu)背后的根本原理有一個基本了解。本文探討了與ADC子系統(tǒng)設(shè)計(jì)相關(guān)的噪聲、帶寬、建立時間和所有其他關(guān)鍵參數(shù)之間的權(quán)衡分析示例,以便為精密數(shù)據(jù)采集電路設(shè)計(jì)人員提供背景信息。

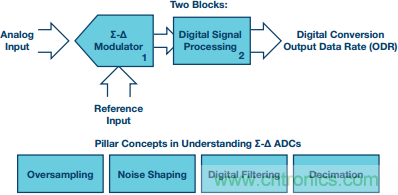

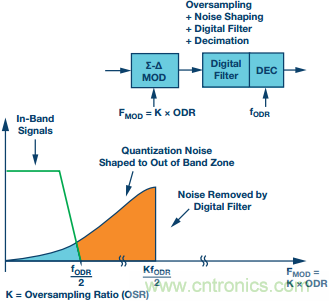

它通常包括兩個模塊:Σ-Δ調(diào)制器和數(shù)字信號處理模塊,后者通常是數(shù)字濾波器。Σ-Δ型ADC的簡要框圖和主要概念如圖1所示。

圖1. Σ-Δ型ADC的關(guān)鍵概念。

Σ-Δ調(diào)制器是一種過采樣架構(gòu),因此,我們從奈奎斯特采樣理論和方案以及過采樣ADC操作開始討論。

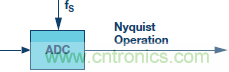

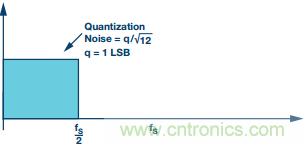

圖2比較了ADC的奈奎斯特操作、過采樣方案和Σ-Δ調(diào)制(也是過采樣)方案。

圖2. Nyquist comparison

圖2a顯示了ADC以標(biāo)準(zhǔn)奈奎斯特方式運(yùn)行時的量化噪聲。這種情況下,量化噪聲由ADC的LSB大小決定。FS為ADC的采樣速率,F(xiàn)S/2為奈奎斯特頻率。圖2b顯示的是同一轉(zhuǎn)換器,不過現(xiàn)在它以過采樣方式運(yùn)行,采樣速率更快。采樣速率提高K倍,量化噪聲擴(kuò)展到K × FS/2的帶寬上。低通數(shù)字濾波器(通常帶抽取功能)可消除藍(lán)色區(qū)域之外的量化噪聲。

圖2a. 奈奎斯特方案。采樣速率為FS,奈奎斯特帶寬為FS/2。

圖2b. 過采樣方案。采樣速率為K × FS。

Σ-Δ調(diào)制器多了一個特性,那就是噪聲整形,如圖2c所示。模數(shù)轉(zhuǎn)換的量化噪聲被調(diào)制整形,從低頻移動到較高頻率(通常如此),低通數(shù)字濾波器可將其從轉(zhuǎn)換結(jié)果中消除。Σ-Δ型ADC的噪底由熱噪聲決定,而不受量化噪聲的限制。

圖2c. Σ-Δ型ADC方案。過采樣和噪聲整形,采樣速率為FMOD = K × FODR。

采樣、調(diào)制、濾波

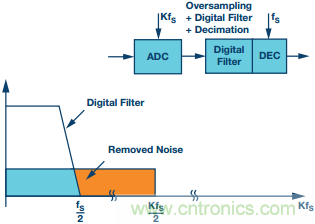

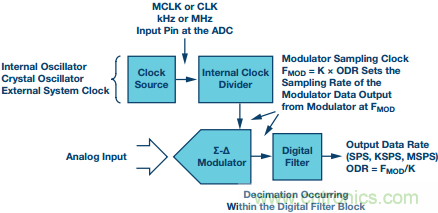

Σ-Δ型ADC使用內(nèi)部或外部采樣時鐘。ADC的主時鐘(MCLK)常常要先分頻,再交由調(diào)制器使用;閱讀ADC數(shù)據(jù)手冊時應(yīng)注意這點(diǎn),并了解調(diào)制器頻率。傳送到調(diào)制器的時鐘設(shè)置采樣頻率FMOD。調(diào)制器以該速率將數(shù)據(jù)輸出到數(shù)字濾波器,進(jìn)而數(shù)字濾波器(通常為低通,帶抽取功能)以輸出數(shù)據(jù)速率(ODR)提供數(shù)據(jù)。圖3顯示了這一過程。

圖3. Σ-Δ ADC流程:從調(diào)制器輸出到數(shù)字濾波輸出的采樣。

一階Σ-Δ調(diào)制器的深入觀察

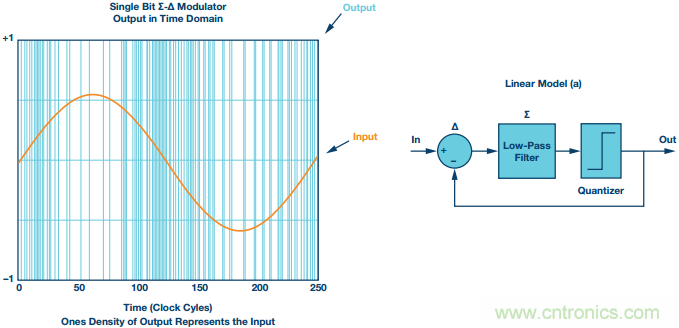

Σ-Δ調(diào)制器是一種負(fù)反饋系統(tǒng),與閉環(huán)放大器相似。環(huán)路包含低分辨率ADC和DAC,以及一個環(huán)路濾波器。輸出和反饋被粗略量化,常常只有一比特表示高電平或低電平的輸出。ADC的模擬系統(tǒng)實(shí)現(xiàn)了這種基本結(jié)構(gòu),量化器就是完成采樣的模塊。如果存在保證環(huán)路穩(wěn)定的條件,那么輸出就是輸入的粗略表示。數(shù)字濾波器獲得該粗略輸出并重構(gòu)模擬輸入的精確數(shù)字轉(zhuǎn)換結(jié)果。

圖4顯示了響應(yīng)一個正弦波輸入的1密度輸出。調(diào)制器輸出從低電平到高電平的變化率取決于輸入的變化率。當(dāng)正弦波輸入為正滿量程時,調(diào)制器輸出開關(guān)速率會降低,輸出以+1狀態(tài)為主。同樣,當(dāng)正弦波輸入為負(fù)滿量程時,+1和–1之間的轉(zhuǎn)換會減少,輸出以–1為主。當(dāng)正弦波輸入處于最大變化率時,調(diào)制器輸出發(fā)生最高密度的+1和–1切換。輸出變化率與輸入變化率同步。因此,模擬輸入由Σ-Δ調(diào)制器輸出的轉(zhuǎn)換率來描述。

圖4. 輸入正弦波的Σ-Δ輸出1碼值的密度。1階Σ-Δ調(diào)制器環(huán)路的線性模型(a)。

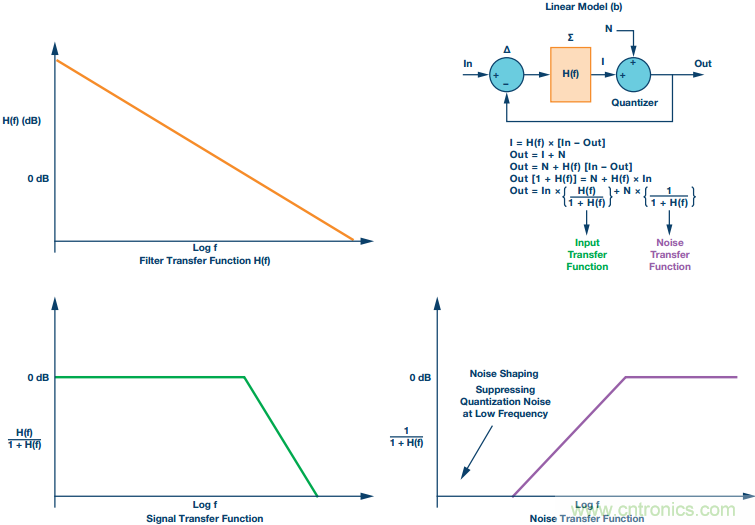

若使用線性模型來描述這種1位調(diào)制器(Mod 1),則可將該系統(tǒng)表示為一個帶負(fù)反饋的控制系統(tǒng)。量化噪聲為量化器的輸入與輸出之差。輸入偏差節(jié)點(diǎn)之后是一個低通濾波器。在圖5b中,量化噪聲用N來表示。

圖5. Mod 1 Σ-Δ環(huán)路的線性模型(b),包括方程、濾波器、信號和噪聲傳遞函數(shù)圖。

H(f)是環(huán)路濾波器的函數(shù),定義噪聲和信號的傳遞函數(shù)。H(f)是一個低通濾波器函數(shù),在低頻(目標(biāo)帶寬內(nèi))時具有非常高的增益,可衰減高頻信號。環(huán)路濾波器可實(shí)現(xiàn)為簡單的積分器或積分器級聯(lián)。實(shí)踐中常常把一個DAC放在反饋路徑中,以便獲取數(shù)字輸出信號并將其轉(zhuǎn)換為模擬信號反饋到模擬輸入偏差節(jié)點(diǎn)。

解出圖5所示方程便可得到信號和噪聲傳遞函數(shù)。信號傳遞函數(shù)用作一個低通濾波器,在目標(biāo)帶寬內(nèi)的增益為1。噪聲傳遞函數(shù)是一個高通濾波器函數(shù),提供噪聲整形,在DC附近的較低頻率,對量化噪聲有很強(qiáng)的抑制。在超出目標(biāo)帶寬的較高頻率看到的量化噪聲會增加。對于一階調(diào)制器(Mod 1),噪聲以大約20 dB/十倍頻程的速率提高。

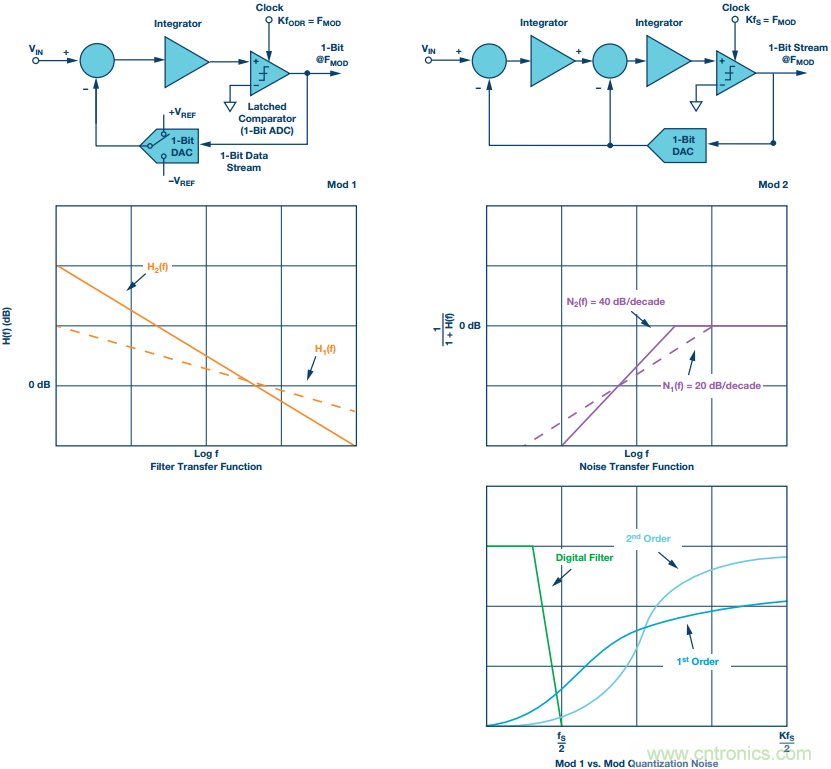

為了提高系統(tǒng)分辨率,常見方法是將兩個環(huán)路濾波器級聯(lián)起來以增加環(huán)路濾波器階數(shù)?,F(xiàn)在,總環(huán)路濾波器的H(f)具有更大的滾降,Mod 2型的噪聲傳遞函數(shù)具有40 dB/十倍頻程的上升速率。噪聲所處的頻率越低,噪聲整形就越厲害。圖6比較了Mod 1型和Mod 2型Σ-Δ ADC。Σ-Δ調(diào)制器的變化和樣式非常多。 規(guī)避了高階1位環(huán)路穩(wěn)定性問題的架構(gòu)稱為多級噪聲整形調(diào)制器(MASH)架構(gòu)。多級(MASH型)架構(gòu)支持通過具有內(nèi)在穩(wěn)定性的低階環(huán)路組合來設(shè)計(jì)穩(wěn)定的高階Σ-Δ調(diào)制器。

圖6. Mod 1和Mod 2框圖配置以及濾波器和噪聲傳遞函數(shù)的比較圖。

推薦閱讀: