【導讀】場效應管的存在工程師們并不陌生,但是鰭式場效晶體管估計不是所有人都了解的。鰭式場效晶體管卻對集成電路物理設計及可測性設計流程具有重大影響。故了解鰭式場效晶體管是很必要的。本文將為大家詳解鰭式場效晶體管集成電路設計以及它的相關測試,話說做戲也要做全套的,希望對大家有用。

鰭式場效晶體管的出現對集成電路物理設計及可測性設計流程具有重大影響。鰭式場效晶體管的引進意味著在集成電路設計制程中互補金屬氧化物(CMOS)晶體管必須被建模成三維(3D)的器件,這就包含了各種復雜性和不確定性。加州大學伯克利分校器件組的BSIM集團開發(fā)出了一個模型,被稱作BSIM-CMG (common multi-gate)模型,來代表存在鰭式場效晶體管的電阻和電容。晶圓代工廠竭力提供精準器件及寄生數據,同時也致力于保留先前工藝所采用的使用模型。

寄生提取挑戰(zhàn)

然而,每個晶圓代工廠都會修改標準模型以使得更貼切地表現特定的架構和工藝。此外,在這些先進的工藝節(jié)點處,晶圓代工廠希望其通過參考場解算器建立的“黃金”模型與該領域設計人員使用提取工具得到的結果有更緊密的關聯(lián)。在28納米級節(jié)點,晶圓代工廠希望商業(yè)提取工具精度介于其黃金模型的5%到10%之間。對于鰭式場效晶體管工藝,晶圓代工廠要求商業(yè)提取工具與黃金模型之間的平均精度誤差在2%以內,3倍離散標準偏差僅為6%-7%。

最具挑戰(zhàn)性的任務是計算鰭式場效晶體管與其周圍環(huán)境之間更復雜且無法估量的相互之間的寄生數據,這需要涉及前段制程(FEOL)幾何結構的精確3D建模。確保三維空間中的精度需要使用3D場解算器進行提取。3D場解算器在先前用于制程特性而非設計,因為其計算成本太高且速率太慢。現在新一代的三維提取工具,比如Mentor的Calibre xACT,通過采用自我調整網格化技術加速計算的方法使其運行速度比之前快了一個數量級。其還有可利用現代多CPU計算環(huán)境的高度可擴容架構。有了這些功能,提取工具可以輕松地在32 CPU機器上執(zhí)行場解算器計算解決方案,小至數個單元大至數百萬內嵌晶體管的模塊。

在全芯片層次,我們需要考慮數十億晶體管設計以及幾千萬根連接導線,即使是快速場解算器也無法提出實用的周轉時間。解決方法是采用先進的啟發(fā)式算法,對于復雜的結構采用場解算器,對于一般的幾何圖形可采用基于表格的提取方法 (table-based)。這種方法是可行的,由于在布線網格中的電場模型類似于前制程節(jié)點所見的。在最理想的情況下,設計工程師所用的提取使用模型不會改變,因為提取工具會自動在場解算器和表格方法之間移動。

隨著雙重和三重光罩在從20納米級節(jié)點制造開始中扮演著越來越重要的作用,我們正經歷著互連角點(interconnect corners)數量的飛躍。在28納米,5個互連角點是可能的,然而對于16納米級,我們預計需要11-15個角點。先進的多角點分析計劃可以實現更高效的計算,減少每個額外角點所需的額外計算量。此外,我們可以并行處理角點,以使每一個額外角點僅增加10%的整體周轉時間。這意味著15個角點只需要2.5倍的單個角點運行時間。

[page]

測試挑戰(zhàn)

測試和失效分析是特別重要的,因為鰭式場效晶體管的關鍵尺寸首次比底層節(jié)點尺寸小得多。這使得提高的缺陷水平以及增加良率的挑戰(zhàn)日益受到關注。單元識別(Cell-Aware)的測試方法特別適合于解決這些問題,因為它可以鎖定晶體管級的缺陷。相對來說,傳統(tǒng)的掃描測試模式只能識別單元之間互連件的缺陷。單元識別分析過程建立一個基于單元布局內缺陷仿真行為的故障模型。結果能生產出更高質量的圖形向量。當采用單元識別方式自動產生測試圖形向量(ATPG),硅驗證結果表明從350納米級到鰭式場效晶體管級的技術節(jié)點,明顯檢測出額外更多的缺陷,超出固定模式及過渡模式。

考慮具有三個鰭的多鰭式場效晶體管。最近的研究建議,這樣的晶體管應考慮兩個缺陷類型:導致晶體管部分或全部擊穿的泄漏缺陷以及導致晶體管部分或完全關閉的驅動強度缺陷。

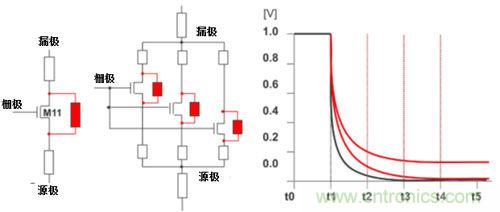

圖1:鰭式場效晶體管泄漏缺陷的測試

泄漏缺陷可以通過在每個晶體管的3鰭片兩端柵極(從漏極到源極)放置電阻來分析,如圖1所示。在單元識別分析過程中,模擬仿真(analog simulation)在一個給定單元庫對于所有鰭式場效晶體管的所有不同電阻值的電阻進行。在晶體管在一定門閾值的情況下響應延遲,對缺陷進行建模。驅動強度缺陷可以通過在漏極和每個柵極之間以及在源極和柵極之間放置電阻的方法來分析。至于泄漏測試,模擬仿真通過改變每個電阻的電阻值來進行。每個鰭片的響應時間差異用于決定是否需要進行缺陷建模。其他的鰭式場效晶體管缺陷類型可以通過類似的方法來處理。

鰭式場效晶體管確實帶來了一些新的挑戰(zhàn),但電子設計自動化工具供貨商和晶圓代工廠會盡全力以對集成電路設計流程影響最小的方式整合解決方案。

相關閱讀:

http://me3buy.cn/power-art/80020398

http://me3buy.cn/test-art/80019709