【導(dǎo)讀】石英晶振是石英晶體諧振器和石英晶體時(shí)鐘振蕩器的統(tǒng)稱,它是一種用于穩(wěn)定頻率和選擇頻率的電子元件�,可分無源晶振和有源晶振兩種類型。

1 晶振介紹

石英晶振是石英晶體諧振器和石英晶體時(shí)鐘振蕩器的統(tǒng)稱��,它是一種用于穩(wěn)定頻率和選擇頻率的電子元件����,可分無源晶振和有源晶振兩種類型��。

(1) 無源晶振為Crystal(晶體)

其必須借助外部的有源激勵(lì)和振蕩電路才能起振�����,振蕩頻率主要取決于晶體的切割方式,外部振蕩電路也部分影響著振蕩頻率的精度��。振蕩電路中包含兩個(gè)Trim電容�,由于電容的精度一般比較低,因此即便是完全相同的電路圖�����,振蕩頻率的頻偏也可能存在一定的差別���。

(2) 有源晶振Oscollator(振蕩器)

它是將振蕩電路和晶體集成在一個(gè)封裝內(nèi)�����,加電即可輸出時(shí)鐘信號���,頻率精度較高,價(jià)格也略高�����。

2 常用的晶振的技術(shù)指標(biāo)

(1) 基準(zhǔn)頻率:晶振在完全理想條件下的振蕩頻率���。

(2) 工作電壓:晶振的工作需要外部提供一定的電源電壓�����,晶振輸出的時(shí)鐘信號上的噪聲與電源再說緊密相關(guān)����,因此在晶振器件資料上����,對電源的質(zhì)量有一定的要求。

(3) 輸出電平:晶振與晶體相比����,最為突出的一點(diǎn)就是只要上電,就直接輸出時(shí)鐘信號����。時(shí)鐘信號的電平也多種多樣,支持的電平主要包括:TTL��、CMOS��、HCMOS���、LVCOMS�、LVPECL、LVDS等��。在選型中�,應(yīng)根據(jù)所需時(shí)鐘電平的種類選擇相應(yīng)的晶振。

(4) 工作溫度范圍:根據(jù)環(huán)境溫度要求的不同����,應(yīng)選擇對應(yīng)的工作溫度范圍。

(5) 頻率精度:對應(yīng)不同的工作溫度范圍���,可選擇不同的頻率精度�。以±15ppm@-20~70℃為例��,其含義是�,在-20~70℃溫度范圍內(nèi),該晶振輸出頻率相對基準(zhǔn)頻率的偏差不會(huì)超過15ppm����。該參數(shù)是晶振的重要參數(shù),包含了由于溫度變化��、電源電壓波動(dòng)�、負(fù)載變化等因素引起的頻率偏差。

(6) 老化度:在恒定的外接條件下測量晶振頻率,頻率精度與時(shí)間之間的關(guān)系����。

(7) 啟動(dòng)時(shí)間:從上電到晶振輸出頻率的偏差達(dá)到規(guī)定的頻率精度所需要的時(shí)間。

(8) 時(shí)鐘抖動(dòng)(Jitter):在后面內(nèi)容詳細(xì)介紹�����。

(9) 相位噪聲:在后面內(nèi)容詳細(xì)介紹����。

3 有源晶振的類型包括以下幾類

(1) 普通封裝晶體振蕩器(SPXO)

它無溫度補(bǔ)償功能����,也無電壓控制功能,其頻率特性完全取決于晶體以及外部振蕩電路���。標(biāo)準(zhǔn)頻率為1~100MHz�,頻率精度最高可達(dá)±10ppm���。由于SPXO不包含任何頻率補(bǔ)償功能��,因此是晶振中精度最差的一個(gè)種類����,價(jià)格低廉,通常作為微處理器的時(shí)鐘器件���。在PCB布局時(shí)�����,SPXO器件應(yīng)遠(yuǎn)離發(fā)熱源�。

(2) 壓控式晶體振蕩器(VCXO)

VCXO是通過外部施加控制電壓時(shí)振蕩頻率可調(diào)的晶體振蕩器�。它的特點(diǎn):輸出頻率可以通過輸入電壓控制,一般控制范圍為±50~±200ppm��。工作原理:通過改變外加調(diào)整電壓的大小����,能改變?nèi)菪载?fù)載CL的值,從而實(shí)現(xiàn)頻率的調(diào)整��。由于VCXO的具有振蕩頻率可調(diào)整的特點(diǎn)�����,所以用頻率—溫度穩(wěn)定度來定義環(huán)境溫度變化對頻偏的影響����。由于VCXO不具備溫度補(bǔ)償功能�,因此在PCB布局時(shí)����,VCXO器件應(yīng)遠(yuǎn)離發(fā)熱源。VCXO除了電源電源外�����,還需要控制電壓����,以調(diào)整輸出頻率����,當(dāng)控制電壓調(diào)整為中央電壓時(shí),VCXO輸出標(biāo)稱的基準(zhǔn)頻率�����。VCXO常用在鎖相環(huán)電路中��。

(3) 溫度補(bǔ)償晶體振蕩器(TCXO)

TCXO是利用附件的溫度補(bǔ)償電路以減少環(huán)境溫度對振蕩頻率的影響����,其特點(diǎn)是頻率精度遠(yuǎn)遠(yuǎn)高于SPXO和VCXO����。工作原理:利用熱敏電阻的溫度敏感性����,當(dāng)溫度變化時(shí),熱敏電阻的阻值和容性負(fù)載同時(shí)發(fā)生變化����,而容性負(fù)載的變化會(huì)改變振蕩頻率,從而實(shí)現(xiàn)對振蕩頻率的修正��。

(4) 恒溫晶體振蕩器(OCXO)

將晶體和振蕩電路置于恒溫箱中��,以消除環(huán)境溫度變化對頻率的影響��。頻率精度為10-10~10-8量級��。頻率穩(wěn)定度在四種類型振蕩器中最高���。

不同的特性決定了四種類型晶振的應(yīng)用場合:如果需要設(shè)備即開即用����,需選用SPXO、VCXO和TCXO�。OCXO晶振需要一定的穩(wěn)定時(shí)間。如果要求時(shí)鐘信號較高的穩(wěn)定度���,推薦使用TCXO和OCXO�。

4 時(shí)鐘抖動(dòng)與相位噪聲

數(shù)字信號的各個(gè)有效邊沿相對于其理想位置都存在一定的偏離����,對于其中的短期性偏離(頻率在10Hz以上的偏離),使用時(shí)鐘抖動(dòng)和相位噪聲參數(shù)來定義�;對于其中的長期性偏離(頻率在10Hz以內(nèi)的偏離),使用漂移來定義��。其中漂移容易被CDR(Clock Data Recovery��,時(shí)鐘數(shù)據(jù)恢復(fù)電路)等模塊濾除�����。時(shí)鐘信號的質(zhì)量通常用抖動(dòng)和相位噪聲來描述���。時(shí)鐘抖動(dòng)和相位噪聲的區(qū)別在于:時(shí)鐘抖動(dòng)是時(shí)域的概念;相位噪聲是頻域的概念�����。時(shí)鐘抖動(dòng)通常分為時(shí)間間隔誤差(Time Interval Error,簡稱TIE)���、周期抖動(dòng)和相鄰周期抖動(dòng)��。以下重點(diǎn)討論周期抖動(dòng)和相位噪聲的關(guān)系�����。

1�����、時(shí)鐘抖動(dòng)

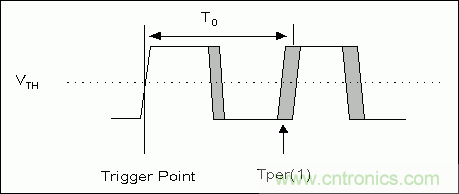

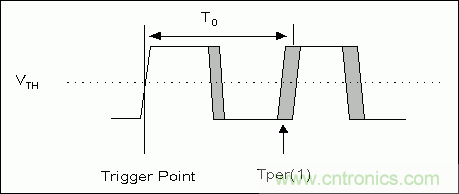

周期抖動(dòng)(JPER)是實(shí)測周期與理想周期之間的時(shí)間差��。由于具有隨機(jī)分布的特點(diǎn)�����,可以用峰-峰值或均方根(RMS)描述���。首先定義門限VTH的時(shí)鐘上升沿位于時(shí)域的TPER(n),其中n是一個(gè)時(shí)域系統(tǒng)�����,如圖1所示。JPER表示為:

其中T0是理想時(shí)鐘周期���。由于時(shí)鐘頻率固定��,隨機(jī)抖動(dòng)JPER的均值應(yīng)該為零����,JPER的RMS可表示為:

圖1 周期抖動(dòng)測量

利用示波器的邊沿觸發(fā)和余輝功能����,可以粗略的測量信號的抖動(dòng)。使用該方法的測量并不具有實(shí)際意義��。原因:(1)隨著測量時(shí)間的增加����,測得的抖動(dòng)值將不斷增加����,即利用這種測量方法,無法得到確定的抖動(dòng)值���;(2)即使能得到確定的抖動(dòng)值�����,這樣的值對電路設(shè)計(jì)也沒有任何指導(dǎo)意義����,只能粗略判斷所使用的晶振的抖動(dòng)情況。

2�����、相位噪聲

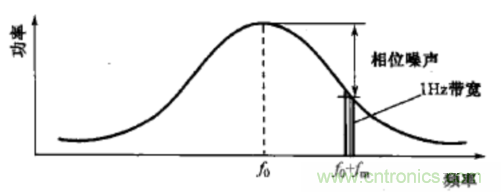

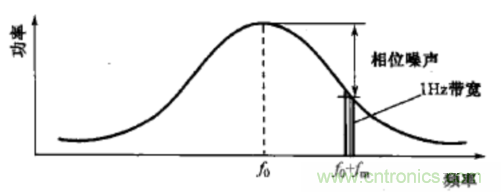

相位噪聲:在頻域上�����,數(shù)據(jù)偏移量用相位噪聲來定義��。如圖2所示為典型的相位噪聲曲線圖��。橫軸代表頻率��,單位是Hz����,縱軸代表功率譜密度�,單位是dBc/Hz��。

對于頻率為f0的時(shí)鐘信號而言����,如果信號上不含抖動(dòng),則信號的所有功率應(yīng)集中在頻率點(diǎn)f0處�����,由于任何信號都存在抖動(dòng)��,這些抖動(dòng)有些是隨機(jī)的�,有些是確定的,分布于相當(dāng)廣的頻帶上�,因此抖動(dòng)的出現(xiàn)將使信號功率被擴(kuò)展到這些頻帶上。信號的相位噪聲��,就是信號在某一特定頻率處的功率分量���,將這些分量連接成的曲線就是相位噪聲曲線��。相位噪聲通常定義為在某一給定偏移處的dBc/Hz值�,其中dBc是以dB為單位的該功率處功率與總功率的比值���。如一個(gè)振蕩器在某一偏移頻率處的相位噪聲定義為在該頻率處1Hz帶寬內(nèi)的信號功率與信號總功率的比值�����,即在fm頻率處1Hz范圍內(nèi)的面積與整個(gè)噪聲頻率下的所有面積之比�。

圖2 信號相位噪聲曲線圖

從相位噪聲曲線圖可知����,絕大多數(shù)抖動(dòng)都集中在頻率f0附近��,距離f0越遠(yuǎn)的頻段���,抖動(dòng)能量越小��。

以下面的例子為例�����,說明對時(shí)鐘輸入的要求:

RMS JPER(12kHz~20MHz):0.5ps

相位噪聲(10~100kHz):-120dBc/Hz

這實(shí)際上是兩個(gè)要求��,一個(gè)是要求在頻段12kHz~20MHz內(nèi)����,均方根抖動(dòng)不能大于0.5ps;另一方面要求在頻段10~100kHz內(nèi)��,任何頻點(diǎn)處的功率譜密度都不能超過-120dBc/Hz�����。

5 使用頻譜分析儀測量相位噪聲的步驟

(1) 在頻譜分析儀上設(shè)置與被測信號頻率相同的中心頻率(Center Frequence)�����,并使被測信號靠近屏幕的左側(cè)�����。

(2) 在頻譜分析儀上設(shè)置參考電平(REF LEVEL)��,略大于或等于被測載波信號的實(shí)際輸出電平值��。

(3) 在頻譜分析儀上根據(jù)被測信號頻率的大小設(shè)置適當(dāng)?shù)膾哳l寬度(SPAN)�����、分辨率帶寬(RWB)�����、視頻帶寬(VBW)使其能顯示被測信號在有效帶寬內(nèi)的一個(gè)或兩個(gè)噪聲邊帶。

(4) 用頻譜分析儀分別測量載波功率PC和指定偏離載波f處的邊帶噪聲功率Pm���。也可以直接用頻譜分析儀的ΔMARKER功能測出PC和Pm的差值,并記錄此時(shí)的RBW�����。

(5) 對指定頻偏點(diǎn)的單邊帶相位噪聲按以下公式計(jì)算歸一化的相位噪聲值����。

Ψ(f)=Pm/Pc-10lg1.2RBW/(1Hz)+2.5

如果頻譜分析儀具備歸一化的相位噪聲計(jì)算分析測量軟件����,則可直接測得已經(jīng)歸一化的相位噪聲值�����。

測試中的注意事項(xiàng):

(1) 頻譜儀的本振相位噪聲應(yīng)低于被測源的相位噪聲��。(對于有源晶振而言,該點(diǎn)一般都滿足)��。

(2) 頻譜儀應(yīng)去多次測試平均值����。

(3) 頻譜儀的分辨率帶寬RBW值應(yīng)盡量小��。

6 晶振電路設(shè)計(jì)

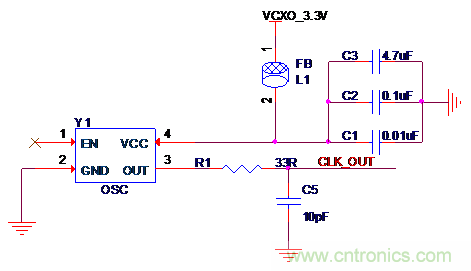

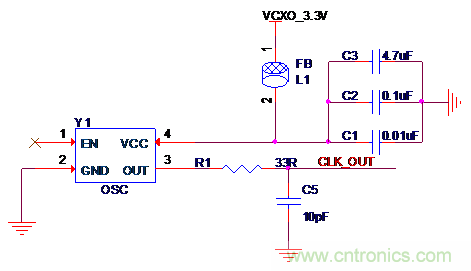

有源晶振EMC標(biāo)準(zhǔn)設(shè)計(jì)電路如下:

原理圖注意事項(xiàng):

(1) 有源晶振的電源引腳最好不要直接接電源�����,而是通過一個(gè)磁珠后接入�����,這可大大降低電源噪聲對時(shí)鐘輸出頻率的影響��。晶振電源的去耦電容的匹配也很重要�����,去耦電容一般選3個(gè)�,容值依次遞減。

(2) 有源晶振的時(shí)鐘輸出端串聯(lián)一個(gè)小電阻�����,作用是為了減少信號反射,以免造成信號反射引起的信號過沖���。電阻R1是預(yù)留匹配設(shè)計(jì)�,可根據(jù)實(shí)驗(yàn)情況進(jìn)行阻值調(diào)整�。其具體作用如下:

可以減少諧波����。有源晶振的輸出是方波,當(dāng)阻抗嚴(yán)重不匹配的時(shí)候?qū)⒁鹬C波干擾�����。加上串聯(lián)電阻后��,該電阻與輸入電容構(gòu)成RC電路����,將方波變成正弦波。

可以進(jìn)行阻抗匹配����,減少反射信號的干擾���。

(3) C5是預(yù)留設(shè)計(jì),可根據(jù)實(shí)驗(yàn)情況進(jìn)行調(diào)整����,它的作用是:與串聯(lián)電阻組成RC濾波電路,減少時(shí)鐘信號的過沖���。

PCB設(shè)計(jì)注意事項(xiàng):

(1) 耦合電容應(yīng)盡量靠近晶振的電源引腳����,位置擺放順序:按電源流入方向����,依容值從大到小依次擺放,容值最小的電容最靠近電源引腳��。

(2) 晶振的外殼必須接地�,可以晶振的向外輻射,也可以屏蔽外來信號對晶振的干擾�����。

(3) 晶振下面不要布線��,保證完全鋪地,同時(shí)在晶振的300mil范圍內(nèi)不要布線����,這樣可以防止晶振干擾其他布線、器件和層的性能��。

(4) 時(shí)鐘信號的走線應(yīng)盡量短�����,線寬大一些��,在布線長度和遠(yuǎn)離發(fā)熱源上尋找平衡����。

(5) 晶振不要放置在PCB板的邊緣����,在板卡設(shè)計(jì)時(shí)尤其注意該點(diǎn)。

推薦閱讀: