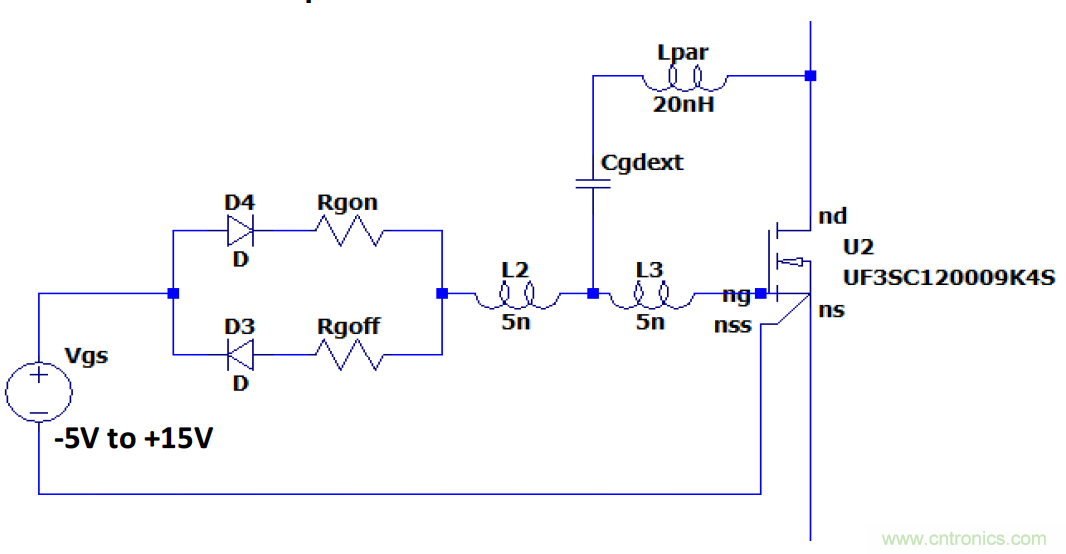

在使用獨立器件的真實應(yīng)用中���,這種寄生電感應(yīng)該遠(yuǎn)小于20nH���,因為外部CGD可能會置于電路板上靠近FET的位置����。然而���,如果在模塊內(nèi)使用UnitedSiC FET芯片��,并將外部CGD置于模塊外��,則路徑中可能會存在20nH的寄生電感�。

我們首先使用UF3SC120009K4S SPICE模塊通過SPICE模擬優(yōu)化外部CGD方法���,然后使用雙脈沖測試電路對其進(jìn)行實驗驗證�。68pF的外部CGD被有意焊接在TO247-4L的C引腳和D引腳之間�����,而不是電路板上�����,以提高路徑中的寄生電感��。

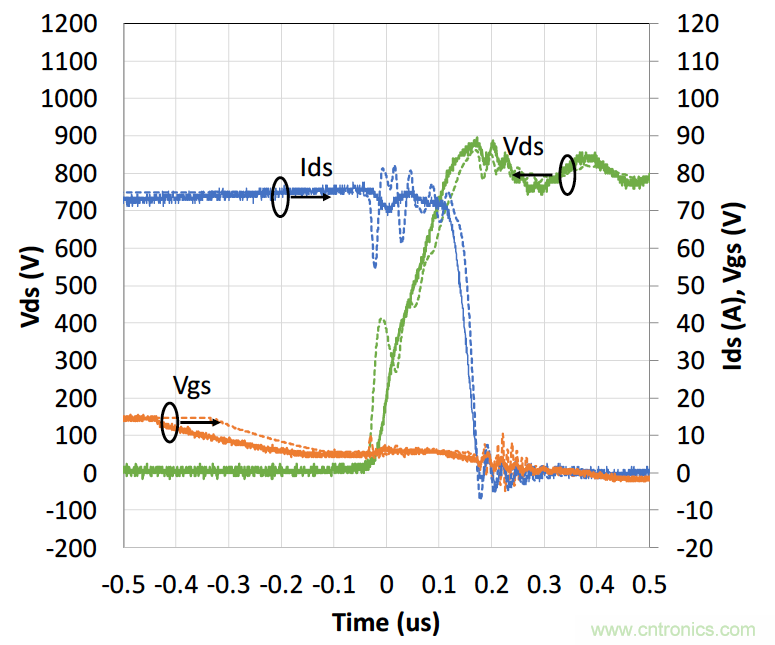

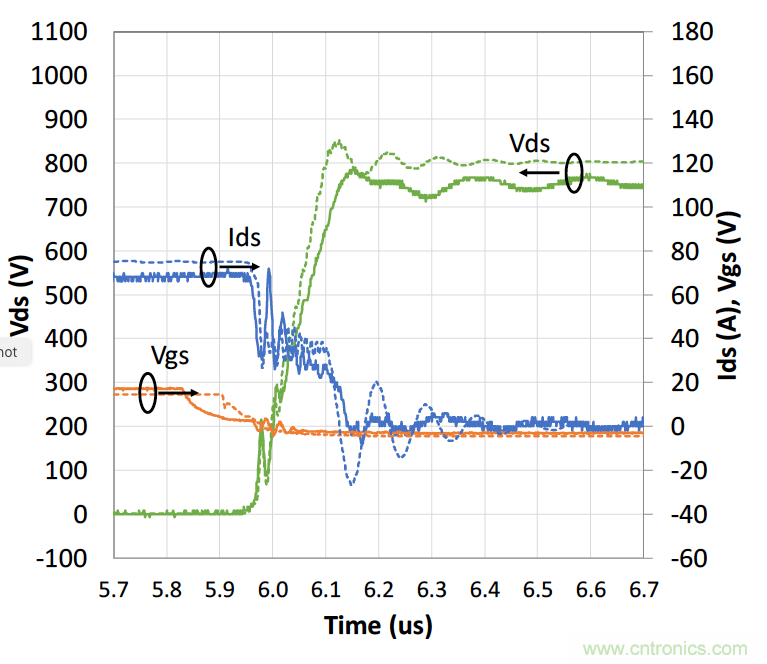

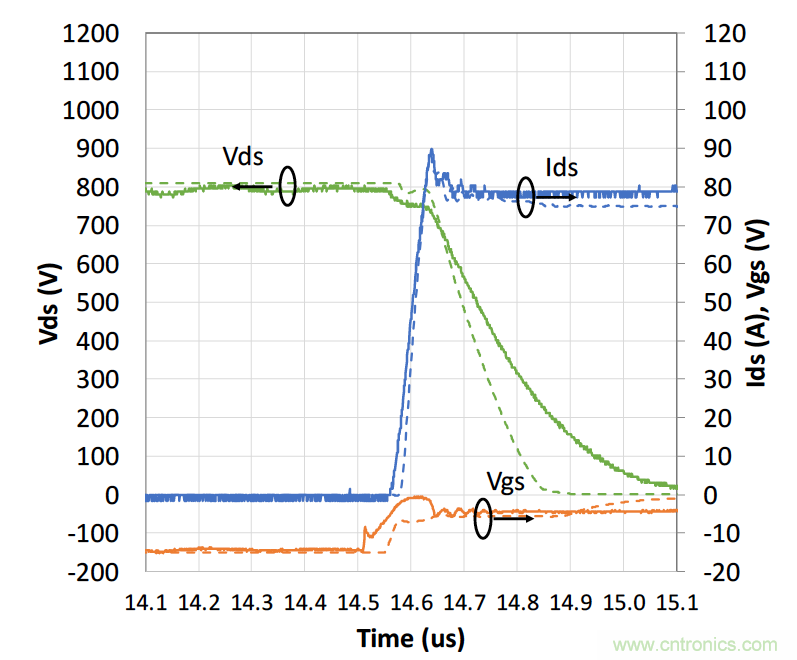

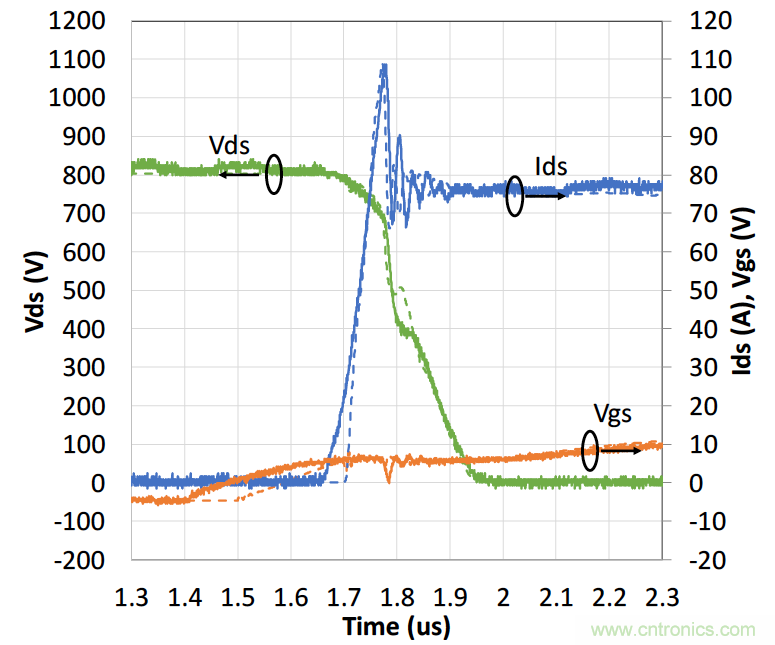

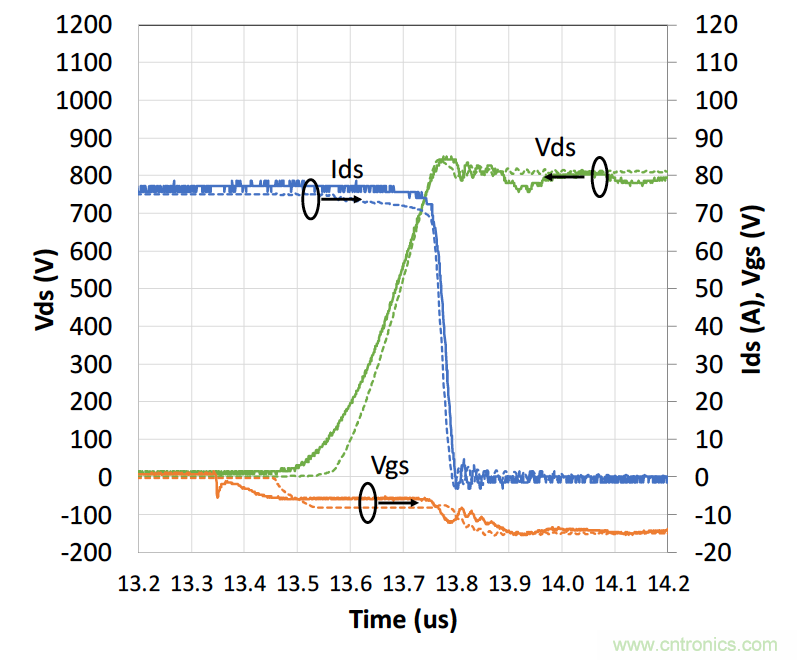

從實驗測量和SPICE模擬中得到的關(guān)閉和打開波形被疊加在一起以進(jìn)行比較。在圖2中��,測量波形和模擬波形非常吻合��。

圖2 實驗測量(實線)和SPICE模擬(虛線)的關(guān)閉(左)和打開波形疊加(75A�����,800V���,外部CGD為68pF���,RG為33?)

在外部CGD為68pF的情況下,使用10?至33?的RG可以將dV/dt有效控制在25V/ns至5V/ns范圍內(nèi)���。對于SPICE和實驗��,通過計算打開和關(guān)閉轉(zhuǎn)換期間的IDS×VDS得到EON和EOFF�����,該值和預(yù)計一樣隨RG增加。

外部CGD可以容忍高寄生電感(在SPICE中為20nH)的原因是開關(guān)期間的電流非常小��。對于外部CGD為68pF,dV/dt為8V/ns的情況�����,估計電流僅為0.54A且與SPICE模擬中的電流一致�����。因此�����,它適用于模塊����,在采用模塊形式時,外部CGD置于模塊外�����,位于電路板柵極驅(qū)動上���,且路徑中有一些寄生電感��。

器件RC緩沖電路

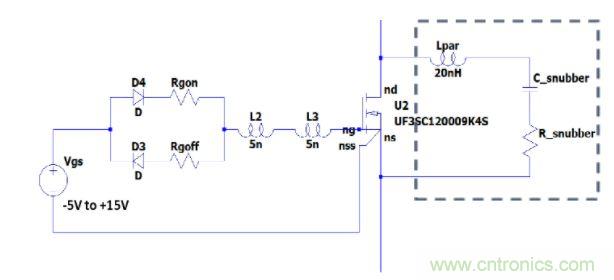

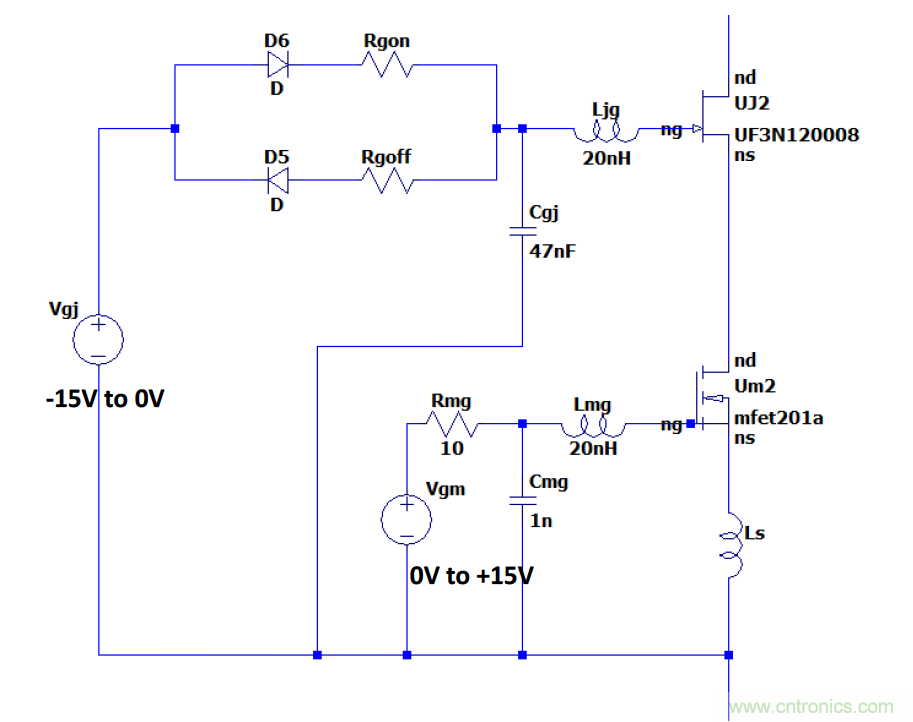

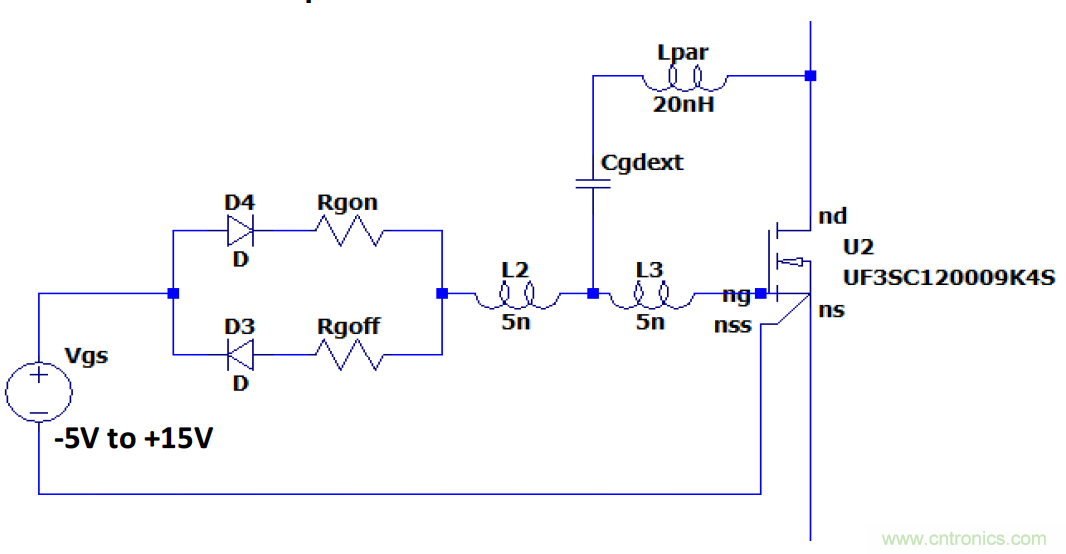

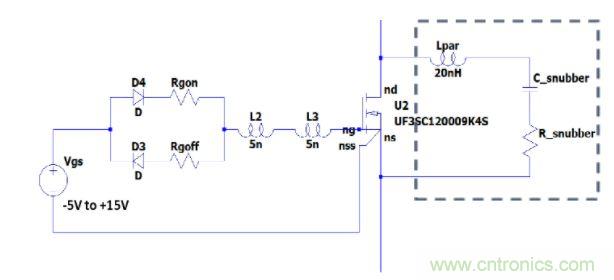

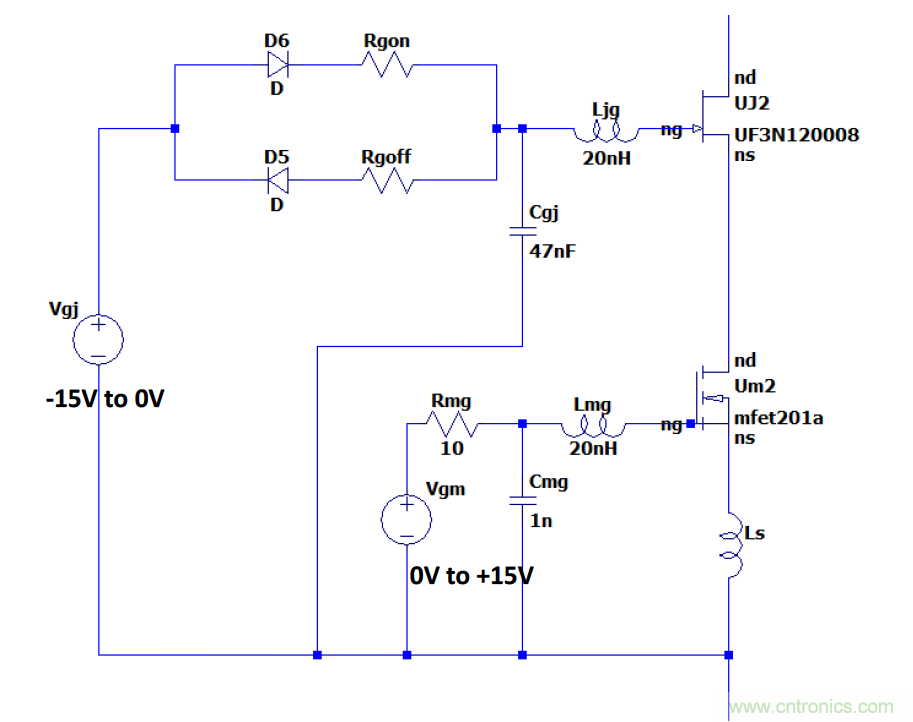

第二個dV/dt控制方法將RC緩沖電路與高側(cè)開關(guān)和低側(cè)開關(guān)并聯(lián)����。我們故意將一個20nH寄生電感與緩沖電路串聯(lián),旨在證明這種方法的緩沖電路路徑中可以容忍寄生電感(圖3)�����。

圖 3 RC緩沖電路與FET并聯(lián)(包括高側(cè)和低側(cè)FET)以實現(xiàn)dV/dt控制

在使用獨立器件的真實應(yīng)用中���,RC緩沖電路可能非??拷麱ET���,且寄生電感僅為幾nH����。但是如果在模塊內(nèi)采用UnitedSiC FET芯片�,則RC緩沖電路可以置于模塊外,且路徑中可能存在20nH的寄生電感��。

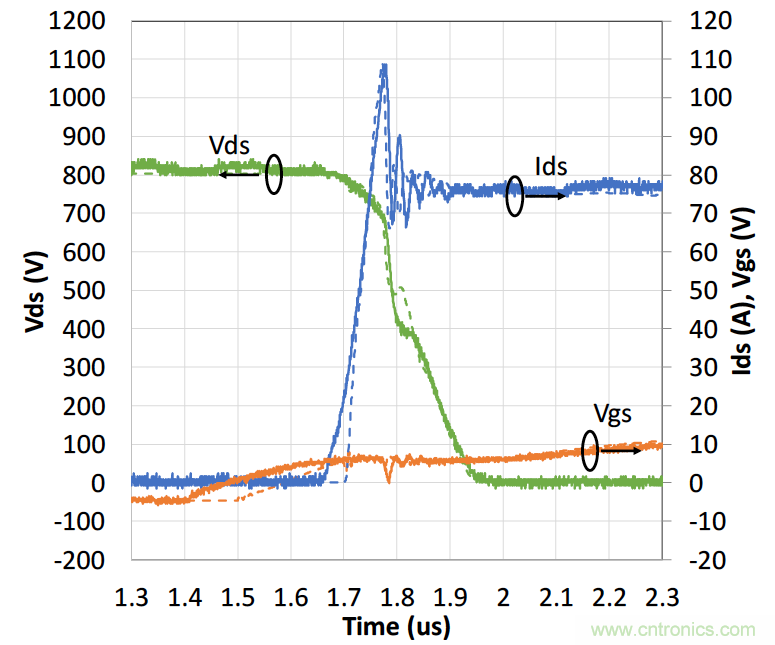

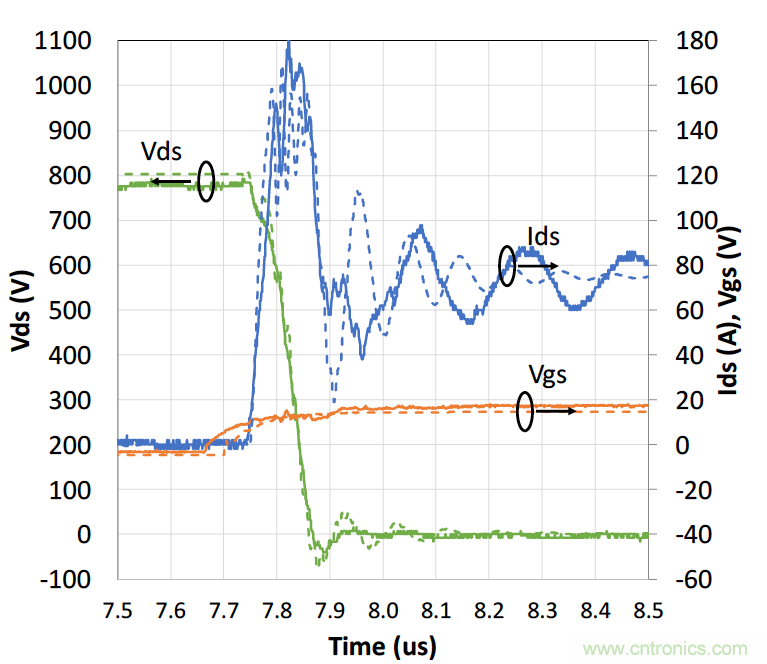

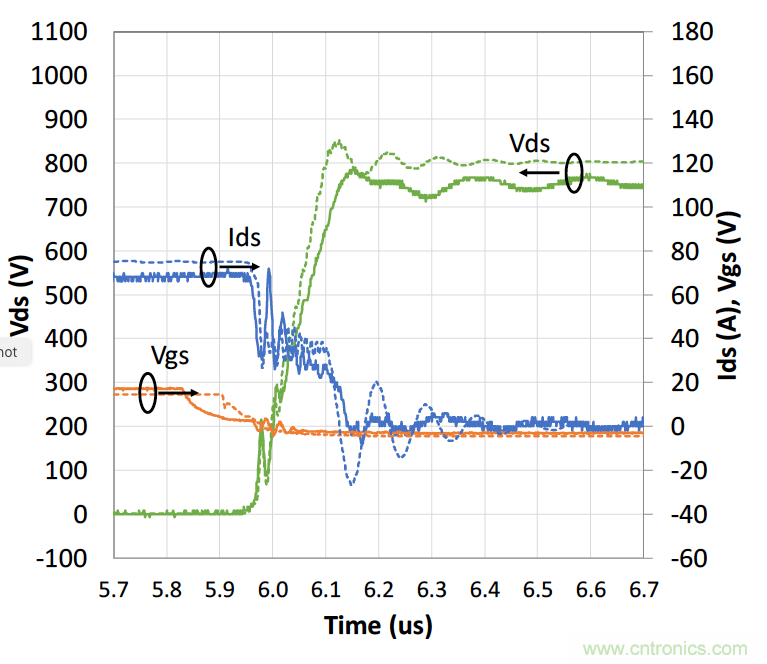

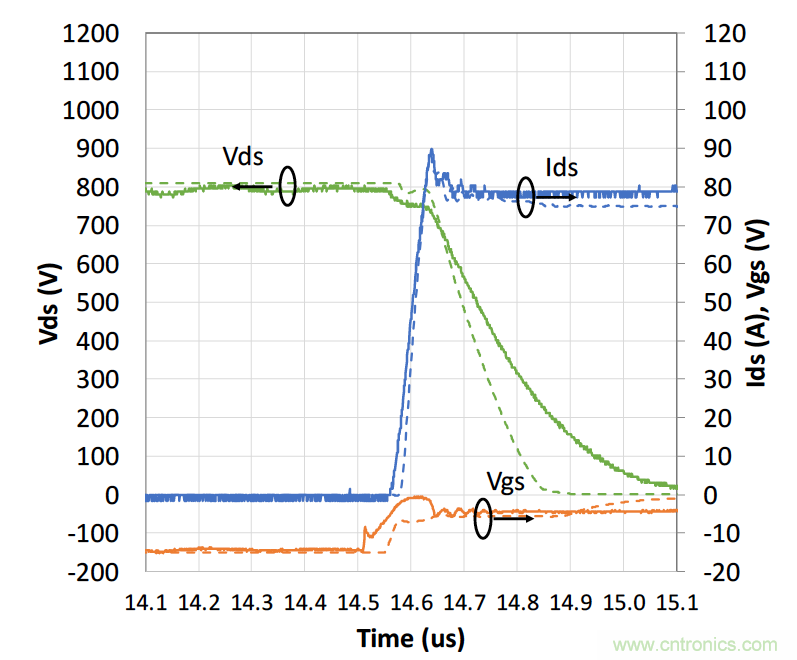

從實驗測量和SPICE模擬中得到的關(guān)閉和打開波形被疊加在一起以進(jìn)行比較(圖4)��。請注意��,圖表中的IDS電流包含緩沖電路電流。實驗和SPICE模擬表明��,dV/dt可以被最高5.6nF的C_SNUBBER(緩沖電路電容器)有效控制在50V/ns至5V/ns范圍內(nèi)����。

圖 4實驗測量(實線)和SPICE模擬(虛線)的關(guān)閉(左)和打開波形疊加(75A�,800V,RC緩沖電路為0.5?����,5.6nF)

開關(guān)損耗(EON、EOFF和ESW)通過計算開關(guān)轉(zhuǎn)換期間的IDS×VDS得到���,其中IDS包括緩沖電路電流��。因此�����,EON和EOFF中包含緩沖電路的損耗����。然而����,0.5? R_SNUBBER上的緩沖電路損耗非常低���,尤其是當(dāng)dV/dt較慢時。在C_SNUBBER為4nF��,關(guān)閉dV/dt=8V/ns時�����,SPICE表明����,緩沖電路損耗僅為0.2mJ,即在開關(guān)f=10kHz時為2W��。我們發(fā)現(xiàn)�����,緩沖電路也能容忍高寄生電感(在SPICE中為20nH)���,因此����,如果使用模塊形式,RC緩沖電路可以置于模塊外�����。

JFET直接驅(qū)動

第三種方法是直接驅(qū)動�����,在這種情況下�����,Si MOS僅會在電路啟動后打開一次��,JFET柵極直接切換到-15V到0V之間(圖5)���。在這種配置中,常關(guān)操作會被保留����,不過會需要柵極PWM和簡單的“啟用”信號。

在開關(guān)瞬態(tài)���,高側(cè)JFET保持關(guān)閉且電壓為-15V�����,需要同步整流才能讓續(xù)流JFET將第三象限中的通導(dǎo)損耗降低���。

圖5 JFET直接驅(qū)動方法(在高側(cè)和低側(cè)FET上均有)以實現(xiàn)dV/dt控制

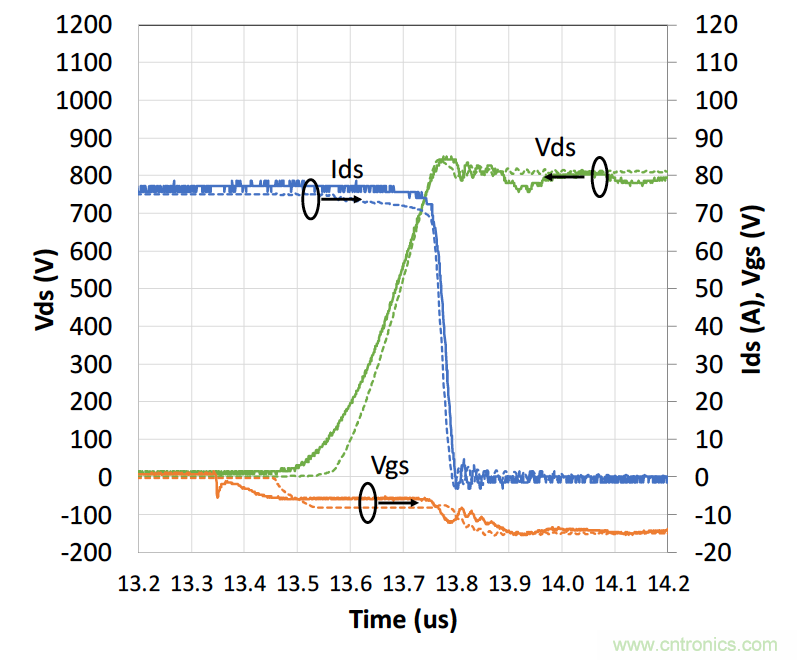

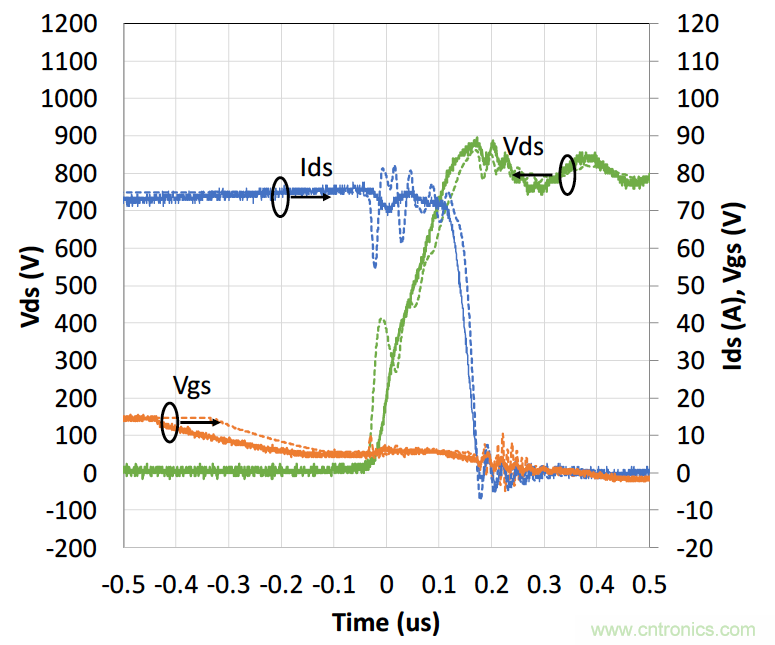

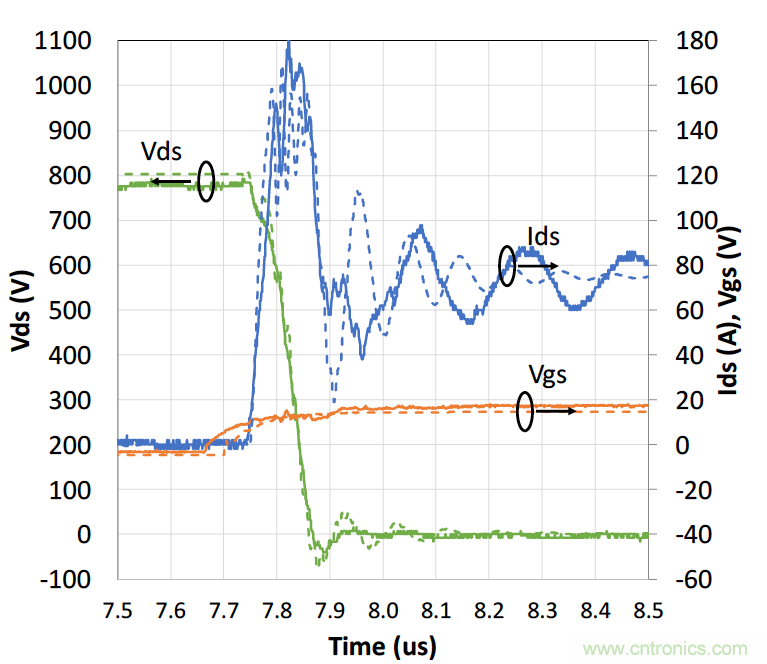

因為SiC JFET有可觀的CRSS(CGD)����,所以一個4.7?的小RG就足以將dV/dt放緩至5V/ns��。從實驗測量和SPICE模擬中得到的關(guān)閉和打開波形被疊加在一起以進(jìn)行比較(圖6)���。

圖6 實驗測量(實線)和SPICE模擬(虛線)的關(guān)閉(左)和打開波形疊加(75A�,800V�����,JFET直接驅(qū)動且RG為4.7?)

SPICE(虛線)與實驗(實線)波形間的IDS電流波形十分吻合�����。但是實驗VDS波形表明其dV/dt比SPICE波形慢�。原因可能是在dV/dt變換期間實驗中使用的JFET柵極驅(qū)動器不能提供足夠的柵極電流來為JFET CRSS充電和放電,導(dǎo)致dV/dt放慢��。

將SPICE和測量得到的dV/dt進(jìn)行比較會發(fā)現(xiàn),可以將dV/dt很好地控制在15V/ns到4V/ns之間�����。使用與前兩種方法相同的做法可以得到開關(guān)損耗����,EON和EOFF和預(yù)計一樣隨著JFET RG增加。

三種dV/dt控制方法比較

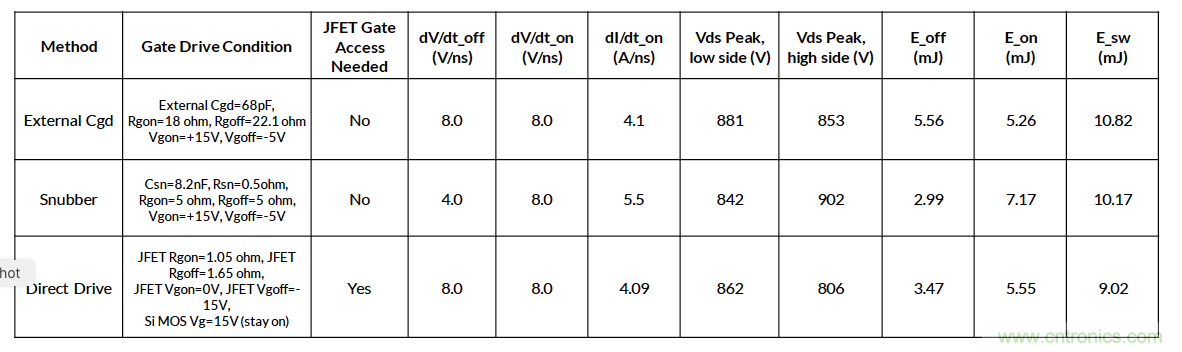

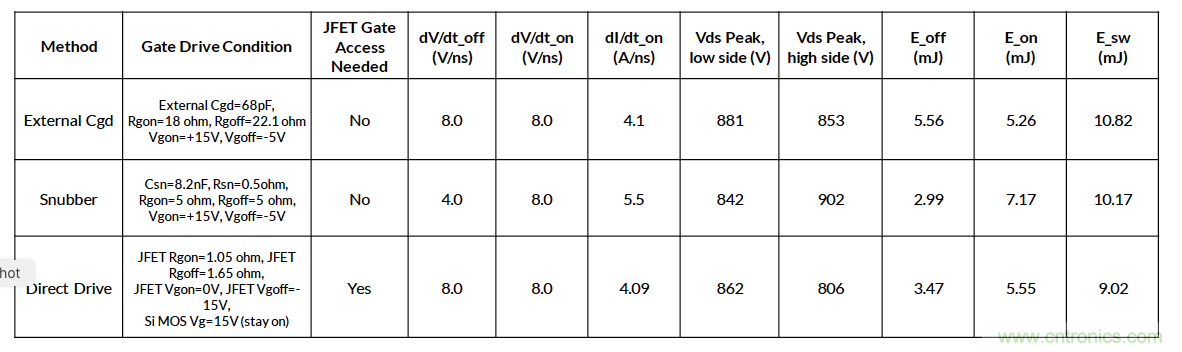

在dV/dt ≤ 8V/ns這一相同限制下����,使用SPICE模擬對這三種方法進(jìn)行了比較(圖1)�����。

表1 在dV/dt最大等于8V/ns的情況下��,SPICE模擬的75A/800V開關(guān)下的性能

JFET直接驅(qū)動方法表現(xiàn)出的整體開關(guān)損耗最低���,為9.02mJ����。與其他兩種方法相比���,這種方法需要負(fù)壓才能驅(qū)動SiC JFET�,并且需要在電路啟動時為Si MOS提供啟用信號,從而增加了柵極驅(qū)動的復(fù)雜性����。標(biāo)準(zhǔn)UnitedSiC FET不提供到JFET柵極的通路,但是新的雙柵極TO247-4L產(chǎn)品正在開發(fā)中��,既有SiC JFET柵極和Si MOS柵極�����,又適合JFET柵極驅(qū)動�����。這種方法還適合模塊�,可以添加單獨的JFET柵極引腳。如此項研究所示�,JFET柵極路徑可忍受合理的寄生電感(在SPICE中為20nH),因此可以將JFET柵極驅(qū)動器放置在模塊頂部的柵極驅(qū)動電路板上���。

外部CGD和器件RC緩沖電路方法表現(xiàn)出了較高的開關(guān)損耗����,但是它們不需要到JFET柵極的通路。當(dāng)在獨立封裝(如TO247)中使用UnitedSiC FET時��,兩種方法都可以輕松實施到電路板上�����。由于這兩種方法可以忍受合理的寄生電感(在SPICE中為20nH)���,它們還適合內(nèi)部有UnitedSiC芯片的模塊��。

RC緩沖電路方法的一個缺點是它不能分別調(diào)整關(guān)閉和打開dV/dt�。如表1所示���,要實現(xiàn)8V/ns的打開dV/dt,關(guān)閉dV/dt必須降低至4V/ns���,這會提高EOFF��。

然而�,外部CGD和JFET直接驅(qū)動方法使用單獨的RGON和RGOFF�,可以分別調(diào)整這二者。如表1所示����,通過分別優(yōu)化RGON和RGOFF�����,可以讓打開和關(guān)閉dV/dt均為8V/ns���。

總結(jié)

總而言之,運用這些簡單技術(shù)可以實現(xiàn)良好的dV/dt控制���。較低的通導(dǎo)損耗和短路穩(wěn)健性這兩個UnitedSiC FET優(yōu)勢對于高效可靠的電動機(jī)驅(qū)動應(yīng)用而言極為重要����。