【導讀】電阻在電路中起限制電流的作用。上拉電阻和下拉電阻是經(jīng)常提到也是經(jīng)常用到的電阻。在每個系統(tǒng)的設計中都用到了大量的上拉電阻和下拉電阻。

在上拉電阻和下拉電阻的電路中,經(jīng)常有的疑問是:上拉電阻為何能上拉?下拉電阻為何能下拉?下拉電阻旁邊為何經(jīng)常會串一個電阻?

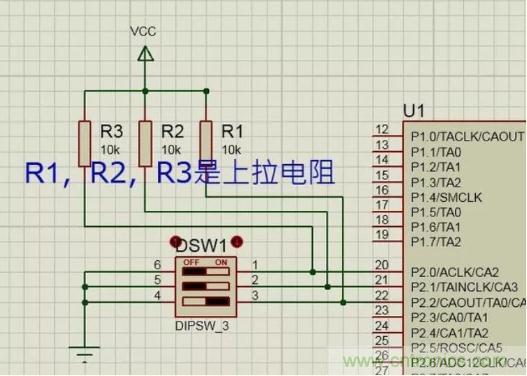

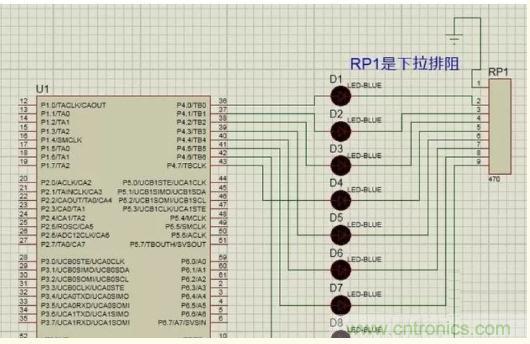

簡單概括為:電源到器件引腳上的電阻叫上拉電阻,作用是平時使該引腳為高電平,地到器件引腳上的電阻叫下拉電阻,作用是平時使該引腳為低電平。低電平在IC內(nèi)部與GND相連接;高電平在IC內(nèi)部與超大電阻相連接。

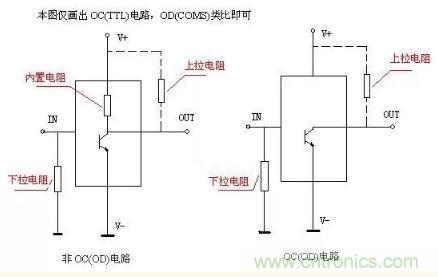

上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用,下拉同理。對于非集電極(或漏極)開路輸出型電路(如普通門電路,其提升電流和電壓的能力是有限的,上拉和下拉電阻的主要功能是為集電極開路輸出型電路提供輸出電流通道。上拉是對器件注入電流,下拉是輸出電流;強弱只是上拉或下拉電阻的阻值不同,沒有什么嚴格區(qū)分。

當IC的I/O端口,節(jié)點為高電平時,節(jié)點處和GND之間的阻抗很大,可以理解為無窮大,這個時候通過上拉電阻(如4.7K歐,10K歐電阻)接到VCC上,上拉電阻的分壓幾乎可以忽略不計;當I/O端口節(jié)點需要為低電平時,直接接GND就可以了,這個時候VCC與GND是通過剛才的上拉電阻(如4.7K歐,10K歐電阻)連接的,通過的電流很小,可以忽略不計。

電平值的大小、高低是相對于地電平來說的,因此在看電平值的大小時要參考地的電平值來看??纯茨切┮_是否接到地上,與自己是否連接外圍器件沒有關系,因為其實高電平還是低電平是相對于地平面來說的。

在節(jié)點與+5V之間接10K歐或4.7K歐的上拉電阻,能夠把這個節(jié)點的電位拉上來,往往這個節(jié)點要求應用單片機或其它控制器來控制它(及這個節(jié)點與I/O連接)為高電平或低電平。如果單純的想要使這個節(jié)點成為高電平,并且輸出阻抗非常大,則直接接電源也無妨,但是如果單片機要使這個節(jié)點拉低,即單片機內(nèi)部使節(jié)點接地,這樣5V電源和地之間就短路了。

另外,當要求這個節(jié)點為高電平時,這個節(jié)點和地之間的阻抗一般非常大,如100K歐的阻抗,當上拉一個10K歐的電阻,這個點分得的電壓為100K歐/(100K+10K)*5V=4.5V,這樣也可以拉到高電平。而當要求這個節(jié)點為低電平時,只要把它和地連接就可以了,電源和地之間有一個10K偶的電阻,這樣就不會短路了。當?shù)碗娖綍r,電源和地之間有一個負載形成的回路,有時候這個節(jié)點會再串接一個電阻,因為電流流向阻抗低的地方,所以電流會通過與電源相連的電阻流向地,而不是流向這個與節(jié)點相連的電阻,因為這個節(jié)點連接的電阻阻抗高,所以低電平時這個點的電勢就是低電平。

可以這么認為,對于IC的I/O端口來說,IC內(nèi)部通過控制高低電平相當于控制這個O/O口與其內(nèi)部的GND或非常大的電阻相連,如100K歐,當I/O口為低電平0V時,在IC內(nèi)部,是控制IC芯片O/O口的引腳在芯片內(nèi)與GND連接;當I/O口為高電平時,如5V,這個時候I/O口引腳在芯片內(nèi)是與非常大的電阻,如100K歐相連接的,有時在I/O節(jié)點處會再串接一個小電阻值的電阻,如68歐,因為電流流向阻抗低的地方,所以當芯片內(nèi)部的I/O端口歐與GND相連為低電平時,電源與上拉電阻及芯片內(nèi)部的GND形成環(huán)路進行流通,這時I/O口節(jié)點處的電流就會流向芯片內(nèi)部的GND,因為節(jié)點處串接了一個小阻值的電阻,相對于GND來說是高阻,就是大一點點也是高阻,所以電流就不會流過這個串聯(lián)的電阻。

當用下拉電阻時(所謂的上拉和下拉都是針對高阻態(tài)而言的),當I/O口為高阻態(tài)時,通過上拉電阻能夠讓其保持在高電平狀態(tài);具體如上文所述:當I/O端口為高阻態(tài)時,用下拉電阻把這個口與GND相連接,高阻態(tài)電阻值很大,可以理解為斷開,其實就是和芯片內(nèi)部的阻值很大的電阻相連接,下拉的時候拉到地上了,沒有電流,電平值為0,除非是給這個引腳賦予一個高電平值它才能夠起作用。

上拉和下拉電阻的作用概括如下:

1、提高電壓準位

當TTL電路驅動CMOS電路時,如果TTL電路輸出的高電平低于CMOS電路的最低高電平,這時就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值;OC門電路必須加上拉電阻,以提高輸出的高電平值。

2、加大輸出引腳的驅動能力

有的單片機引腳上也常使用上拉電阻。

3、N/A引腳(沒有連接的引腳)防靜電、防干擾

在CMOS芯片上,為了防止靜電造成損壞,不用的引腳不能懸空,一般接上拉電阻降低輸入阻抗,提供泄荷通路。同時引腳懸空就比較容易接收外界的電磁干擾。

4、電阻匹配

抑制反射波干擾,長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻使電阻匹配,能有效的抑制反射波干擾。

5、預設空間狀態(tài)/默認電位

在一些CMOS輸入端接上拉或下拉電阻是為了預設默認電位。當不用這些引腳時,這些輸入端下拉接低電平或上拉接高電平。在I2C等總線上空閑時的狀態(tài)是由上下拉電阻獲得的。

6、提高芯片輸入信號的噪聲容限

輸入端如果是高阻狀態(tài),或高阻抗輸入端處于懸空狀態(tài),此時需要加上拉或下拉電阻,以免受到隨機電平的影響,進而影響電路工作。同樣,如果輸出端處于被動狀態(tài),需要加上拉或下拉電阻,如輸出端僅僅是一個三極管的集電極,從而提高芯片輸入信號的噪聲容限,增強抗干擾能力。

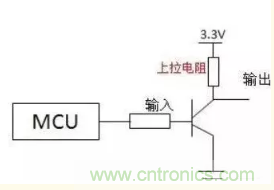

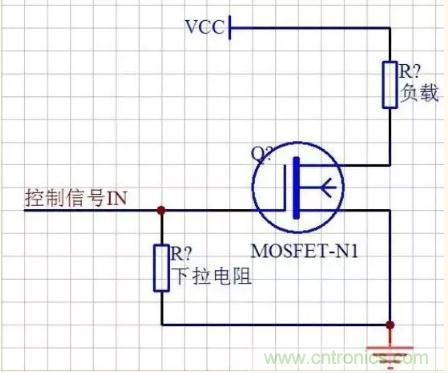

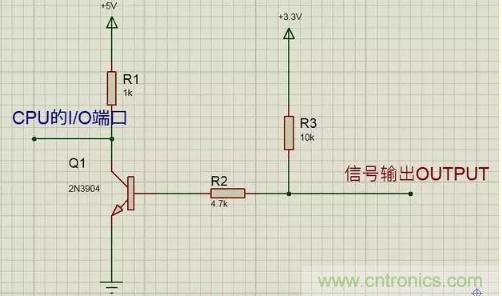

在BJT晶體三極管的基極端,上拉電阻和下拉電阻也起著至關重要的作用。在三極管的電路應用中,串接在基極上的電阻起限制基級電流的作用,如下圖中的R2所示,

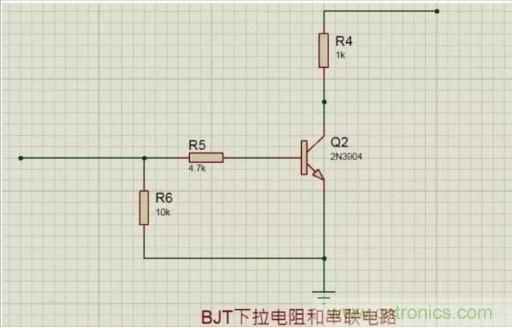

如下圖中的R5所示,上拉電阻使三極管基極的輸入電平在默認情況下是高電平輸入,當CPU有低電平信號輸出時,外圍電路響應,下拉電阻使晶體管的基極輸入在默認情況下拉到低電平,如下圖中的R6所示。

來源:網(wǎng)絡