【導(dǎo)讀】同步降壓穩(wěn)壓器是一種常用的電源 ,隨著各類應(yīng)用要求的不斷提高,行業(yè)越來越趨向于追求高能效、高可靠性、高功率密度的設(shè)計方案。本文將介紹快速設(shè)計出高效可靠的同步降壓穩(wěn)壓器的技術(shù), 以及安森美半導(dǎo)體的 Power Supply WebDesigner在線設(shè)計工具,幇助工程師解決所面臨的技術(shù)挑戰(zhàn)。

同步降壓穩(wěn)壓器是一種常用的電源 ,隨著各類應(yīng)用要求的不斷提高,行業(yè)越來越趨向于追求高能效、高可靠性、高功率密度的設(shè)計方案。比如 應(yīng)用于無線局域網(wǎng)的負載點(PoL)電源,輸入電壓越來越寬,工作頻率、功率密度也越來越高,隨著技術(shù)的發(fā)展,甚至可將整個電源系統(tǒng)集成在單個封裝中。同步降壓穩(wěn)壓器其電路結(jié)構(gòu)本身非常簡單, 但工程師要完成高效可靠的同步降壓穩(wěn)壓器的設(shè)計,還是有著不少的技術(shù)挑戰(zhàn),必須對穩(wěn)壓器電路的各種工作狀態(tài)有著非常深入、透徹的了解,同時還需完成大量的計算工作。本文將介紹快速設(shè)計出高效可靠的同步降壓穩(wěn)壓器的技術(shù), 以及安森美半導(dǎo)體的 Power Supply WebDesigner在線設(shè)計工具,幇助工程師解決所面臨的技術(shù)挑戰(zhàn)。

動態(tài)性能的設(shè)計

設(shè)計一個可靠的同步降壓穩(wěn)壓器,首先必須滿足其動態(tài)性能指標(biāo)如負載響應(yīng)能力。而輸出電感、電容的選擇會直接影響到穩(wěn)壓器的動態(tài)性能,所以同步降壓穩(wěn)壓器的功率電路設(shè)計通常是從選擇輸出電感和電容開始。

1、選擇電感

從電路設(shè)計的角度,為實現(xiàn)快速瞬態(tài)響應(yīng), 必須選擇盡可能小的輸出濾波電感和最小的輸出電容。然而小的電感值會增加電感電流紋波,導(dǎo)致電感中有效電流值增加而使得導(dǎo)通損耗增大,同時所導(dǎo)致的峰值電流的增加,也會大大增加控制管的開關(guān)損耗。

使用大電感,可減小電感中的電流紋波,從而降低穩(wěn)態(tài)輸出電壓紋波,所導(dǎo)致的低峰值電流也有助于降低MOSFET的開關(guān)損耗,但電感太大不僅會導(dǎo)致相對較大的直流阻抗,產(chǎn)生較高的電感損耗,還會降低穩(wěn)壓器的負載響應(yīng)能力,從而降低穩(wěn)壓器的動態(tài)性能。

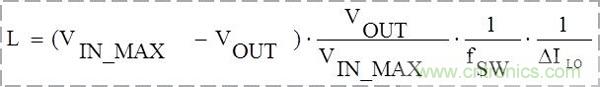

為選擇適當(dāng)?shù)碾姼?,通??杉俣娏骷y波ΔILO為電感平均電流的30%,然后根據(jù)下面的公式直接計算出合適的電感值。

2、選擇電容

最小輸出電容的選擇必須考慮到兩個因素:一是穩(wěn)態(tài)下輸出電壓紋波的要求,二是當(dāng)負載從滿載到空載突變時所允許的最大輸出過沖電壓。

但輸出電容也不是越大越好,太大的輸出電容及電容本身的寄生串聯(lián)電阻會影響到穩(wěn)壓器的輸出電路的性能以及當(dāng)負載突變時穩(wěn)壓器的瞬態(tài)響應(yīng)能力。

通常,輸出電容應(yīng)首選: 一,有較小等效串聯(lián)電阻(ESR)的電容, 以便降低交流損耗和輸出紋波; 二, 有較小等效串聯(lián)電感(ESL)的電容, 以便在負載突變時抑制輸出偏差。

能效設(shè)計

作為控制管和同步整流開關(guān), 功率MOSFET廣泛用于降壓穩(wěn)壓器中。它們消耗大部分的損耗功率,通常決定了穩(wěn)壓器的整體能效。

1、選擇最佳的MOSFET

針對不同的設(shè)計要求,比如是想要成本最低,還是想要損耗最低,又或是想要封裝盡可能小等等,需要選擇不同的MOSFET。

考慮到額定電流通常與MOSFET成本成正比,有的工程師會根據(jù)額定電流的大小來選擇MOSFET,希望以此來控制產(chǎn)品成本;為最大限度地降低導(dǎo)通損耗,有的工程師則會選擇具有最低RDS(ON)的MOSFET;還有的根據(jù)質(zhì)量因數(shù)(FOM)= RDS(ON)xQg(TOT)來進行選擇,希望能平衡導(dǎo)通損耗和開關(guān)損耗……這些依賴于參數(shù)的選擇方法其實都有不足。使用額定電流及電壓的方法沒有考慮具體的開關(guān)損耗;而最低RDS(ON)法,成本可能會佷高,且MOSFET寄生電容可能導(dǎo)致更低的能效; FOM法則不能預(yù)測能效或成本。

因此,無論是為了降低成本,提高能效,還是為了設(shè)計更緊湊的產(chǎn)品,必須完整計算出電路損耗及工作溫度,才能確保設(shè)計出的產(chǎn)品能工作在可靠的工作溫度范圍,達到最佳的能效。

2、計算MOSFET的損耗

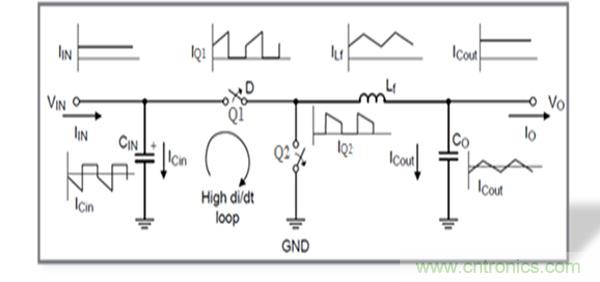

在計算損耗前,需要先了解MOSFET在同步降壓穩(wěn)壓器中的工作機制。圖1所示為簡化的穩(wěn)壓器的功率電路原理圖,其中Q1為控制管,Q2 為同步管。

圖1:簡化的穩(wěn)壓器的功率電路原理圖

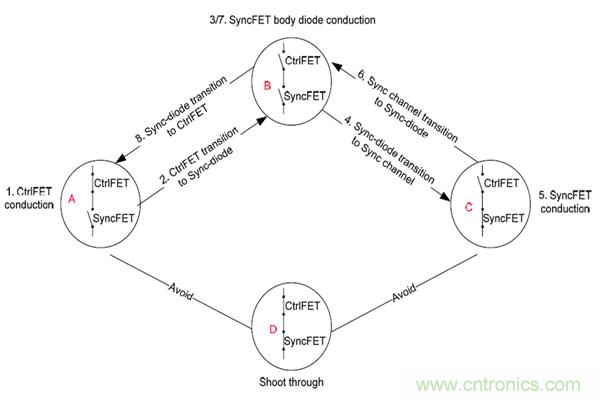

同步降壓穩(wěn)壓器主要有3種工作狀態(tài),其開關(guān)順序是A-B-C-B-A,如圖2所示。

圖2:同步降壓穩(wěn)壓器的開關(guān)順序

狀態(tài)A:控制管導(dǎo)通,輸入電流經(jīng)過控制管、電感傳送到輸出端。

狀態(tài)B:控制管和同步管同時關(guān)斷,電感儲能通過同步管的寄生二極管放電,傳送到輸出端。

狀態(tài)C:同步管導(dǎo)通,電感儲能通過同步管放電,傳送到輸出端。

MOSFET的功耗包括控制管和同步管的導(dǎo)通損耗(PCOND)、控制管的開關(guān)損耗PSW、同步管的開關(guān)損耗、控制管和同步管的柵極驅(qū)動損耗PRgate。在140 kHz頻率下導(dǎo)通損耗幾乎占總功耗的70%。隨著頻率升高,總功耗中逐漸以開關(guān)損耗(PSW)為主。

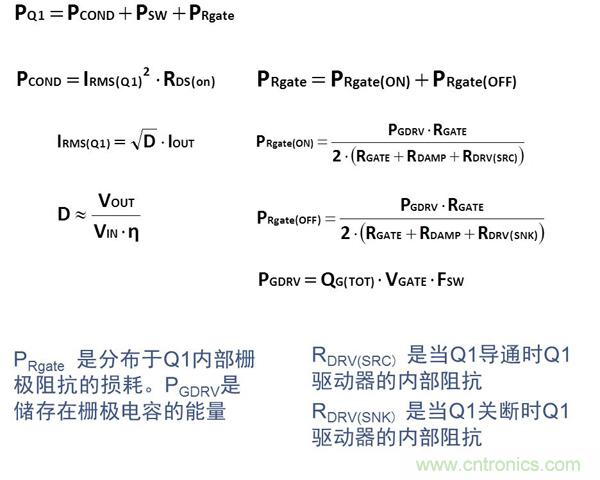

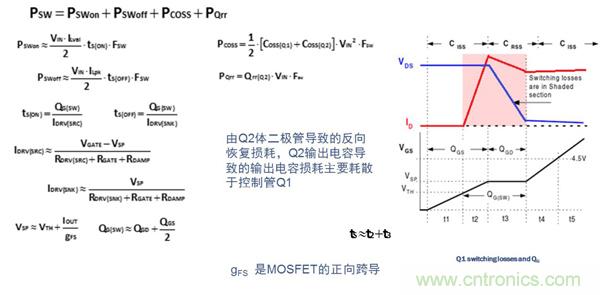

1). 控制管Q1的損耗計算

Q1工作在硬開關(guān)條件下,在小占空比或高頻(> MHz)時以開關(guān)損耗為主,開關(guān)性能受同步管Q2影響:快速di/dt可導(dǎo)致反向恢復(fù)損耗增加,快速dv/dt有可能引起Q2誤導(dǎo)通, 造成Q1、Q2直通現(xiàn)象,導(dǎo)致額外的損耗。另外,值得注意的是,由Q2體二極管導(dǎo)致的反向恢復(fù)損耗、 Q2輸出電容導(dǎo)致的輸出電容損耗主要耗散于控制管Q1上 [Ref. 1,2]。因此,在計算Q1的開關(guān)損耗和溫度時必須綜合考慮到Q2的影響。另外,Q1的導(dǎo)通阻抗隨結(jié)溫上升而上升。結(jié)溫越高,導(dǎo)通阻抗越高,導(dǎo)通損耗就越高, 使得結(jié)溫進一步上升。因此,對Q1的導(dǎo)通損耗必須循環(huán)反復(fù)計算,直到管子的溫度計算結(jié)果穩(wěn)定下來。

對于高頻應(yīng)用(>MHz),控制管Q1的選用應(yīng)針對降低開關(guān)損耗進行優(yōu)化。Q1損耗的計算公式如下:

Q1的導(dǎo)通損耗PCOND隨輸入電壓(VIN)增加而降低,開關(guān)損耗PSW隨VIN增加而增加,柵極驅(qū)動損耗PRgate與VIN無關(guān)。當(dāng)VIN為最大或最小時,Q1的總損耗最大。

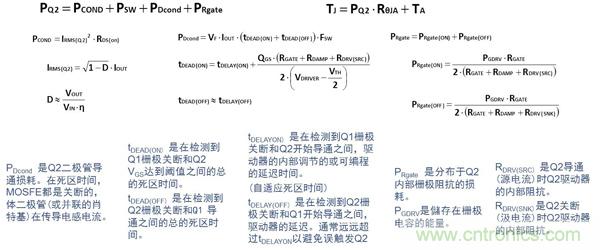

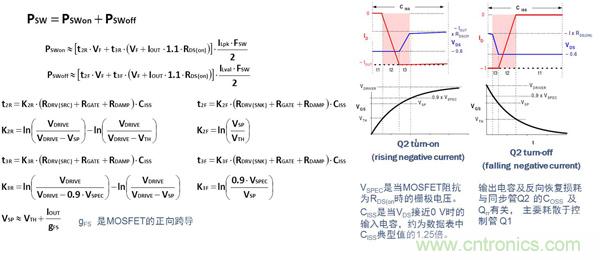

2). 同步管Q2的損耗計算

Q2工作在零電壓開關(guān)(ZVS)條件下,當(dāng)Fsw<1.5 MHz時通常以導(dǎo)通損耗為主。在選擇Q2時,建議選用:

具有低FOM(低Rds_on x Qgs)的MOSFET,以降低Q2的總損耗

低Qgd/Qgs 比率(<1)以防止快速dv/dt引起 Q1、Q2的直通現(xiàn)象

對于高頻應(yīng)用,選用集成肖特基體二極管的MOSFET,以降低反向恢復(fù)損耗以及二極管導(dǎo)通損耗

Q2的損耗計算公式如下:

Q2的導(dǎo)通損耗PCOND隨VIN升高而增加,開關(guān)損耗PSW只是隨著VIN升高而略微增加。而Q2的寄生二極管導(dǎo)通損耗PDcond和柵極驅(qū)動損耗PRgate都與VIN無關(guān)。因此,當(dāng)VIN為最大時,Q2損耗最大。

綜上所述,當(dāng)VIN為最大或最小時,Q1 + Q2總的損耗最大。進行計算時,必須同時考慮Q1和Q2的相互影響。

設(shè)計示例

以下通過一個設(shè)計示例, 演示如何完成控制管Q1和同步管Q2的 優(yōu)化選擇。如果要設(shè)計一個輸出為5 V、10 A的同步降壓穩(wěn)壓器,其輸入電壓VIN=8---16V,工作頻率FSW= 350kHz??紤]到20%的安全裕量及開關(guān)節(jié)點的電壓振蕩,可初步選擇額定電壓30 V以上、額定電流IDCONT 額定值≥ 10.3 A的MOSFET。然后,根據(jù)具體的應(yīng)用要求,確定MOSFET的封裝要求。為簡化演示,我們選擇采用5x6 mm PQFN (Power 56) 封裝的器件。綜合以上選擇條件,安森美半導(dǎo)體的產(chǎn)品陣容中有超過150個器件供選擇,我們需再進一步從中挑選出合適的Q1和Q2。同樣為簡化演示,我們將列出用于Q1和Q2的各12個器件。

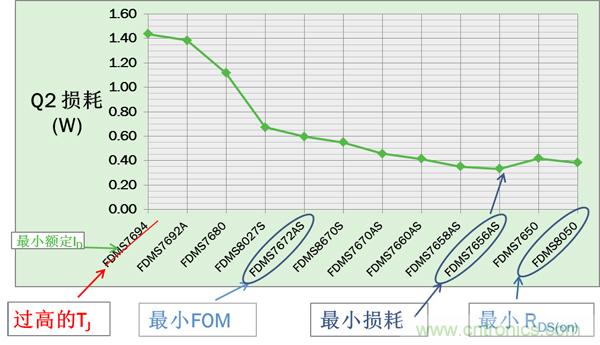

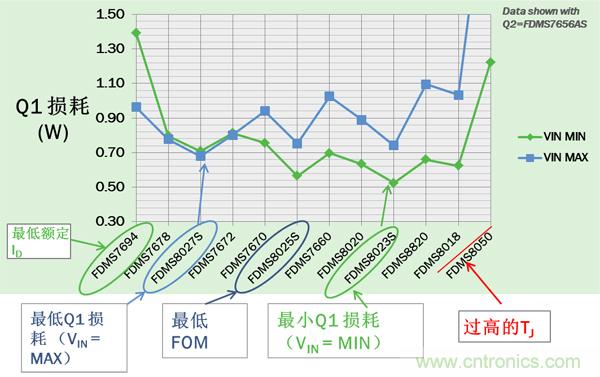

對于Q2,VIN= VINMAX時損耗最大。圖3所示的12個器件中,F(xiàn)DMS7656AS有最低的最大損耗。但由于Q2 寄生參數(shù)會影響Q1的 開關(guān)損耗, 最小Q2 損耗通常并不意味著最佳的總能效。必須比較Q1及Q2的總功耗來找到最佳的Q2以實現(xiàn)最高能效。

圖3:Q2的損耗對比

對于Q1,VIN= VINMAX或VINMIN時損耗最大。圖4所示的12個器件中,F(xiàn)DMS8027S和FDMS8023S分別在VIN= VINMAX和VINMIN時有最低的最大損耗的Q1。

圖4:Q1的損耗對比

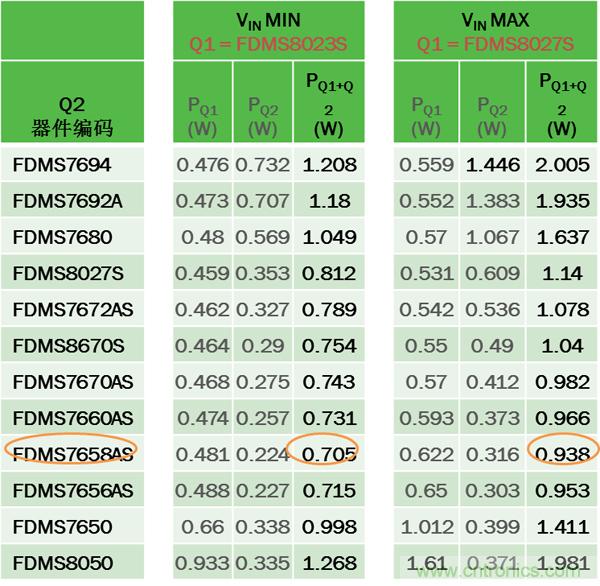

為優(yōu)化轉(zhuǎn)換器能效,首先根據(jù)VIN選擇損耗最小的Q1,然后選擇產(chǎn)生損耗最小的Q2。本例中, 無論VIN最小或最大,最佳的Q2是相同的,都為FDMS7658AS(但并不總是如此,特別是具有寬VIN范圍或高FSW時)。

圖5:優(yōu)化組合Q1和Q2

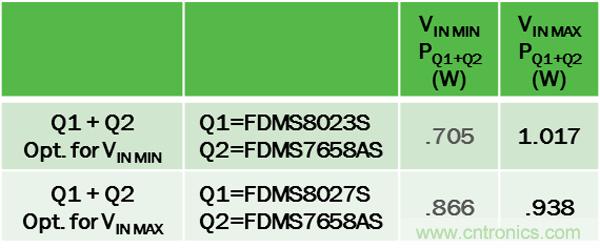

由于當(dāng)VIN=VINMAX或VINMIN,Q1 + Q2總的損耗最大,我們需對總的損耗進行對比,選擇最大損耗最低的最佳組合。如圖6所示,選用FDMS8027S為Q1,F(xiàn)DMS7658AS為Q2時,Q1+Q2的最大損耗最低。

圖6:Q1和Q2總的損耗對比

快速設(shè)計高效可靠的同步降壓穩(wěn)壓器的工具:Power Supply WebDesigner

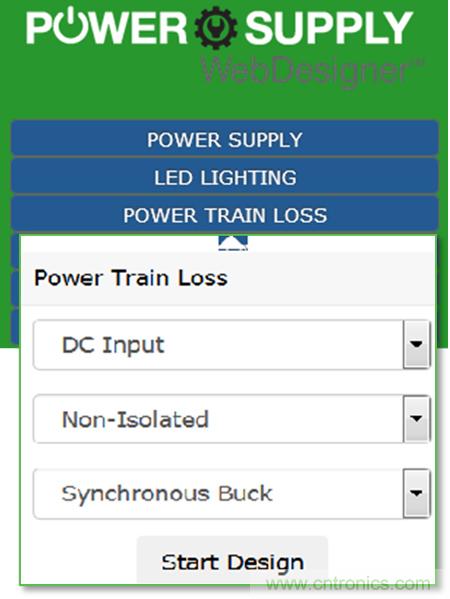

上述設(shè)計示例表明,在設(shè)計同步降壓穩(wěn)壓器時,為選擇最佳的Q1和Q2需進行大量繁瑣復(fù)雜的計算。為幫助工程師快速完成高效可靠的設(shè)計,安森美半導(dǎo)體提供了強大的在線設(shè)計平臺Power Supply WebDesigner ,加速FET優(yōu)化。

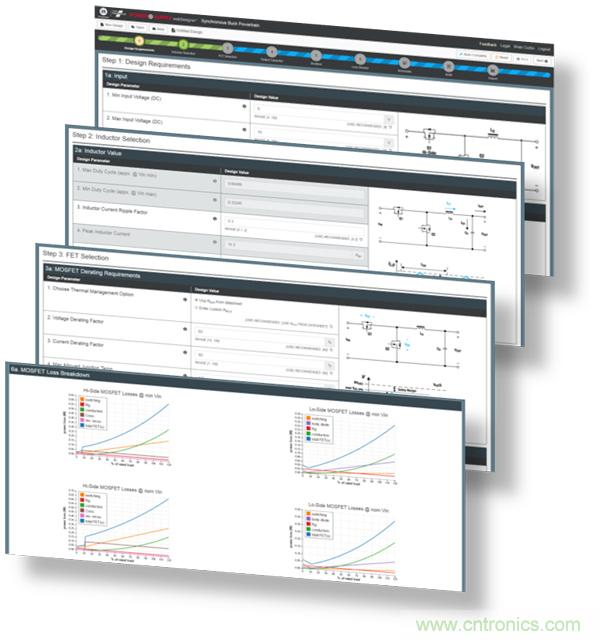

圖7:Power Supply WebDesigner 在線設(shè)計平臺

通過Power Supply WebDesigner里的SynchronousBuck功率回路損耗分析工具Power Train Loss,工程師可輕松對比合格MOSFET器件的數(shù)據(jù)及性能,自動排除超過TJ 限制的器件,選擇設(shè)計裕量和工作溫度范圍,選擇單個或雙重封裝的MOSFET,根據(jù)額定電壓、電流或封裝篩選器件,添加并聯(lián)器件和柵極阻尼電阻, 立即計算出不同的Q1 + Q2 組合的損耗,。在完成選定Q1和Q2后,工程師可獲得輸入電壓笵圍和負載笵圍內(nèi)功率回路的各類損耗和能效曲線,并根據(jù)各類曲線和功率回路能效匯總表針對不同的設(shè)計進行完整的分析、比較 (圖8]。最后,Power Supply WebDesigner可提供PNG格式的電路原理圖、Excel格式的器件清單、完整的PDF設(shè)計報告,工程師可在線保存,便于以后參考或修改。

圖8:SynchronousBuck功率回路損耗分析工具應(yīng)用

總結(jié)

為滿足行業(yè)高能效、高可靠性和高功率密度的設(shè)計趨勢,在進行同步降壓穩(wěn)壓器的設(shè)計時,需從動態(tài)性能、能效設(shè)計等方面綜合考慮。通過仔細調(diào)整元器件值,能夠相對容易地實現(xiàn)優(yōu)化的動態(tài)性能,但處理和優(yōu)化MOSFET功耗的技術(shù)通常較為繁瑣復(fù)雜。安森美半導(dǎo)體的Power Supply WebDesigner可幫助簡化設(shè)計流程,加速MOSFET優(yōu)化選擇。