【導讀】信號完整性的定義 定義:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質(zhì)量。 差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同 引起的。當電路中信號能以要求的時序、持續(xù)時間和電壓幅度到達接收端時,該電路就有很好的信號完整性。當信號不能正常響應時,就出現(xiàn)了信號完整性問題。

信號完整性包含:

1、波形完整性(Waveform integrity)

2、時序完整性(Timing integrity)

3、電源完整性(Power integrity)

信號完整性分析的目的就是用最小的成本,最快的時間使產(chǎn)品達到波形完 整性、時序完整性、電源完整性的要求。

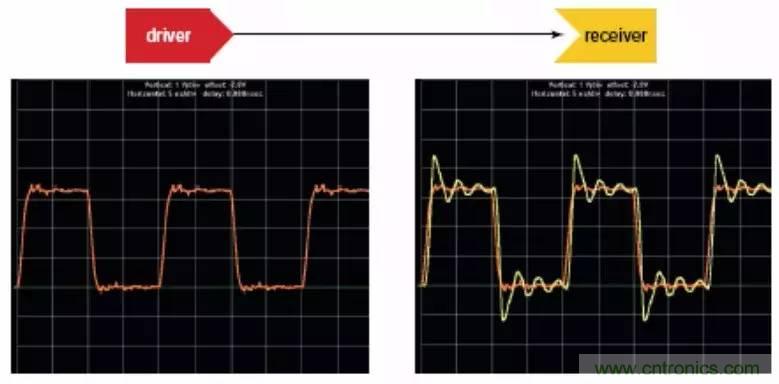

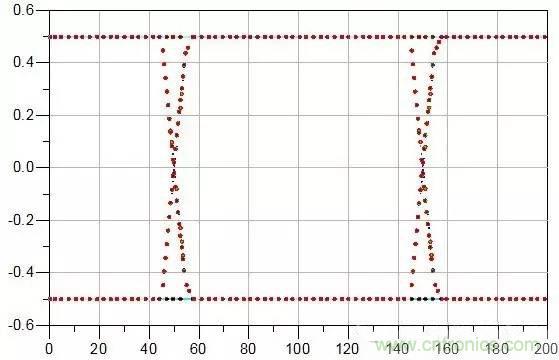

我們知道:電源不穩(wěn)定、電源的干擾、信號間的串擾、信號傳輸過程中的反射,這些都會讓信號產(chǎn)生畸變,看下面這張圖,你就會知道理想的信號,經(jīng)過:反射、串擾、抖動,最后變成什么鬼。

典型的信號完整性問題:反射、串擾、電源/ 地噪聲、時序等。

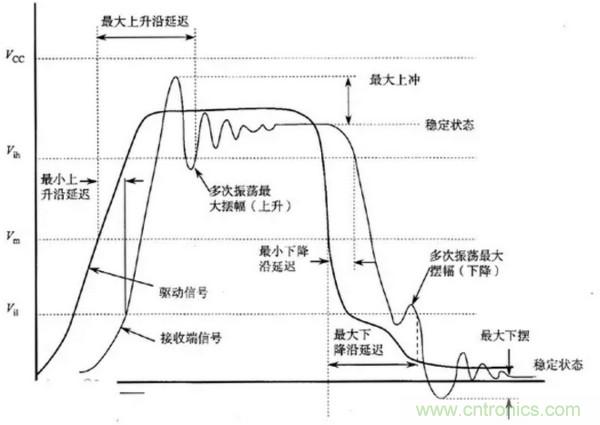

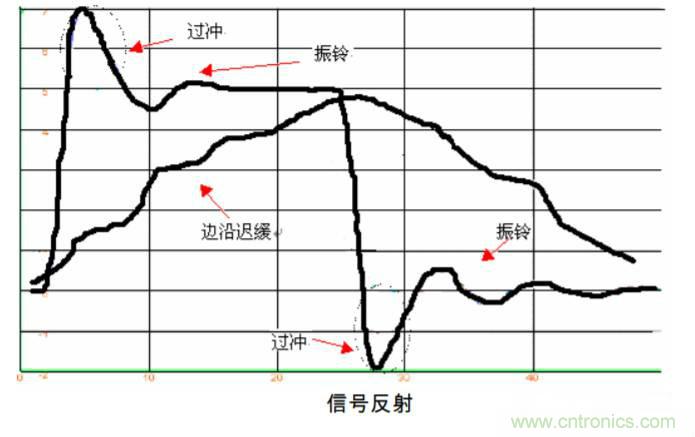

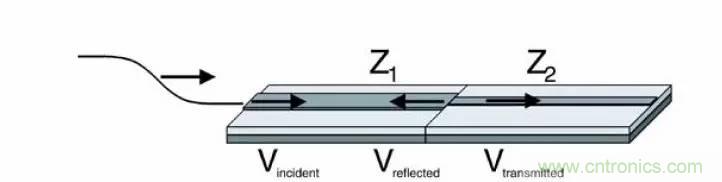

反射

由于傳輸系統(tǒng)阻抗不匹配,會使傳輸?shù)男盘柌?能被完全吸收,造成部分能量返回。反射造成信號出現(xiàn)過沖(Overshoot)、振鈴(Ringing)、邊沿遲 緩(階梯電壓波)。過沖是振鈴的欠阻尼狀態(tài),邊沿遲緩是振鈴的過阻尼狀態(tài)。下圖為信號反射的三種表現(xiàn)形式。

過沖一方面會造成強烈的電磁干擾,另一方面 會損傷后面電路的輸入級,甚至失效。而振鈴會帶 來信號長時間不能穩(wěn)定,邊沿遲緩帶來信號上升時 間過長,二者都可能帶來信號的時序問題,如時鐘數(shù)據(jù)同步、建立與保持時間不滿足等。

PCB設計總有幾個阻抗沒法連續(xù)的地方,怎么辦?

PCB的阻抗控制

高速電路設計/信號完整性的一些基本概念

為什么一般傳輸線特性阻抗都希望控制為50歐姆?

為什么PCB走線中避免出現(xiàn)銳角和直角?

PCB中的平面跨分割

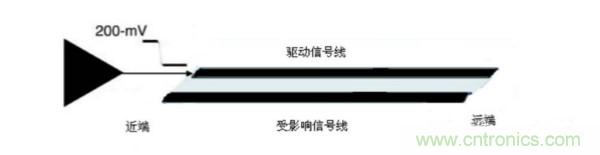

串擾 Crosstalk

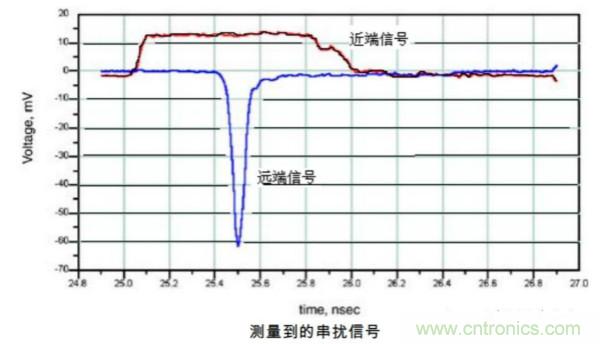

由于導線之間間距過小,當有快速變化的電流 流過導線時會產(chǎn)生交變的磁場,而使鄰近的導線上 感應出信號電壓,稱為串擾(Crosstalk)。 下圖為信號串擾試驗模型,以及受影響信號線上的串擾信號。

串擾一方面是EMC主要根源之一,另一方面, 串擾干擾正常的信號流,有可能造成數(shù)據(jù)錯誤,是造成誤碼的主要原因之一。問題發(fā)生沒有一定規(guī)律, 時隱時現(xiàn),診斷與定位往往花費大量時間與精力。

串擾和反射能讓信號多不完整?

互感--連接器如何引起串擾

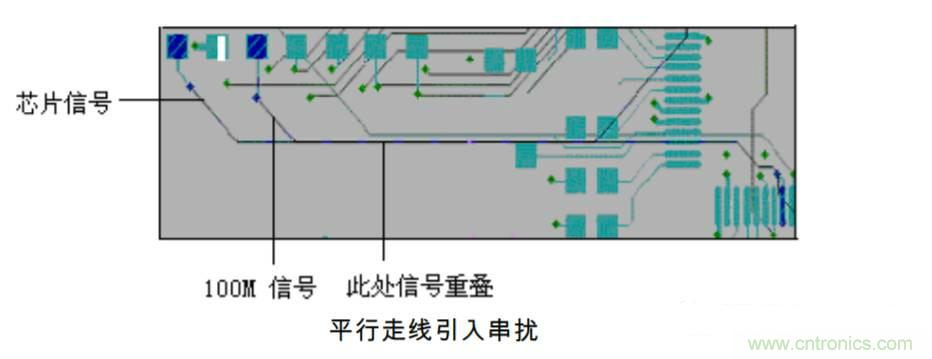

某單板經(jīng)常發(fā)現(xiàn)工作一段時間后,網(wǎng)口工作異 常,數(shù)據(jù)傳輸經(jīng)常有誤碼。詢問供應商,該現(xiàn)象一 般和某芯片的信號受到干擾有關。 檢查 PCB 發(fā)現(xiàn),在相鄰層該信號和一條 100M 信號相重疊,中間沒有地平面分隔,由此引入干擾。

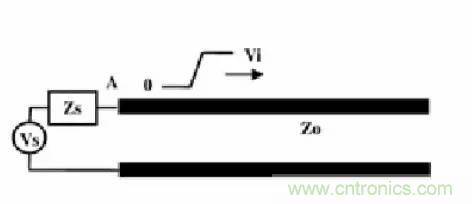

反射--初始波

當驅動器發(fā)射一個信號進入傳輸線時,信號的幅值取決于電壓、緩沖器的內(nèi)阻和傳輸線的阻抗。驅動器端看到的初始電壓決定于內(nèi)阻和線阻抗的分壓。

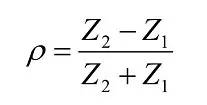

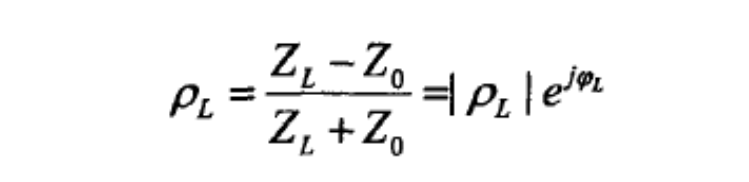

反射系數(shù)

其中-1≤ρ≤1

當ρ=0時無反射發(fā)生

當ρ=1(Z 2 =∞,開路)時發(fā)生全正反射

當ρ=-1(Z 2 =0,短路)時發(fā)生全負反射

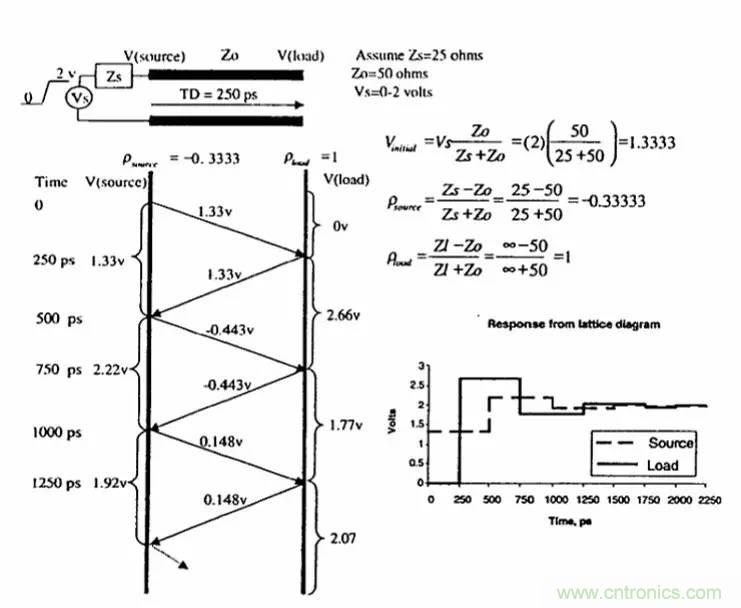

初始電壓,是源電壓Vs(2V)經(jīng)過Zs(25歐姆)和傳輸線阻抗(50歐姆)分壓。

Vinitial=1.33V

后續(xù)的反射率按照反射系數(shù)公式進行計算

源端的反射率,是根據(jù)源端阻抗(25歐姆)和傳輸線阻抗(50歐姆)根據(jù)反射系數(shù)公式計算為-0.33;

終端的反射率,是根據(jù)終端阻抗(無窮大)和傳輸線阻抗(50歐姆)根據(jù)反射系數(shù)公式計算為1;

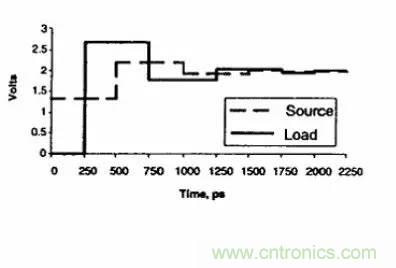

我們按照每次反射的幅度和延時,在最初的脈沖波形上進行疊加就得到了這個波形,這也就是為什么,阻抗不匹配造成信號完整性不好的原因。

由于連接的存在、器件管腳、走線寬度變化、走線拐彎、過孔會使得阻抗不得不變化。所以反射也就不可避免。

串擾

電壓后者電流有變化,自然就會往外輻射電磁波

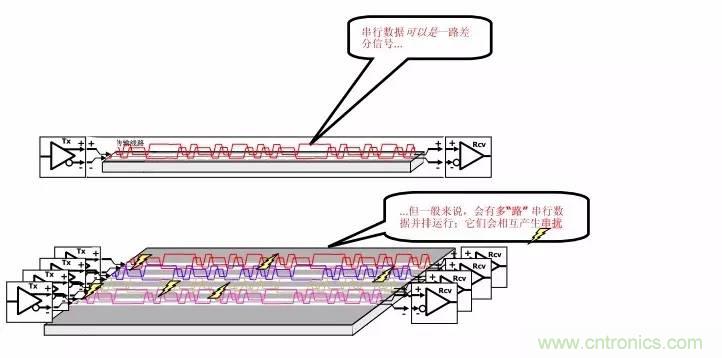

串擾是指當信號在傳輸線上傳播時,因電磁耦合對相鄰的傳輸線產(chǎn)生的不期望的電壓噪聲。

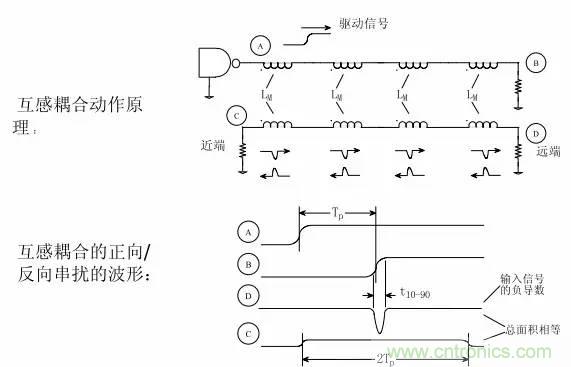

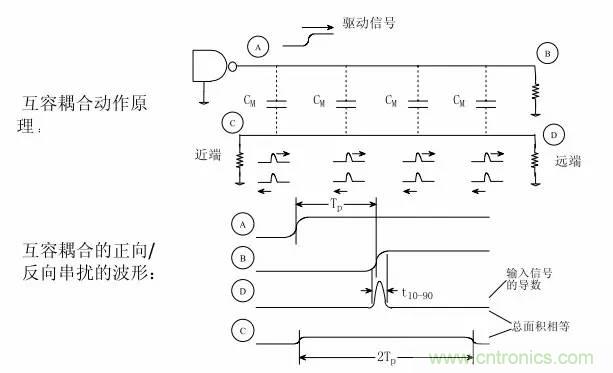

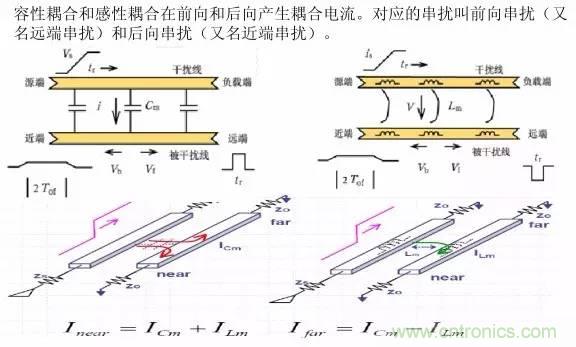

串擾是由電磁耦合引起的,耦合分為容性耦合和感性耦合兩種。

容性耦合是由于干擾源(Aggressor)上的電壓變化在被干擾對象(Victim)上引起感應電流從而導致的電磁干擾;

而感性耦合則是由于干擾源上的電流變化產(chǎn)生的磁場在被干擾對象上引起感應電壓從而導致的電磁干擾。因此,信號通過一導體時會在相鄰的導體上引起兩類不同的噪聲信號:容性耦合信號和感性耦合信號。

感性耦合:

容性耦合:

電源完整性

電源完整性(Power integrity)簡稱PI,是確認電源來源及目的端的電壓及電流是否符合需求。

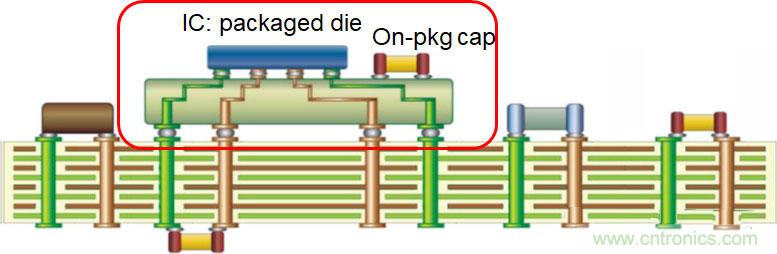

電源完整性在現(xiàn)今的電子產(chǎn)品中相當重要。有幾個有關電源完整性的層面:芯片層面、芯片封裝層面、電路板層面及系統(tǒng)層面。在電路板層面的電源完整性要達到以下三個需求:

1、使芯片引腳的電壓噪聲+電壓紋波比規(guī)格要求要小一些(例如芯片電源管腳的輸入電壓要求1V之間的誤差小于+/-50 mV)

2、控制接地反彈(地彈)(同步切換噪聲SSN、同步切換輸出SSO)

3、降低電磁干擾(EMI)并且維持電磁兼容性(EMC):電源分布網(wǎng)絡(PDN)是電路板上最大型的導體,因此也是最容易發(fā)射及接收噪聲的天線。

名詞解釋:

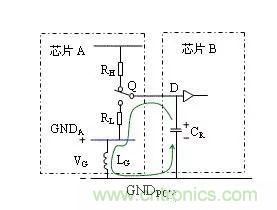

a、“地彈”,是指芯片內(nèi)部“地”電平相對于電路板“地”電平的變化現(xiàn)象。以電路板“地”為參考,就像是芯片內(nèi)部的“地”電平不斷的跳動,因此形象的稱之為地彈(ground bounce)。

當器件輸出端由一個狀態(tài)跳變到另一個狀態(tài)時,地彈現(xiàn)象會導致器件邏輯輸入端產(chǎn)生毛刺。對于任何形式封裝的芯片,其引腳必會存在電感電容等寄生參數(shù),而地彈主要是由于GND引腳上的阻抗引起的。 集成電路的規(guī)模越來越大,開關速度不斷提高,地彈噪聲如果控制不好就會影響電路的功能,因此有必要深入理解地彈的概念并研究它的規(guī)律。

我們可以用下圖來直觀的解釋一下。圖中開關Q的不同位置代表了輸出的“0”“1”兩種狀態(tài)。假定由于電路狀態(tài)裝換,開關Q接通RL低電平,負載電容對地放電,隨著負載電容電壓下降,它積累的電荷流向地,在接地回路上形成一個大的電流浪涌。隨著放電電流建立然后衰減,這一電流變化作用于接地引腳的電感LG,這樣在芯片外的電路板“地”與芯片內(nèi)的地之間,會形成一定的電壓差,如圖中VG。這種由于輸出轉換引起的芯片內(nèi)部參考地電位漂移就是地彈。

芯片A的輸出變化,產(chǎn)生地彈。這對芯片A的輸入邏輯是有影響的。接收邏輯把輸入電壓和芯片內(nèi)部的地電壓差分比較確定輸入,因此從接收邏輯來看就象輸入信號本身疊加了一個與地彈噪聲相同的噪聲。

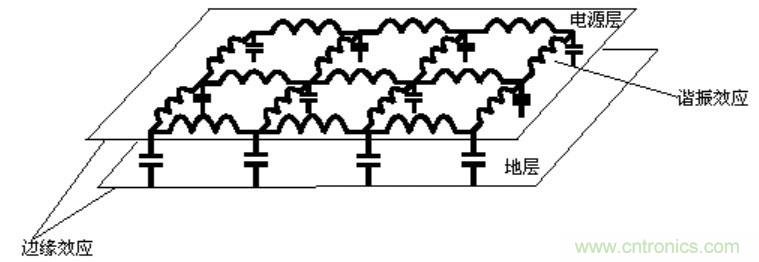

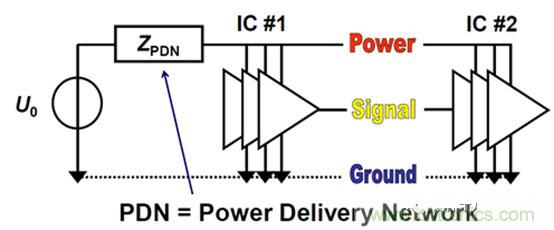

b、PDN

電路板設計中,都有電源分配網(wǎng)絡系統(tǒng)。電源分配網(wǎng)絡系統(tǒng)的作用就是給系統(tǒng)內(nèi)所有器件或芯片提供足夠的電源,并滿足系統(tǒng)對電源穩(wěn)定性的要求。

我們看到電源、GND網(wǎng)絡,其實分布著阻抗。

電源噪聲余量計算:

1、芯片的datasheet會給一個規(guī)范值,通常是5%;要考慮到穩(wěn)壓芯片直流輸出誤差,一般是+/_2.5%,因此電源噪聲峰值幅度不超過+/_2.5%。

2、如芯片的工作電壓范圍是3.13~3.47,穩(wěn)壓芯片標出輸出電壓是3.3V,安裝在電路板后的輸出電壓是3.36V。容許的電壓的變化范圍是3.47-3.36=110mv。穩(wěn)壓芯片輸出精度是+/_1%,及3.36* +/_1%=+/_33.6mv。電源噪聲余量為110-33.6=76.4mv。

計算電源噪聲要注意五點

(1)穩(wěn)壓芯片的輸出的精確值是多少。

(2)工作環(huán)境的是否是穩(wěn)壓芯片所推薦的環(huán)境。

(3)負載情況是怎么樣,這對穩(wěn)壓芯片輸出也有影響。

(4)電源噪聲最終會影響到信號質(zhì)量。而信號上的噪聲來源不僅僅是電源噪聲,反射竄擾等信號完整性問題也會在信號上疊加,因此不能把所有噪聲余量留給電源系統(tǒng)。

(5)不同的電壓等級對電源噪聲要求也不樣,電壓越小噪聲余量越小。模擬電路對電源要求更高。

電源噪聲來源

(1)穩(wěn)壓芯片輸出的電壓不是恒定的,會有一定的紋波。

(2)穩(wěn)壓電源無法實時響應負載對于電流需求的快速變化。穩(wěn)壓電源響應的頻率一般在200Khz以內(nèi),能做正確的響應,超過了這個頻率則在電源的輸出短引腳處出現(xiàn)電壓跌落。

(3)負載瞬態(tài)電流在電源路徑阻抗和地路徑阻抗產(chǎn)生的壓降。

(4)外部的干擾。

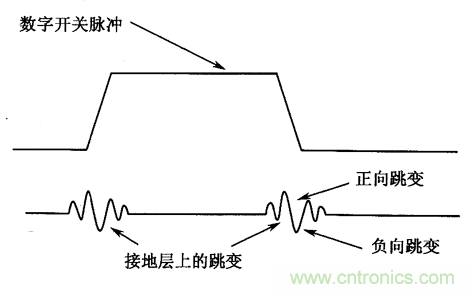

電源/地噪聲

當信號狀態(tài)快速改變時,在電源和地上會產(chǎn)生 紋波電流。由于電源和地上的電感的存在,信號突 變產(chǎn)生的尖峰電流將使電源和地上出現(xiàn)電壓的波 動。系統(tǒng)幾十甚至上百個信號同時發(fā)生狀態(tài)改變時, 有可能造成系統(tǒng)的誤動作。由于電源/地噪聲的復雜 性,有時單獨作為電源完整性(Power Integrity)來 研究。

歷史參考文檔:

電源完整性與地彈噪聲的高速PCB仿真

電源完整性測量對象和測量內(nèi)容

電源完整性設計

電源完整性設計2

電源完整性設計3

高速數(shù)字電路“接地”要點

電源完整性——理解與設計

時序問題

系統(tǒng)中數(shù)據(jù)的提取通常是由時鐘信號的上升沿 或下降沿觸發(fā),按照一定的節(jié)拍進行,數(shù)據(jù)應該及 時到達接收端并進入穩(wěn)態(tài)。數(shù)據(jù)的超時延時和數(shù)據(jù) 的信號畸變都會造成數(shù)據(jù)的讀取錯誤。接收端信號 由于出現(xiàn)嚴重的振鈴現(xiàn)象,部分進入非穩(wěn)定狀態(tài), 會使數(shù)據(jù)不能被可靠地提取,造成誤碼問題。

時序分析基本概念

傳輸時間:傳輸時間是指信號在傳輸線上的傳播延時,與線長和信號傳播速度有關。通常我們認為信號在傳輸線的傳輸速度為6000mil/ns,可以根據(jù)信號傳輸線的長度得出傳輸時間。

飛行時間(Flight Time):指信號從驅動端傳輸?shù)浇邮斩?,并達到一定的電平之間的延時,和傳輸延遲和上升時間有關。

Tco:Tco是指器件的輸入時鐘邊緣觸發(fā)有效到輸出信號有效的時間差,這是信號在器件內(nèi)部的所有延遲總和。

建立時間:指的是接收端能夠正確地鎖存數(shù)據(jù),在時鐘邊沿來導之前應該保持穩(wěn)定的最小時間,它表示數(shù)據(jù)有效必須先于時鐘有效的最小時間。

保持時間:為了成功的鎖存一個信號到接收端,器件必須要求數(shù)據(jù)信號在被時鐘沿觸發(fā)后繼續(xù)保持一段時間,以確保數(shù)據(jù)被正確的操作。這個最小的時間就是我們說的保持時間。

時鐘抖動(Jitter):時鐘抖動是指時鐘觸發(fā)沿的隨機誤差,時鐘抖動通常指時鐘周期在周期與周期之間的變化。這個誤差是由時鐘發(fā)生器內(nèi)部產(chǎn)生的,和后期布線沒有關系。

時鐘偏移(Skew):是指由同樣的時鐘產(chǎn)生的多個子時鐘信號之間的延時差異。

采樣窗口:指我們通過示波器觀察到的信號的波形。

同步時鐘系統(tǒng) 時序設計——DDR為例

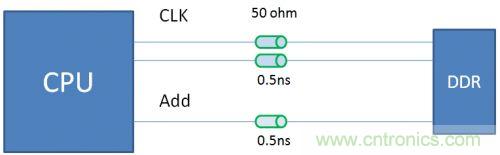

DDR布線在PCB設計中占有舉足輕重的地位,設計成功的關鍵就是要保證系統(tǒng)有充足的時序裕量。要保證系統(tǒng)的時序,線長匹配又是一個重要的環(huán)節(jié)。我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制/命令信號與時鐘做等長。數(shù)據(jù)信號與DQS做等長。為啥要做等長?大家會說是要讓同組信號同時到達接收端,好讓接收芯片能夠同時處理這些信號。那么,時鐘信號和地址同時到達接收端,波形的對應關系是什么樣的呢?我們通過仿真來看一下具體波形。

建立如下通道,分別模擬DDR3的地址信號與時鐘信號。

圖1 地址/時鐘仿真示意圖

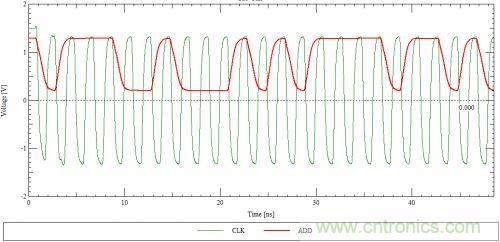

為方便計算,我們假設DDR的時鐘頻率為500MHz,這樣對應的地址信號的速率就應該是500Mbps,這里大家應該明白,雖然DDR是雙倍速率,但對于地址/控制信號來說,依然是單倍速率的。下面來看看波形,在地址與時鐘完全等長的情況下,地址與數(shù)據(jù)端的接收波形如下圖2,紅色代表地址信號,綠色代表時鐘信號。

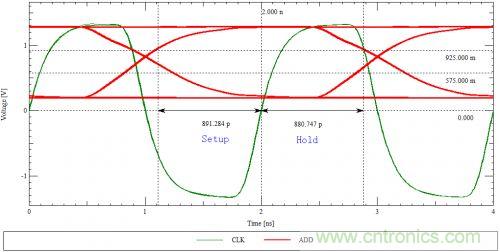

圖2 時鐘信號與地址信號波形

上面的波形我們似乎看不出時鐘與地址之間的時序關系是什么樣的,我們把它放在一個眼圖中,時序關系就很明確了。這里粗略的計算下建立時間與保持時間。如下圖

圖3 時鐘信號與地址信號波形

由上圖3.我們可以知道,該地址信號的建立時間大約為891ps,保持時間為881ps。這是在時鐘與地址信號完全等長情況下的波形。如果地址與時鐘不等長,信號又是什么樣的呢?仿真中,我們讓地址線比時鐘線慢200ps,得到的與眼圖如下:

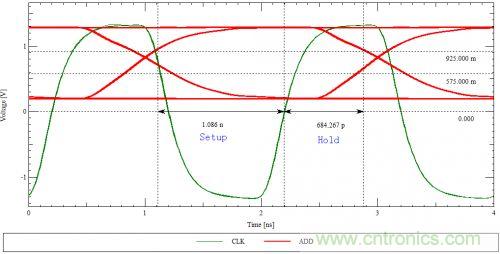

圖4 時鐘信號與地址信號波形

由上圖可知,在地址信號比時鐘信號長的情況下,保持時間為684ps,建立越為1.1ns。可見,相對于地址線與時鐘線等長來說,地址線比時鐘線長會使地址信號的建立時間更短。同理,如果時鐘線比地址線長,則建立時間會變長,而保持時間會變短。那么雙倍速率的數(shù)據(jù)信號又是怎樣的?下面通過具體的仿真實例來看一下。

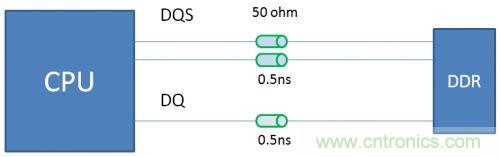

圖5 DQ 與 DQS仿真示意

仿真通道如上圖所示,驅動端和接收端為某芯片公司的IBIS模型,仿真波形如下:

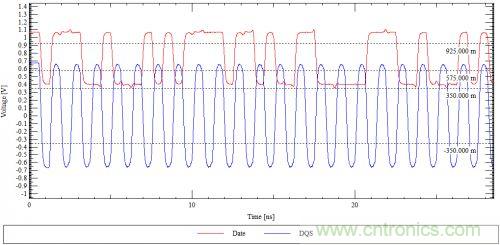

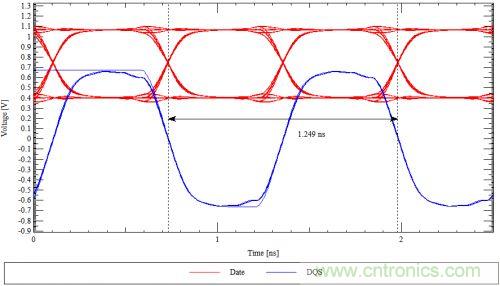

圖6 DQ與DQS仿真波形

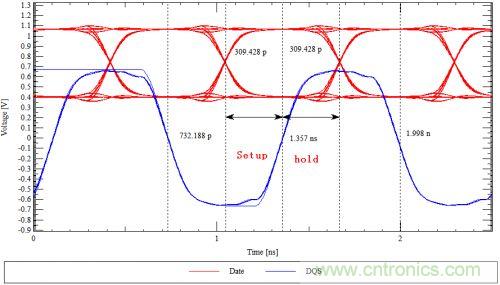

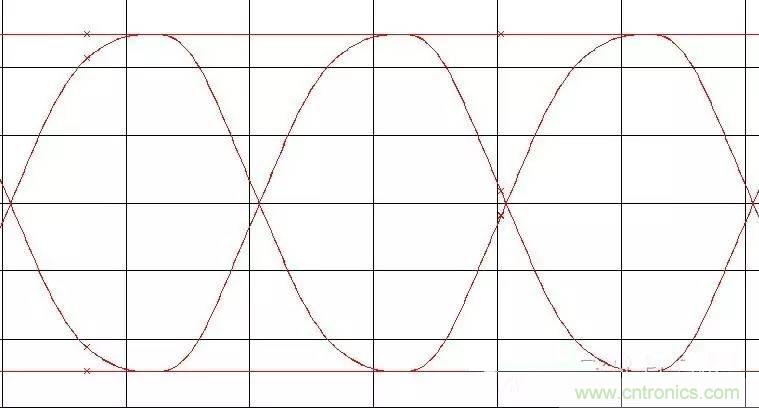

我們將DQS和DQ信號同時生成眼圖,在一個窗口下觀測,結果如下:

圖7 DQ與DQS眼圖

如上圖所示,大家可能發(fā)現(xiàn)了,如果按照原始對應關系,數(shù)據(jù)信號的邊沿和時鐘信號的邊沿是對齊的,如果是這樣,時鐘信號怎樣完成對數(shù)據(jù)信號的采樣呢?實際上并不是這樣的。以上仿真只是簡單的將兩波形放在了一起,因為DQ和DQS的傳輸通道長度是一樣的,所以他們的邊沿是對齊的。實際工作的時候,主控芯片會有一個調(diào)節(jié)機制。一般數(shù)據(jù)信號會比DQS提前四分之一周期被釋放出來,實際上,在顆粒端接收到的波形對應關系應該是這樣的:

圖8 平移后的眼圖

通過主控芯片的調(diào)節(jié)之后,DQS的邊沿就和DQ信號位的中心對齊了,這樣就能保證數(shù)據(jù)在傳輸?shù)浇邮斩擞凶銐虻慕r間與保持時間。和上面分析時鐘與地址信號一樣,如果DQ與DQS之間等長做的不好,DQS的時鐘邊沿就不會保持在DQ的中間位置,這樣建立時間或者保持時間的裕量就會變小。先簡單的來看一張圖

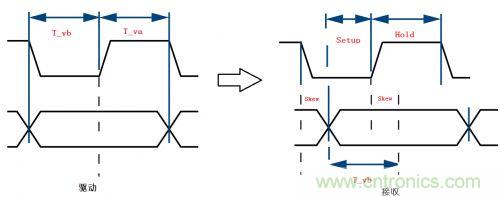

圖9 延時偏差對時序的影響

上圖中,T_vb與T_va表示的是主控芯片在輸出數(shù)據(jù)時時鐘與數(shù)據(jù)之間的時序參數(shù)。在理想情況下,時鐘邊沿和數(shù)據(jù)電平的中心是對齊的,由于時鐘和數(shù)據(jù)傳輸通道不等長,使得時鐘邊沿沒有和數(shù)據(jù)脈沖的中間位置對其,使得建立時間的裕量變小。在理解了這些基礎問題之后,我們需要做的就是將這些時間參數(shù)轉化為線長。

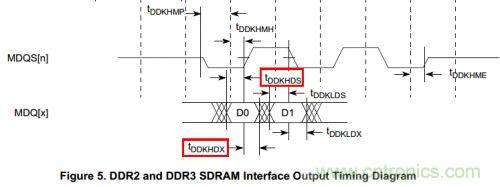

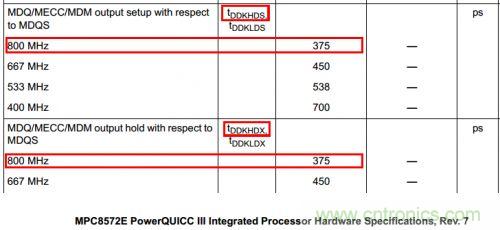

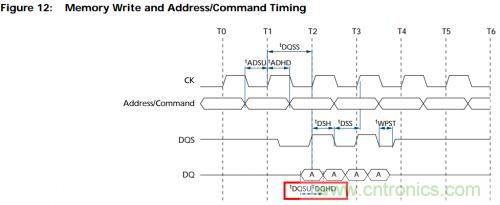

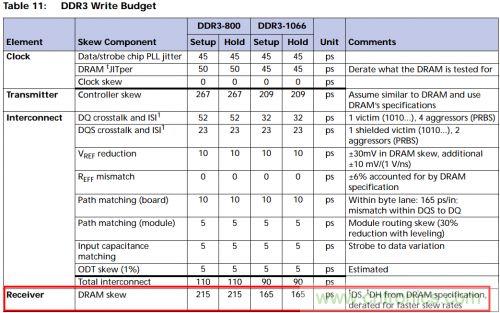

下面我們通過具體實例來看看時序的計算,下圖是Freescale MPC8572 DDR主控芯片手冊,這張圖片定義了從芯片出來的時候,DQS與DQ之間的相位關系。

圖10 MPC8572時序圖

圖11 MPC8572時序參數(shù)

顆粒端為美光DDR,該芯片的時序圖以及時序參數(shù)如下圖所示,這張圖片則定義了顆粒端芯片識別信號所需要的建立時間與保持時間。

圖12 DDR顆粒時序圖以及時序參數(shù)

我們用T_pcbskew來表示DQ與DQS之間的延時偏差,如果想要得到足夠的時序裕量,則延時偏差要滿足以下關系:

T_pcbskew《T_vb-T_setup

T_pcbskew》T_hold-T_va

代入數(shù)據(jù),有:

T_vb-T_setup=375-215=160ps

T_hold-T_va=-160ps

這樣,如果傳輸線的速度按照6mil/ps來計算,T_pcbskew為+/-960mil。大家會發(fā)現(xiàn)裕量很大,當然這只是最理想情況,沒有考慮時鐘抖動以及數(shù)據(jù)信號的抖動,以及串擾、碼間干擾帶來的影響,如果把這些因素都考慮進來,留給我們布線偏差的裕量就比較小了。

綜上所述,時序控制的目的就是要保證數(shù)據(jù)在接收端有充足的建立時間與保持時間

眼圖

眼圖(EYE Diagram)介紹

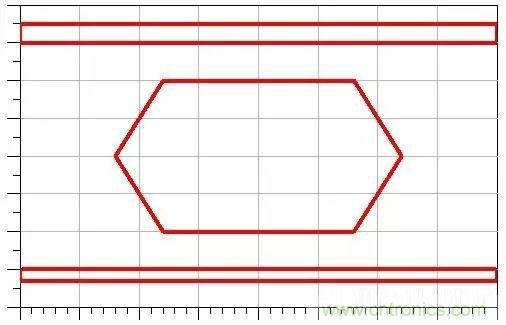

所謂眼圖簡單的說就是把一連串接收端接收到的脈沖信號(000,001,010,011, 100, 101,110,111)同時疊加在高速示波器上以形成眼圖,如下圖所示:

圖1

若在眼圖中加入一個多邊形以標識信號真正存在的區(qū)域,即所謂的眼圖模板測試(Eye Mask)。因為眼圖模板測試可在一次量測中,計算出測試信號波形的上升時間、下降時間、噪聲與抖動(Jitter)等,形成一套系統(tǒng)化的測量方法,因此眼圖已被多個協(xié)會(SATA, SAS, PCIE, USB, Ethernet等幾乎所有的高速總線協(xié)會)采用來規(guī)范各種通信互連系統(tǒng)的標準測試項目。

圖 2

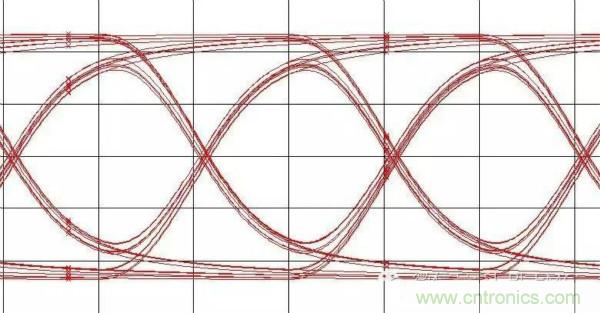

眼圖的特性是累加了一連串的脈沖時序,因此它具有測量信號重復性的作用。圖1的眼圖可以呈現(xiàn)許多信息;假如整個互連通信系統(tǒng)無任何噪聲時,眼圖上的軌跡應為同一條直線。當噪聲越大時,信號變動程度也越大,在垂直方向之疊合軌跡也越粗,誤碼率也將增加。如下圖所示:

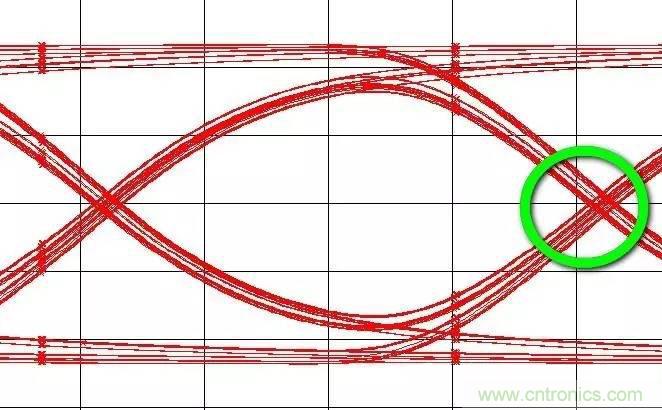

圖3

眼圖的水平方向為時間軸,代表信號到達的時間,抖動將造成水平方向上軌跡變粗。眼圖的左右邊沿可以測量出信號的上升時間和下降時間。眼圖形狀類似于眼睛,當眼睛張的越大時,傳輸質(zhì)量越佳?;旧先粞蹐D的形狀呈現(xiàn)【瞇瞇眼】形狀時,表示信號質(zhì)量極非常差。如下圖所示:

圖4

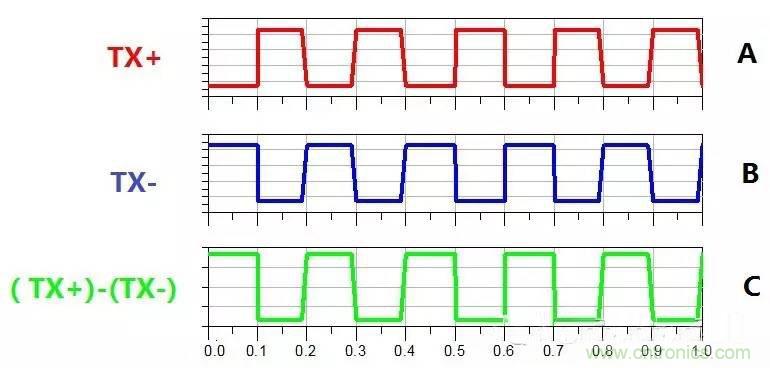

在信號量測中,眼圖的形成正如上所述:由多個差分信號運算所累加而成。以SATA為例,其原理大致如下:

首先SATA 的信號pin角,大致上可分為TX+、TX-、RX+與RX-;由于SATA、SAS、PCI Express這類總線都是以差分信號來取代傳統(tǒng)的單端信號傳輸,TX 為發(fā)送端,RX為接收端,而+、-則為差分的成對信號。參考圖5(A)與圖5(B)的信號波形圖(以TX 為例),當信號傳遞時,即使因外界的噪聲干擾,也不用擔心信號會有誤判的情形發(fā)生,因為差分信號的傳輸機制會將TX+與TX-作相減的運算,如圖5(C)所示,如果有噪聲,也不會傳遞到芯片內(nèi)部,這樣就不會影響到正常的信號傳遞,從而提高噪聲容忍度。

圖5

而示波器在測量眼圖信號時,透過自觸發(fā)點之后,將TX+ - TX-的信號累加至示波器上,如下圖所示,即獲得了眼圖。

圖 6

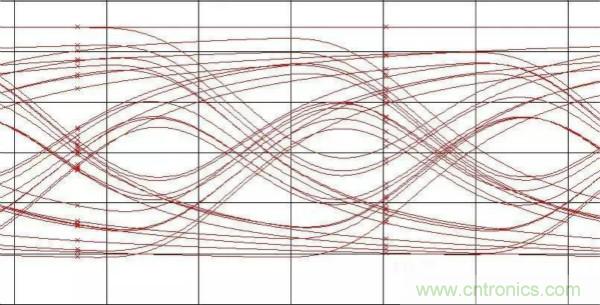

很多人在稱贊美女的時候,經(jīng)常會用【明眸皓齒】、【蜂腰美人】或【水蛇腰】來形容。其實在評判眼圖的質(zhì)量時,這個標準也蠻適用的。這其實就可以當作檢查眼圖是否完美的兩個重要準則:

■【明眸皓齒】:眼睛要大,如果配合上有眼圖模板的話,那么以眼圖模板當作瞳孔,則眼白(Margin)就必須要夠多。

■【蜂腰美人】:如圖7紅綠色圓圈中交叉的部分,必須要越小越好,最好是一個點,就像蜂腰美人一樣,比較瘦小,因為這里代表的是抖動,如果太大就會造成誤碼率增加。抖動越小則代表信號質(zhì)量越好,發(fā)生誤碼的機率越低。

圖 7

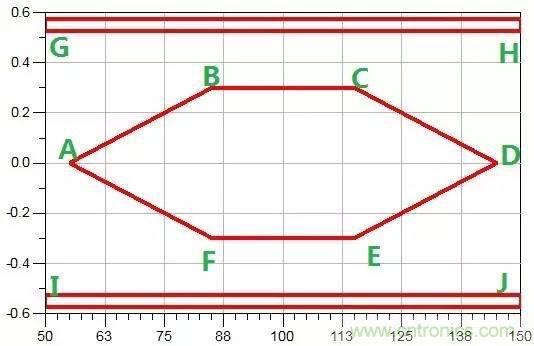

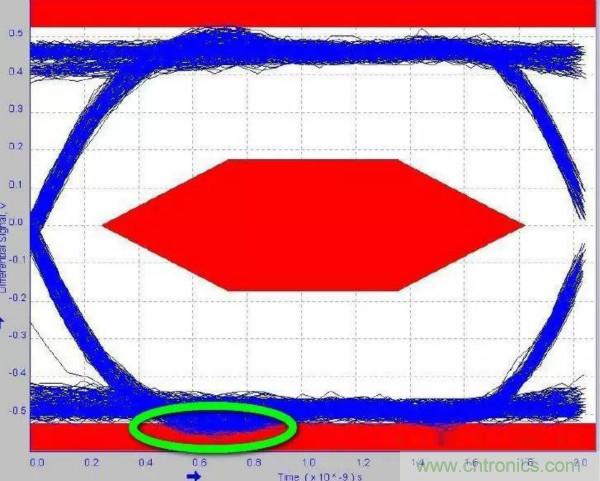

前面講到了眼圖模板,眼圖的測試主要是用來檢測高速串行傳輸?shù)男盘栙|(zhì)量,不論是SATA、PCI Express還是USB,標準都有提供眼圖模板的標準給工程師作為眼圖的測量準則。如圖8所示,是USB2.0 TX的眼圖模板,所謂的眼圖模板主要是用在判斷眼圖是否符合規(guī)范的要求,圖8中ABCDEF6點所圍成的六邊形紅色區(qū)域以及GH以上、IJ一下區(qū)域代表所謂的【禁止區(qū)域】,如果眼圖有任何信號波形位進入這些紅色區(qū)域,則表示信號傳輸不滿足協(xié)議規(guī)范的要求(如圖9綠色圓圈處)。

圖 8

圖 9

眼圖的判斷

以上說了那么多,現(xiàn)在就來看看眼圖到底如何來判斷。

首先,看是否【明眸】。眼圖是否夠大?是否有進入內(nèi)模板?是否有超過上下限。

其次,看是都【蜂腰】。眼圖交叉點的部分,是否達到夠細?是否達到最小協(xié)議規(guī)范中抖動的要求?

以上兩點需要同時滿足,才能說明眼圖符合設計要求。

歷史參考文檔:

薛定諤貓 與 建立保持時間

為什么會有建立時間(Setup Time)和保持時間(Hold Time)?

亞穩(wěn)態(tài)概述

亞穩(wěn)態(tài)分析

信號完整性設計方法

嚴格控制關鍵信號的 PCB 走線長度

信號完整性問題主要是 PCB 走線過長造成的。 如果在設計前期,我們能夠找出關鍵信號,并對走線長度進行控制,就可以有效地抑制信號反射,保證信號質(zhì)量。所以我們需要研究器件的數(shù)據(jù)手冊, 確定信號最快上升與下降時間,估算臨界走線長度, 對于時鐘、高速數(shù)據(jù)流信號尤其要注意長度控制。

高速信號 PCB布線技巧

三種特殊走線技巧

合理規(guī)劃走線的拓撲結構

走線的拓撲結構是指一根走線的布線順序及布 線結構,如菊花鏈和星形分布等。同時,需要采用 合適的匹配方式,如源端匹配、終端匹配等。我們 需要了解電路的設計原理,驅動順序與信號本身特 點,采用合適的拓撲與匹配方式。

高速信號走線規(guī)則

有效控制 PCB 特征阻抗

在多層線路板中,信號完整性性能良好的關鍵 是使它的特性阻抗在整條線路中保持恒定。目標是 使所有線路的特性阻抗?jié)M足一個規(guī)定值,通常在 25 歐姆和 70 歐姆之間。所以在設計時,就需要對 PCB 走線特征阻抗進行計算,確定合理的走線寬度與其 它設計參數(shù);在 PCB 加工時,表明阻抗要求;PCB 加工后,需要采用儀器對特征阻抗進行驗證。

阻抗不匹配,信號反射疊加的過程

阻抗控制的走線細節(jié)舉例

特征阻抗那點事

設計仿真技術

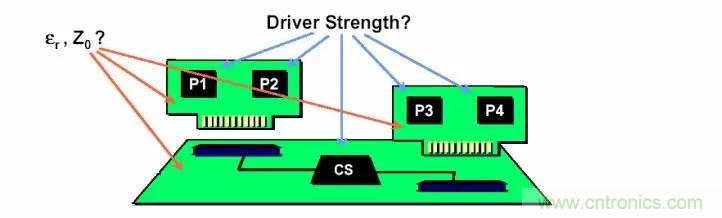

在 PCB 設計過程中,采用軟件進行仿真。在系 統(tǒng)設計時,對模塊布置進行仿真;在單板布局時, 可以進行前仿真,確定器件布局;在走線時,進行 后仿真,保證走線質(zhì)量。通過仿真,事先可以預測 到信號的設計質(zhì)量,及時調(diào)整設計策略,預先預防, 而不是事后補救。

其它可采用技術

在設計時,需要從電路設計、布局、布線、電源系統(tǒng)等方面進行考慮。如在電路設計時,合理選 擇驅動器件,盡量采用同步設計,避免異步設計, 高速信號采用差分信號,為集成電路芯片添加去耦 電容;布局時,注意數(shù)字與模擬信號分開,合理設 計單板的疊層,器件按照速度合理布局;布線時,注意少打過孔,布線遵循 3W 原則;電源設計時, 注意低阻抗連接,層疊遵循 20H 原則等。

3W原則

布局基本要領

高速信號 PCB布線技巧

推薦閱讀: