【導(dǎo)讀】網(wǎng)絡(luò)路由器帶有用于性能監(jiān)控、流量管理、網(wǎng)絡(luò)追蹤和網(wǎng)絡(luò)安全的統(tǒng)計(jì)計(jì)數(shù)器。計(jì)數(shù)器用來記錄數(shù)據(jù)包到達(dá)和離開的次數(shù)以及特定事件的次數(shù),比如當(dāng)網(wǎng)絡(luò)出現(xiàn)壞包時(shí)。數(shù)據(jù)包的到達(dá)會(huì)使多個(gè)不同的統(tǒng)計(jì)計(jì)數(shù)器發(fā)生更新,但一臺(tái)網(wǎng)絡(luò)設(shè)備中的統(tǒng)計(jì)計(jì)數(shù)器的數(shù)量及其更新速度常常受到存儲(chǔ)技術(shù)的限制。

管理統(tǒng)計(jì)計(jì)數(shù)器需要高性能的存儲(chǔ)器才能滿足多重的讀—修改—寫操作。本文將描述一種使用IP方法的獨(dú)特統(tǒng)計(jì)計(jì)數(shù)器,這種計(jì)數(shù)器的一端可以連接網(wǎng)絡(luò)處理器(NPU),另一端可以連接Xilinx公司的QDR-IV存儲(chǔ)控制器。QDR-IV統(tǒng)計(jì)計(jì)數(shù)器IP是一種帶有QDR-IV SRAM、為網(wǎng)絡(luò)交流管理和其他計(jì)數(shù)器應(yīng)用提供高效統(tǒng)計(jì)計(jì)數(shù)器的軟IP。

QDR-IV SRAM概述

QDR-IV SRAM配備兩個(gè)雙向數(shù)據(jù)端口A和B,可以在一個(gè)時(shí)鐘周期內(nèi)完成兩次數(shù)據(jù)寫入或兩次數(shù)據(jù)讀取操作,或一次讀寫結(jié)合的操作。因此,這一特點(diǎn)帶來了額外的靈活性,架構(gòu)師可將之用于讀/寫并不一定平衡的應(yīng)用中。每個(gè)端口在兩個(gè)時(shí)鐘沿均可進(jìn)行數(shù)據(jù)傳輸(DDR(雙倍數(shù)據(jù)速率)操作),工作模式為突發(fā)式,每個(gè)時(shí)鐘周期的突發(fā)長度為兩個(gè)字(每個(gè)字為X18或X36)。地址總線為通用型,其上升沿和下降沿能分別為端口A和端口B提供地址。部分制造商的QDR-IV SRAM還可支持嵌入式ECC(錯(cuò)誤檢查和糾正),可從根本上消除軟錯(cuò)誤,提高存儲(chǔ)器陳列的可靠性。

QDR-IV SRAM分為兩種:高性能 (HP) QDR-IV和超高性能 (XP) QDR-IV。HP設(shè)備的最大運(yùn)行頻率為667 MHz,而XP設(shè)備的最大運(yùn)行頻率為1066 MHz。QDR-IV XP能夠通過將存儲(chǔ)空間分成分成8個(gè)內(nèi)存條來增加性能,用地址的3個(gè)最低有效位(LSB)表示。要求的存儲(chǔ)方案是在同一周期內(nèi)存取不同的內(nèi)存條。從一個(gè)周期到另一周期,所有的內(nèi)存條均可存取,系統(tǒng)設(shè)計(jì)師可通過規(guī)劃系統(tǒng)架構(gòu)來相應(yīng)地分配記憶庫地址,以充分發(fā)揮極速存儲(chǔ)器的RTR性能。這樣,開發(fā)人員可以在降低總系統(tǒng)成本的同時(shí)大幅提高性能。

統(tǒng)計(jì)計(jì)數(shù)器IP

QDR IV統(tǒng)計(jì)計(jì)數(shù)器是一種帶有QDR-IV SRAM,并且為網(wǎng)絡(luò)交流管理和其他計(jì)數(shù)器應(yīng)用提供統(tǒng)計(jì)計(jì)數(shù)器的軟IP。該IP采用支持系統(tǒng)管理存取端口的讀—修改—寫邏輯。該IP的一端可以連接網(wǎng)絡(luò)處理單元(NPU),另一端可以連接 QDR-IV存儲(chǔ)控制器。由于該統(tǒng)計(jì)計(jì)數(shù)器支持400Gbps及更快速率的線卡,因此性能僅受限于所使用的FPGA和QDR-IV設(shè)備。

統(tǒng)計(jì)計(jì)數(shù)器IP的運(yùn)行

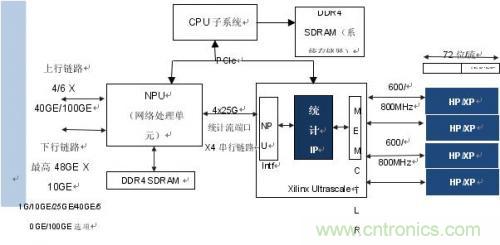

圖1是使用QDR-IV和統(tǒng)計(jì)計(jì)數(shù)器IP的用例。典型的網(wǎng)絡(luò)處理單元(NPU)以800M的每秒配對(duì)物更新速率發(fā)送統(tǒng)計(jì)(STATS)更新請(qǐng)求。每一項(xiàng)STATS請(qǐng)求包含在一個(gè)72位字中帶有兩個(gè)計(jì)數(shù)器(數(shù)據(jù)包和字節(jié)計(jì)數(shù))的入口/出口包命令令牌。整個(gè)計(jì)數(shù)器緩存數(shù)據(jù)以1秒為間隔,更新到系統(tǒng)存儲(chǔ)器中的終身計(jì)數(shù)器(通常為DRAM)。這一來自NPU的回讀被稱為處理器(PROCS)更新請(qǐng)求。PCIe接口用于傳輸計(jì)數(shù)器緩存數(shù)據(jù)以更新終身計(jì)數(shù)器。下圖顯示了STATS IP的設(shè)置和與Xilinx存儲(chǔ)控制器、PCIe總線和NPU連接的QDR-IV存儲(chǔ)器。

圖1:帶統(tǒng)計(jì)IP、NPU和存儲(chǔ)器的完整基礎(chǔ)架構(gòu)

統(tǒng)計(jì)IP適用于HP和XP QDR-IV存儲(chǔ)器。其運(yùn)行模式通過位于IP設(shè)計(jì)頂層接口的單一參數(shù)控制。兩個(gè)計(jì)數(shù)器(數(shù)據(jù)包和字節(jié))的每個(gè)流地址為單72位字。一個(gè)144Mb QDR-IV SRAM支持四百萬計(jì)數(shù)器。該設(shè)計(jì)所要求的IP接口數(shù)量與所使用的QDR-IV SRAM的數(shù)量相當(dāng)。

正如模塊圖所示,NPU通過4x25Gbps鏈路將統(tǒng)計(jì)和處理請(qǐng)求推送到IP中。IP的運(yùn)行頻率為存儲(chǔ)器存取頻率的四分之一,并且使用四條被稱為“通道”的平行數(shù)據(jù)路徑以匹配存儲(chǔ)器帶寬。在存儲(chǔ)接口HP和XP運(yùn)行模式中,端口A作為讀取端口,端口B作為寫入端口。每項(xiàng)統(tǒng)計(jì)請(qǐng)求對(duì)保存在與該請(qǐng)求相關(guān)的獨(dú)特存儲(chǔ)位置中的計(jì)數(shù)器數(shù)據(jù)進(jìn)行讀—修改—寫操作。

讀寫請(qǐng)求通過分階段來延遲與QDR-IV存儲(chǔ)器讀取延遲以及存儲(chǔ)控制器延遲的匹配。分階段設(shè)計(jì)也作為本地緩存累積延遲過程中的服務(wù)更新請(qǐng)求。在HP模式中,沒有統(tǒng)計(jì)/處理器更新地址限制通過四根通道中的任何一根。地址的發(fā)生可能是隨機(jī)的,并且無需給每根通道分配特定類型的地址。但由于在XP模式中存儲(chǔ)器的區(qū)塊結(jié)構(gòu)和限制與其相關(guān),因此通道0和1被分配到保存入口流數(shù)據(jù)的奇數(shù)地址位置,通道2和3被分配到保存出口流數(shù)據(jù)的偶數(shù)地址位置。這一獨(dú)特的安排可以預(yù)防可能在XP模式中發(fā)生的分塊限制位置。

處理器發(fā)出的一秒鐘回讀請(qǐng)求常見于這兩種運(yùn)行模式。整個(gè)存儲(chǔ)位置需要以一秒鐘間隔回讀,因此處理器不發(fā)出連續(xù)請(qǐng)求,并且以一秒鐘間隔時(shí)間分布。該活動(dòng)在每次通過處理器請(qǐng)求讀取后復(fù)位存儲(chǔ)器位置。

統(tǒng)計(jì)IP架構(gòu)

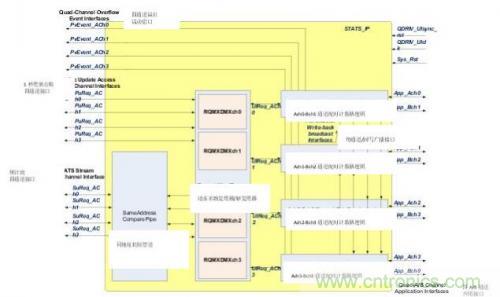

圖2中的STATS_IP架構(gòu)模塊圖標(biāo)出了三個(gè)子部件:每條通道的同地址比較管道(SACOMP)區(qū)塊、請(qǐng)求-復(fù)用-解復(fù)用(REQ_MXDMX_CHn)區(qū)塊以及每條QDR IV應(yīng)用通道1個(gè)的4個(gè)A-B通道配對(duì)計(jì)數(shù)器邏輯(ABCH_CTRL_CHn)區(qū)塊實(shí)例。

圖2:統(tǒng)計(jì)IP架構(gòu)

SACOMP模塊圖包含兩個(gè)管道階段,其中一個(gè)用于通過比較將同一時(shí)鐘周期上的所有四條通道進(jìn)行壓縮(SACOMP_ChN-to-All),另一個(gè)用于對(duì)單一通道上的同一地址進(jìn)行雙向(突發(fā)2)比較(SACOMP_B2BChN)。當(dāng)兩條或更多條通道在指定的時(shí)間實(shí)例中為同一地址時(shí),優(yōu)先性最高的通道積累地址相同的通道上出現(xiàn)的數(shù)據(jù),而所有其他優(yōu)先性較低、地址相同的通道都將失效。這確保了單一統(tǒng)計(jì)請(qǐng)求覆蓋所有地址相同的通道,從而預(yù)防出現(xiàn)任何數(shù)據(jù)一致性問題。比較和積累算法對(duì)所有可能的情況進(jìn)行快速評(píng)估。此外,在單根通道上,如果有同一存儲(chǔ)位置的雙向統(tǒng)計(jì)更新請(qǐng)求,則最新請(qǐng)求失效,其數(shù)據(jù)通過之前發(fā)生的請(qǐng)求積累。這樣能夠確保任何同一地址位置的雙向存取不會(huì)在QDR-IV存儲(chǔ)設(shè)備定義的讀取延遲中發(fā)生。

圖2所示的請(qǐng)求-復(fù)用– 解復(fù)用(RQMXDMXChn)區(qū)塊接收對(duì)應(yīng)通道數(shù)的處理器更新請(qǐng)求和統(tǒng)計(jì)更新請(qǐng)求。由于處理器更新請(qǐng)求的間隔時(shí)間固定,因此RQMXDMXchN選擇對(duì)應(yīng)下一個(gè)時(shí)鐘服務(wù)的處理器請(qǐng)求,并且通過“請(qǐng)求就緒”回壓信號(hào)停止統(tǒng)計(jì)請(qǐng)求。在開始處理每個(gè)一秒更新請(qǐng)求后,RQMXDMXchN停止配置時(shí)鐘數(shù)(默認(rèn)為10)的處理器請(qǐng)求通道以確保不會(huì)提供連續(xù)的一秒更新請(qǐng)求服務(wù)。停止信號(hào)發(fā)送至NPU,確保在回壓信號(hào)失效前不會(huì)產(chǎn)生新的請(qǐng)求。該機(jī)制能夠在不堵塞這一設(shè)計(jì)的情況下處理統(tǒng)計(jì)和處理器請(qǐng)求。

在最終階段,A-B通道配對(duì)計(jì)數(shù)器邏輯(ABCH_CTRLn)對(duì)每項(xiàng)統(tǒng)計(jì)請(qǐng)求實(shí)施實(shí)際的讀—修改—寫機(jī)制,同時(shí)確保對(duì)每一項(xiàng)處理器請(qǐng)求進(jìn)行最新讀取。該階段包含讀取-延時(shí)管道邏輯、控制復(fù)用、讀寫管道和QDR-IV控制器接口邏輯。讀寫延時(shí)管道考慮了內(nèi)存和控制器延遲。來自鄰近通道和同一通道控制復(fù)用的反饋機(jī)制杜絕所有數(shù)據(jù)一致性問題發(fā)生的可能性。管道中的請(qǐng)求流發(fā)起統(tǒng)計(jì)和處理器更新??刂茝?fù)用(CTRL_MUX)區(qū)塊區(qū)分處理器和統(tǒng)計(jì)請(qǐng)求,從而使當(dāng)前數(shù)據(jù)能夠作為處理器讀取數(shù)據(jù)轉(zhuǎn)發(fā)或者推送到控制器接口區(qū)塊以便進(jìn)行進(jìn)一步處理??刂破鹘涌趨^(qū)塊將實(shí)際的讀寫請(qǐng)求轉(zhuǎn)換為端口A和端口B上的控制器特定命令。

QDR-IV接口運(yùn)行和應(yīng)用通道映射

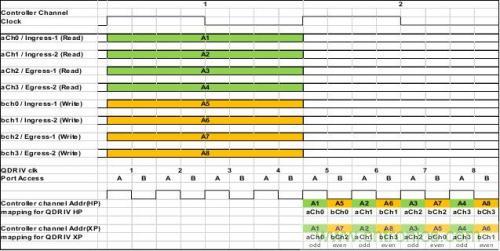

統(tǒng)計(jì)流四通道和一秒(處理器)更新四通道接口作為應(yīng)用通道。QDR IV控制器采用帶有為QDR IV端口A和端口B定義的專用四通道端口界面的4:1/1:4通道復(fù)用/解復(fù)用功能。QDR-IV控制器以固定順序?qū)νǖ肋M(jìn)行復(fù)用和解復(fù)用,應(yīng)用端和以4X時(shí)鐘頻率運(yùn)行的QDR IV設(shè)備端之間的順序?yàn)閏h0、ch1、ch2和ch3。圖3為所假設(shè)的QDR-IV控制器順序和建議的QDR IV HP統(tǒng)計(jì)計(jì)數(shù)器解決方案和QDR IV XP統(tǒng)計(jì)計(jì)數(shù)器解決方案應(yīng)用通道映射。

圖3 QDR-IV接口4:1/1:4 復(fù)用/解復(fù)用和應(yīng)用通道映射

在QDR-IV HP統(tǒng)計(jì)計(jì)數(shù)器中,端口A和端口B 的請(qǐng)求獨(dú)立于地址并按照Ch0-Ch1-Ch2-Ch3順序的排列。這是因?yàn)镠P模式無區(qū)塊要求,并且端口A和端口B上的請(qǐng)求可能包含同一位置的地址。但在QDR-IV XP統(tǒng)計(jì)計(jì)數(shù)器中,端口A和端口B的請(qǐng)求是以奇數(shù)-偶數(shù)-奇數(shù)-偶數(shù)為順序的排列的,這樣端口A和端口B在同一時(shí)鐘周期中就不會(huì)出現(xiàn)兩個(gè)屬于同一區(qū)塊的地址。

基于 QDR-IV SRAM的QDR IV 統(tǒng)計(jì)計(jì)數(shù)器IP為網(wǎng)絡(luò)流量管理和其他計(jì)數(shù)器的應(yīng)用提供了高效的統(tǒng)計(jì)計(jì)數(shù)方案。