【導(dǎo)讀】今天,我們來談?wù)勊须娮酉到y(tǒng)都存在的一種常見問題——電磁干擾也即 EMI,并側(cè)重討論時鐘的影響。從廣義來講,EMI 是中斷、阻礙或者降低電子器件有效性能的所有電磁干擾。其產(chǎn)生的方式有兩種:1)通過存在于信號之間的寄生電感/電容,或者通過電源或接地連接的無用耦合,從而產(chǎn)生 EMI;或者2)直接通過電子/磁輻射,即輻射性 EMI。

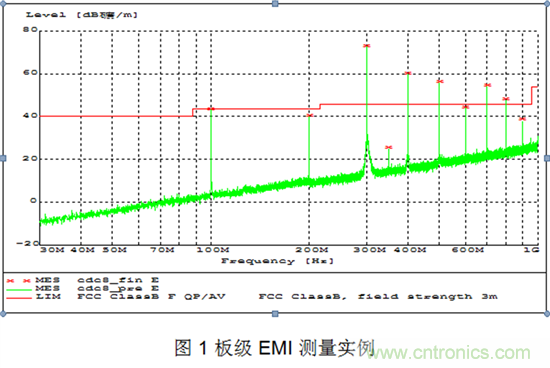

由于兩個原因,時鐘信號常歸咎于 EMI。即使時鐘低頻率運行,較好的時鐘上升/下降沿也包含大量的奇次諧波,其在更高頻率時會引起 EMI。另外,時鐘通常會在板上傳播一段較長的距離,從而更可能給其他組件帶來干擾。通常,EMI 可通過頻譜分析儀測量,如圖 1 所示。圖中,綠色信號存在一些超出紅色 FCC 屏蔽的頻率分量(300MHz、400MHz 和 500MHz 等)。

控制時鐘引起 EMI 的一些方法都基于上述兩種方式:屏蔽、去耦、精心布局,以及改變時鐘源特性。

屏蔽方法使用導(dǎo)體將 EMI 徹底包起來接地。利用這種方法,電磁能量被控制在系統(tǒng)內(nèi)部。另外,它還使外部信號更難以將 EMI 帶入系統(tǒng)。這種方法對傳導(dǎo)性 EMI 和輻射性 EMI 都有效。一般而言,這種方法在保護系統(tǒng)的敏感部件時成本較高,并且占用空間。高頻時效果較好。在 100MHz 以下時鐘頻率或邊緣速率情況下,EMI 自屏蔽層以上時鐘信號耦合,而屏蔽層本身也產(chǎn)生輻射。這種情況下,屏蔽的效果極其有限。一種解決方法是使用 RF 線圈。

大多數(shù)情況下,較好的去耦和精心的布局比屏蔽方法更能減少傳導(dǎo)性 EMI。

在每個有源器件(盡可能靠近器件連接電源或接地)上安裝旁路或者“去耦”電容有助于引導(dǎo)時鐘或任何其他高頻信號組件直接接地,而非干擾其他信號。至少用兩個數(shù)量級,交替這些旁路電容器的值。如果可能,選擇表面貼裝類型。在板上給去耦組件一個占位器 (position holder) 一直都是一個不錯的辦法。

就您的布局而言,基本原則是讓接地返回路徑短一些,并最小化信號環(huán)路。使用較短的過孔組件線。盡可能地靠近 PCB 貼裝組件,并將與時鐘線跡相關(guān)的所有組件都靠近放置在一起。如果可以的話,請使用差分信號。實事證明,使用一個專用接地層和多層布局較為高效。但是,這會增加電路板成本。對于一些如便攜式系統(tǒng)等成本敏感型設(shè)計而言,這樣做并不可取。這些情況下,改變時鐘信號本身可有效地減少 EMI 源,同時更便宜,也更靈活。

一種方法是減少信號擺動來降低峰值能量。增加串聯(lián)電阻減慢時鐘上升/下降沿,從而減少諧波。另一種普遍使用的方法是使用擴頻時鐘 (SSC),有意將時鐘能量傳播至更寬的頻帶,這樣便使峰值能量降低。這種 SSC 功能被集成到大多數(shù)我們的時鐘器件中。下次,我們將對其做更詳細的討論。

降低擺動或使用邊緣控制的缺點是使時鐘的抗噪性變差。使用 SSC 增加了時鐘的抖動。就消費類電子產(chǎn)品而言,通常較少關(guān)注這些。但是,對于一些高精度應(yīng)用而言,這些方法通常不是首選的方法。

結(jié)論

總之,降低 EMI 方法的選擇涉及您的應(yīng)用、時鐘頻率和成本/性能考慮等諸多方面。一般而言,它是所有上述方法的綜合。

參考文獻

● 《防止時鐘分布電路中 EMI 的應(yīng)用手冊》TI,網(wǎng)址: http://focus.ti.com/general/docs/techdocsabstract.tsp?abstractName=scaa031

● 如欲了解 CDCS502 的詳情并獲取 SSC 器件的樣片,您可以登錄 http://focus.ti.com/docs/prod/folders/print/cdcs502.html 下載產(chǎn)品說明時和其他技術(shù)文檔;請登錄 http://focus.ti.com/docs/prod/folders/print/cdce949.html 了解 CDCE949 詳情。

作者簡介

Lin Wu 現(xiàn)任 TI 接口和時鐘產(chǎn)品部產(chǎn)品營銷經(jīng)理。 Lin 女士畢業(yè)于愛荷華州立大學(xué)(Iowa State University),獲電子工程博士學(xué)位,現(xiàn)在擁有 3 項美國專利。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進行處理。

推薦閱讀: