【導(dǎo)讀】本電路筆記聚焦于該解決方案的振動(dòng)應(yīng)用,尤其是狀態(tài)監(jiān)控領(lǐng)域,但儀器儀表和工業(yè)自動(dòng)化領(lǐng)域也有大量應(yīng)用以類似方式使用IEPE傳感器,并且由類似的信號(hào)鏈提供服務(wù)。

電路功能與優(yōu)勢

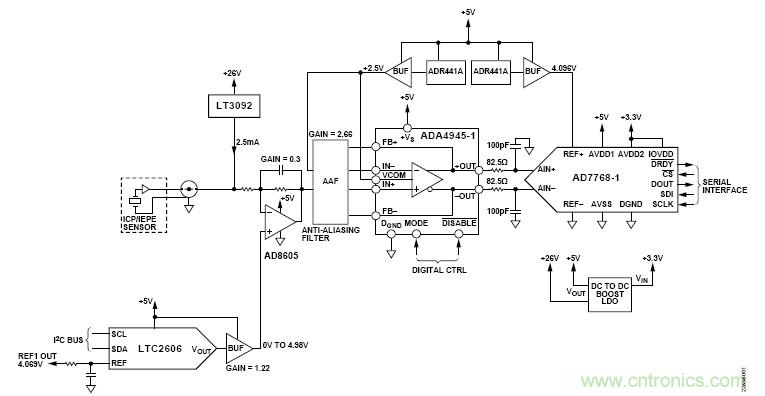

圖1所示的參考設(shè)計(jì)是一款高分辨率、寬帶寬、高動(dòng)態(tài)范圍的、IEPE (Integrated Electronics Piezoelectric)兼容接口數(shù)據(jù)采集(DAQ)系統(tǒng),其與ICP® (IC Piezoelectric)/IEPE傳感器接口。IEPE傳感器最常用于振動(dòng)測量應(yīng)用,但也有很多IEPE傳感器用于測量溫度、應(yīng)變、沖擊和位移等參數(shù)。

本電路筆記聚焦于該解決方案的振動(dòng)應(yīng)用,尤其是狀態(tài)監(jiān)控領(lǐng)域,但儀器儀表和工業(yè)自動(dòng)化領(lǐng)域也有大量應(yīng)用以類似方式使用IEPE傳感器,并且由類似的信號(hào)鏈提供服務(wù)。

具體而言,狀態(tài)監(jiān)控使用傳感器信息來幫助預(yù)測機(jī)器狀態(tài)的變化。跟蹤機(jī)器狀態(tài)的方法有很多,但振動(dòng)分析是最常用的方法。通過跟蹤振動(dòng)隨時(shí)間的分析數(shù)據(jù),可以預(yù)測故障或失效以及故障源。

工業(yè)環(huán)境需要穩(wěn)健可靠的檢測方法,這給振動(dòng)檢測增加了難度。了解機(jī)器的狀況有助于提高效率和生產(chǎn)率,并使工作環(huán)境更安全。

市場上大多數(shù)與壓電傳感器接口的解決方案都是交流耦合式,缺乏直流和亞赫茲測量能力。 CN-0540參考設(shè)計(jì)是一種直流耦合解決方案,可實(shí)現(xiàn)直流和亞赫茲精度。

通過查看IEPE振動(dòng)傳感器在頻域(直流至50 kHz)中的完整數(shù)據(jù)集,并使用快速傅立葉變換(FFT)頻譜中發(fā)現(xiàn)的諧波的位置、幅度和數(shù)量,可以更好地預(yù)測機(jī)器故障的類型和來源。

數(shù)據(jù)采集板為Arduino兼容外形尺寸,可以直接與大多數(shù)Arduino兼容開發(fā)板接口并由后者供電。

ADI公司的Circuits from the Lab®電路由ADI公司的工程師設(shè)計(jì)構(gòu)建。每個(gè)電路的設(shè)計(jì)和構(gòu)建都嚴(yán)格遵循標(biāo)準(zhǔn)工程規(guī)范,電路的功能和性能都在實(shí)驗(yàn)室環(huán)境中以室溫條件進(jìn)行了測試和檢驗(yàn)。然而,您需負(fù)責(zé)自行測試電路,并確定對(duì)您是否適用。因而,ADI公司將不對(duì)由任何原因、連接到任何所用參考電路上的任何物品所導(dǎo)致的直接、間接、特殊、偶然、必然或者懲罰性的損害負(fù)責(zé)。

圖1.IEPE壓電振動(dòng)傳感器的狀態(tài)監(jiān)控信號(hào)鏈

電路描述

圖1所示電路是IEPE傳感器的傳感器到比特(數(shù)據(jù)采集)信號(hào)鏈,包括電流源、帶數(shù)模轉(zhuǎn)換器(DAC)的電平轉(zhuǎn)換和衰減級(jí)、三階抗混疊濾波器、模數(shù)轉(zhuǎn)換器(ADC)驅(qū)動(dòng)器及全差分Σ-Δ型ADC。

可編程電流源以恒定電流驅(qū)動(dòng)壓電加速度計(jì)。輸出電流可通過外部電阻設(shè)置,根據(jù)傳感器和電纜的類型,通常設(shè)置在2 mA和20 mA之間。

DAC的緩沖和放大輸出以及電平轉(zhuǎn)換運(yùn)算放大器,將輸入信號(hào)偏移至接近2.5 V共模電壓(VCOM),以平衡抗混疊濾波器的輸入和全差分放大器(FDA)的輸入?;鶞?zhǔn)電壓源將FDA供電軌的第二個(gè)輸入設(shè)置為VCOM的2.5 V,確保滿足輸入裕量要求,并且輸出是為驅(qū)動(dòng)ADC而優(yōu)化的全差分電壓。

抗混疊濾波器將信號(hào)鏈的帶寬設(shè)置為54 kHz。壓電加速度計(jì)的帶寬高達(dá)20 kHz,但就相位延遲而言,選擇了更寬帶寬的信號(hào)鏈,從而在3軸測量中實(shí)現(xiàn)更好的相位匹配性能。(進(jìn)一步的帶寬限制發(fā)生在ADC的數(shù)字濾波器中,但相位延遲是已知且確定的。)

ICP/IEPE加速度計(jì)

任何IEPE振動(dòng)傳感器都可以與CN-0540參考設(shè)計(jì)接口,因?yàn)樗蠭EPE振動(dòng)傳感器都利用相同的原理工作,但具有不同的偏移電壓、噪聲電平、帶寬和靈敏度。IEPE輸出信號(hào)既攜帶交流電壓,也攜帶直流電壓,其中與振動(dòng)相關(guān)的交流電壓被直流轉(zhuǎn)換到介于7 V和13 V之間的某個(gè)電壓電平。此直流電平隨傳感器的不同而異,并且對(duì)于任何給定的傳感器,它都有相對(duì)于時(shí)間、溫度和勵(lì)磁電流的漂移分量。

IEPE傳感器必須由電壓范圍足夠高的電流源供電,以完全覆蓋傳感器的幅度。IEPE傳感器的典型激勵(lì)電壓為24V。

信號(hào)鏈的輸入可以接收高達(dá)10 V p-p的信號(hào)幅度,偏移電壓最高可達(dá)13 V。直流失調(diào)通過施加直流失調(diào)校正信號(hào)來消除,從而允許在任意低頻下工作。

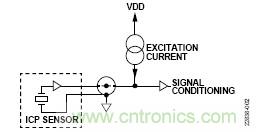

圖2.ICP加速度計(jì)模塊連接

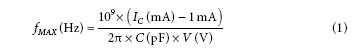

圖2顯示了一個(gè)傳感器的ICP加速度計(jì)框圖,其由恒流源供電并連接到直流耦合信號(hào)鏈。傳感器的最大帶寬與激勵(lì)電流成正比,與電纜電容成反比。選擇恒定電流電平時(shí),必須考慮傳感器的最大期望輸出電壓和電纜類型,可通過下式確定:

其中:

fMAX為傳感器的最大頻率,單位為Hz。

IC為恒定電流,單位為mA。

1 mA為傳感器的功耗要求。

C為電纜電容,單位為pF。

V為傳感器的最大峰值電壓輸出,單位為V。

注意在式1中,從提供給傳感器的總電流(IC)中減去了1 mA,該近似1 mA電流是用于為傳感器本身供電,而其余電流則用于驅(qū)動(dòng)電纜。此數(shù)字因傳感器而異。

例如,此參考設(shè)計(jì)使用PCB Piezotronics生產(chǎn)的333B52型ICP加速度計(jì)進(jìn)行了測試,最大峰值輸出為10 V,電纜長度為10英尺,電容為29 pF/英尺,激勵(lì)電流為2.5 mA。應(yīng)用式1,傳感器的最大理論帶寬為82.3 kHz。電纜和所選的電流水平均未限制傳感器的性能。

恒流源

設(shè)計(jì)恒流源(CCS)和考慮噪聲性能時(shí)應(yīng)多加注意。低電流噪聲至關(guān)重要,因?yàn)楫?dāng)驅(qū)動(dòng)信號(hào)鏈的輸入阻抗時(shí),電流噪聲會(huì)被轉(zhuǎn)換為電壓噪聲。

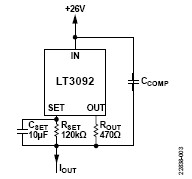

圖3.恒流源

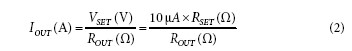

圖3顯示了一個(gè)2端子電流源,其電阻RSET和ROUT將輸出電流設(shè)置為2.5 mA,電容CSET限制電流噪聲的帶寬。LT3092的內(nèi)部10μA基準(zhǔn)電流源使RSET兩端保持穩(wěn)定的VSET。VSET鏡像到ROUT兩端,根據(jù)式2設(shè)置輸出電流。

請(qǐng)注意,由于內(nèi)部基準(zhǔn)電流從SET端子流出,因此實(shí)際的IOUT電流比式3給出的輸出電流要大10μA。

數(shù)據(jù)手冊(cè)建議RSET = 20kΩ,以將RSET兩端的壓降設(shè)置為200 mV,使失調(diào)電壓的影響最小。(在較小的VSET上,失調(diào)電壓更為明顯。)電阻產(chǎn)生的白電流噪聲由式3給出。

其中:

T為絕對(duì)溫度,單位為K。

k為玻耳茲曼常數(shù)(J/K)。

R為電阻。

電阻電流噪聲與電阻倒數(shù)的平方根成正比,因此將RSET的值從建議的20 kΩ增加到120 kΩ時(shí),ROUT也需要成比例地增加(而輸出電流保持在相同水平),導(dǎo)致整體噪聲電流下降。建議在RSET兩端接一個(gè)電容CSET,用以降低RSET和LT3092內(nèi)部電流基準(zhǔn)的電流噪聲。CSET電容旁路LT3092產(chǎn)生的電流噪聲。

如圖3所示,對(duì)恒流源進(jìn)行了LTspice仿真,以優(yōu)化元件值和布局依賴性。為了仿真Keysight E3631臺(tái)式電源(其兩路輸出串聯(lián)連接,總電壓設(shè)置為26V),我們建模了一個(gè)非理想電壓源,其在20 MHz帶寬內(nèi)具有0.7 mV rms的電壓噪聲和224 nA rms的電流噪聲。

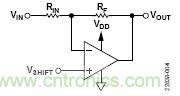

表1列出了不同元件值組合的均方根噪聲。均方根電流噪聲針對(duì)1 mHz至100 kHz的帶寬進(jìn)行了仿真。CCOMP的作用類似于高通濾波器,將噪聲從電壓源傳遞到輸出。進(jìn)一步增加RSET和ROUT有助于降低電流噪聲,但也會(huì)導(dǎo)致電阻上的壓降更高,從而降低容許的信號(hào)擺幅。

表1.降低LT3092電流噪聲

1 無需元件。

當(dāng)使用具有高電感的長電纜時(shí),穩(wěn)定性可能成為問題。有關(guān)補(bǔ)償感性負(fù)載的更多信息,請(qǐng)參閱LT3092數(shù)據(jù)手冊(cè)。

要計(jì)算電流源提供的可用傳感器激勵(lì)電壓,請(qǐng)使用下式:

其中:

VDD為恒流源的電源電壓。

LT3092DROP為IC本身的壓差(負(fù)載電流最高10 mA時(shí),其通常為1.2 V)。

RSET×10μA給出電阻上的壓差,其設(shè)置輸出電流電平,內(nèi)部10μA電流流過電阻。

在這種情況下,可用激勵(lì)電壓為23.6V。

電壓電平轉(zhuǎn)換器

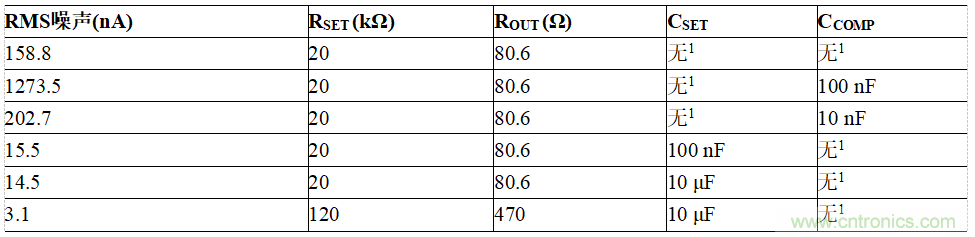

電壓電平轉(zhuǎn)換器可承受高達(dá)13 V的傳感器偏移電壓,信號(hào)擺幅最高可達(dá)10 V p-p,支持市場上的大多數(shù)壓電傳感器。選擇的是帶運(yùn)算放大器的反相電壓電平轉(zhuǎn)換器拓?fù)?,需要一個(gè)正轉(zhuǎn)換電壓來降低輸入電壓,以適應(yīng)FDA級(jí)的輸入要求。

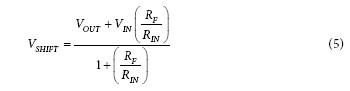

圖4.反相電壓電平轉(zhuǎn)換器

圖4顯示了一個(gè)帶運(yùn)算放大器的反相電壓電平轉(zhuǎn)換器拓?fù)?。轉(zhuǎn)換電壓通過下式計(jì)算:

電壓轉(zhuǎn)換器產(chǎn)生的VOUT電壓設(shè)置為盡可能接近VCOM (2.5 V),以平衡下一級(jí)中FDA的輸入。RF/RIN比值(運(yùn)算放大器的衰減)必須遵循以下約束:

•轉(zhuǎn)換運(yùn)算放大器的電源電壓:5 V

•轉(zhuǎn)換電壓范圍:0 V至5 V

•運(yùn)算放大器的穩(wěn)定性

•ADC的滿量程范圍:±4.096 V

•輸入信號(hào)幅度:10 V p-p

•輸入直流偏移電壓:最高13 V

0.3的衰減是合理的折衷方案,下一級(jí)中的較小增益可使ADC的輸入幅度最大化,并提高信噪比(SNR)。請(qǐng)注意,電平轉(zhuǎn)換器輸出端的信號(hào)和噪聲都會(huì)被放大,因此最大限度地降低電平轉(zhuǎn)換器的輸出噪聲至關(guān)重要。

在CN-0540中,輸入阻抗和輸入噪聲之間進(jìn)行了折衷,輸入噪聲電平足夠低,輸入電阻則足夠高,以防止引入測量誤差。壓電傳感器一般為低阻抗輸出(數(shù)百歐姆)傳感器,哪怕相對(duì)較低的信號(hào)鏈輸入阻抗(數(shù)十kΩ)也會(huì)引入不到1%的誤差。作為折衷方案,選擇的最終輸入阻抗RIN = 50kΩ。

使用下式計(jì)算輸入短路時(shí)電平轉(zhuǎn)換器模塊的電壓噪聲:

其中電阻的噪聲貢獻(xiàn)計(jì)算如下:

其中:

k為玻爾茲曼常數(shù)。

T為絕對(duì)溫度,單位為K。

R為電阻,單位為歐姆。

在平方之前,必須將除RIN以外的所有貢獻(xiàn)乘以噪聲增益。反相運(yùn)算放大器配置的噪聲增益與同相配置的噪聲增益相同。

使用下式計(jì)算反相輸入運(yùn)算放大器的噪聲貢獻(xiàn):

其中NG為電路的噪聲增益。

電壓電平轉(zhuǎn)換器模塊的單極點(diǎn)RC濾波器可限制噪聲。使用下式計(jì)算電壓電平轉(zhuǎn)換器產(chǎn)生的噪聲均方根值:

第一級(jí)的噪聲貢獻(xiàn)為20.8μVrms,其中最重要的噪聲貢獻(xiàn)者是RIN,這是將輸入阻抗設(shè)置得足夠高以使負(fù)載引起的誤差最小化的結(jié)果。

直流偏置補(bǔ)償技術(shù)

每個(gè)IEPE加速度計(jì)都有一定的直流偏置電壓,此電壓沒有攜帶任何有用的信息,因此必須將其消除。如果信號(hào)鏈中使用了直流耦合,便可讓輸入電壓直流轉(zhuǎn)換以抵消直流偏置電壓,使得ADC僅接收輸入電壓的交流部分,而沒有任何直流偏移。精確的直流轉(zhuǎn)換對(duì)于直流測量的精度和測量動(dòng)態(tài)范圍的最大化至關(guān)重要。

使用式5中的轉(zhuǎn)換電壓可以找到確切的轉(zhuǎn)換電壓。按照這種方法,必須分別為每個(gè)電路板和傳感器進(jìn)行不同溫度下的數(shù)次測量,從而確保測量的準(zhǔn)確性。

本電路使用了其他更精確、可靠且自動(dòng)化的技術(shù)。CN-0540中采用了定制的逐次逼近算法。標(biāo)準(zhǔn)逐次逼近模型使用DAC至ADC控制環(huán)路估算未知電壓電平的最終位置,而該定制逐次逼近算法試圖使用DAC至ADC環(huán)路將ADC輸入端的平均電壓設(shè)置為盡可能接近于0。換句話說,主要目標(biāo)是將FDA的兩個(gè)輸入設(shè)置為相同電壓電平,即VCOM = 2.5V。

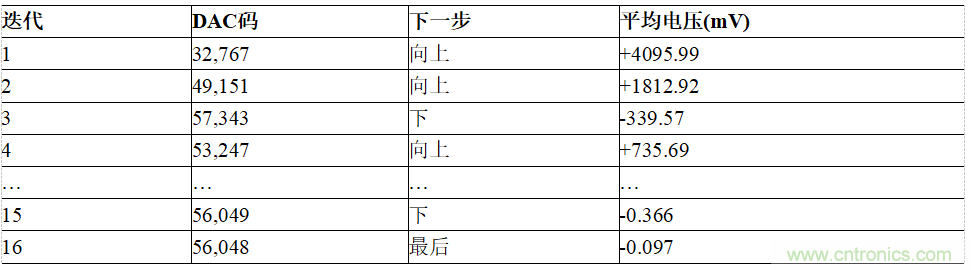

表2.輸入偏置電壓補(bǔ)償過程

表2顯示了使用逐次逼近算法補(bǔ)償輸入偏置電壓的過程。由于選擇了16位DAC,因此進(jìn)行了16次迭代。在此過程的最開始,DAC被設(shè)置為半量程輸出。每次將DAC設(shè)置為新值時(shí),均要測量平均電壓。如果平均電壓為正,則將1位權(quán)重加到當(dāng)前DAC輸出,否則就從當(dāng)前DAC輸出中減去1位權(quán)重。由于輸入運(yùn)算放大器使用反相配置,因此該過程是相反的。

第四個(gè)DAC輸出= (215 – 1) + 214 + 213 – 212 = 53,247 (11)

式11顯示了加上或減去的位權(quán)重。215 − 1為初始半量程值,然后是兩次向上和一次向下,意味著加上第14 位和第13 位,并減去第12 位。

由于傳感器的內(nèi)部結(jié)構(gòu),壓電傳感器本身會(huì)產(chǎn)生相當(dāng)顯著的電壓噪聲。傳感器通電后,傳感器始終會(huì)拾取環(huán)境噪聲,導(dǎo)致更多噪聲從機(jī)械環(huán)境事件轉(zhuǎn)換為電壓噪聲。為了僅提取壓電傳感器的直流偏置電壓,以及消除相當(dāng)顯著的噪聲(隨機(jī)噪聲或周期性噪聲),直流偏置補(bǔ)償過程中會(huì)進(jìn)行大量平均運(yùn)算。

電平轉(zhuǎn)換DAC

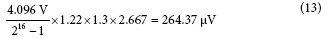

選擇具有27個(gè)可選I2C地址的16位電壓輸出DAC (LTC2606)進(jìn)行電平轉(zhuǎn)換。DAC與ADC共享4.096 V基準(zhǔn)電壓。為了實(shí)現(xiàn)轉(zhuǎn)換運(yùn)算放大器的同相輸入端預(yù)設(shè)的0 V至5 V完整轉(zhuǎn)換電壓范圍,并降低DAC輸出電壓噪聲,電路增加了一個(gè)外部緩沖器。該緩沖器具有Sallen-Key結(jié)構(gòu),截止頻率為100 Hz,增益為1.22。具有增益輸出的DAC的1 LSB為

從DAC到ADC輸入的路徑上還有其他增益。ADC輸入端觀測到的1 LSB變化放大4.23倍(所有增益的乘積),如下所示:

總LSBDAC =

其中,2.667是FDA的增益,1.3是轉(zhuǎn)換運(yùn)算放大器的增益;當(dāng)將變化的信號(hào)引入同相輸入端時(shí),轉(zhuǎn)換運(yùn)算放大器像同相運(yùn)算放大器一樣工作,實(shí)際增益為1 + (RF/RIN)。式13的計(jì)算得出將傳感器調(diào)整到正確電平所引起的最大理論直流誤差。

表2證明,ADC轉(zhuǎn)換的DAC 1 LSB約為264μV。檢查最后兩個(gè)ADC讀數(shù),差異僅為1 LSB,產(chǎn)生269μV。

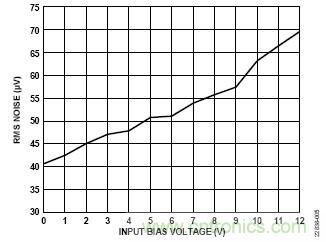

圖5.RMS噪聲與輸入偏置電壓的關(guān)系

圖5顯示了僅將輸入偏置電壓施加于信號(hào)鏈輸入端時(shí)均方根噪聲如何變化。每次改變輸入偏置時(shí),DAC都會(huì)將輸入調(diào)整至正確電平,確保失調(diào)誤差很低。信號(hào)鏈的均方根噪聲隨直流偏置的增加而增加,因?yàn)樘峁┲绷髌玫闹绷餍?zhǔn)器在較高電壓輸出電平下會(huì)產(chǎn)生更多噪聲。

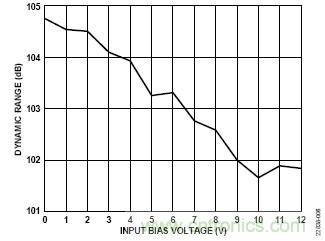

從圖5可知,動(dòng)態(tài)范圍響應(yīng)均方根噪聲的提高,導(dǎo)致輸入偏置電壓提高,如圖6所示。

圖6.動(dòng)態(tài)范圍與輸入偏置電壓的關(guān)系,1 kHz 1 V p-p輸入

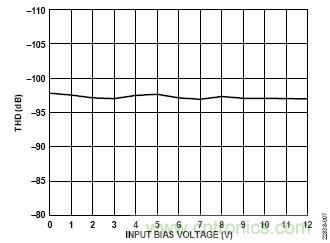

圖7顯示了系統(tǒng)線性度與輸入偏置電壓的關(guān)系,使用的輸入信號(hào)頻率為1 kHz,幅度為1 V p-p。圖7表明,輸入偏置電壓對(duì)線性度沒有明顯影響,總諧波失真(THD)保持穩(wěn)定。

圖7.線性度與輸入偏置電壓

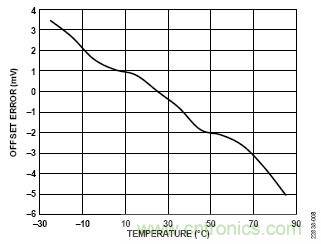

圖8顯示了整個(gè)溫度范圍內(nèi)ADC輸入端預(yù)設(shè)的失調(diào)電壓誤差。失調(diào)誤差是使用相同輸入電壓(10 V)在整個(gè)溫度范圍內(nèi)運(yùn)行輸入偏置電壓補(bǔ)償程序而確定的。25°C下的測量結(jié)果定位0 V失調(diào)誤差。

圖8.10 V輸入偏置電壓在整個(gè)溫度范圍內(nèi)的失調(diào)電壓誤差

如圖1所示,使用了基準(zhǔn)電壓為2.5 V的基準(zhǔn)電壓芯片(ADR441A),確保VCOM穩(wěn)定。此基準(zhǔn)電壓IC具有很高的溫度漂移特性,在-25°C至+ 85°C的溫度范圍內(nèi),電壓變化值為2.75 mV。此變化乘以2.667的FDA增益,導(dǎo)致ADC檢測到7.33 mV的總溫度漂移,該漂移隨后由DAC予以補(bǔ)償。

每次輸入電壓或VCOM發(fā)生變化時(shí)(VCOM僅因溫度漂移而變化),DAC都會(huì)反向補(bǔ)償該變化。在這種情況下,僅VCOM發(fā)生變化,輸入偏置則保持穩(wěn)定。ADR441A的電壓漂移占主導(dǎo)地位,這可以從圖8看出,其形狀與ADR441A的電壓漂移曲線相反。在指定溫度范圍內(nèi),數(shù)字碼的總變化為32 LSB。

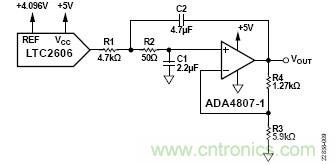

DAC緩沖器

DAC的內(nèi)部緩沖器會(huì)限制電壓噪聲,必須進(jìn)行濾波。由于DAC與ADC共享4.096 V基準(zhǔn)電壓,因此DAC輸出也必須放大以提供0 V至5V。

圖9.帶緩沖器的DAC

圖9顯示了采用低通Sallen-key濾波器結(jié)構(gòu)且具有增益輸出的電平轉(zhuǎn)換DAC。濾波器的截止頻率通過下式設(shè)置為大約100 Hz的較低值:

由于對(duì)Sallen-key濾波器拓?fù)鋺?yīng)用了一個(gè)增益,因此必須考慮濾波器的穩(wěn)定性。否則,緩沖器很可能會(huì)變成振蕩器。另一個(gè)與穩(wěn)定性相關(guān)的因素是濾波器質(zhì)量(Q),此模塊必須加以考慮。Q因子應(yīng)保持足夠低的值(小于0.707),以確保頻率響應(yīng)在截止頻率處沒有峰化,滾降具有較和緩的斜率,而且開始頻率顯著早于截止頻率。低Q因子適合于需要在整個(gè)頻率范圍內(nèi)具有高線性度的應(yīng)用。注意,只要Q因子變?yōu)樨?fù)值,結(jié)構(gòu)便變得不穩(wěn)定。使用下式確定Q因子:

其中k為Sallen-key拓?fù)涞脑鲆?,如下所示?/div>

對(duì)于圖9所示的值,截止頻率為102 Hz,k為1.215,Q為0.27,穩(wěn)定性和平滑滾降均有保證。

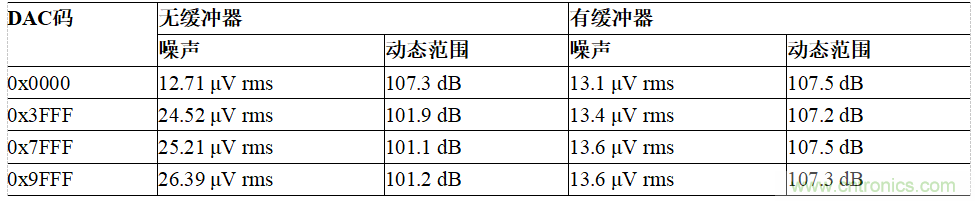

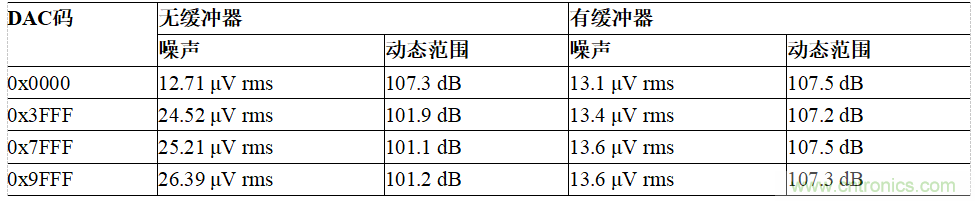

我們比較了有緩沖器和無緩沖器的DAC轉(zhuǎn)換模塊的噪聲性能。請(qǐng)注意,用于該測量的信號(hào)鏈在輸入短路時(shí)具有12.3μV rms的噪聲和108.2 dB的動(dòng)態(tài)范圍。該均方根噪聲是在64 kHz帶寬下測得的。

表3顯示了輸出電壓如何隨DAC碼變化。DAC輸出以漸進(jìn)方式設(shè)置:從零到四分之一量程、半量程,最終達(dá)到四分之三量程。在最壞情況下,DAC轉(zhuǎn)換模塊的噪聲貢獻(xiàn)僅為1.3μV rms。

表3.ADC測得的DAC輸出的噪聲比較

抗混疊濾波器和FDA

抗混疊濾波器和FDA使用差分多反饋低通結(jié)構(gòu),并將單端信號(hào)轉(zhuǎn)換為差分信號(hào)??够殳B濾波器的截止頻率設(shè)置為54 kHz,這比大多數(shù)壓電加速度計(jì)的帶寬要寬。該濾波器在2.3 MHz時(shí)提供−80 dB的阻帶抑制。

此級(jí)的增益設(shè)置為2.667,以便通過提升輸入幅度來更緊密地匹配ADC輸入的±VREF范圍,從而改善SNR。FDA也會(huì)放大寬帶噪聲,但由于抗混疊濾波器會(huì)限制寬帶噪聲,因此性能的降低小于信號(hào)增益帶來的改善。

模數(shù)轉(zhuǎn)換

AD7768-1是一款精密、單通道、24位Σ-Δ型ADC,選擇這款器件的原因是它具有出色的DC至204 kHz帶寬精度、低功耗、108.5 dB(典型值)動(dòng)態(tài)范圍和−120 dB THD。

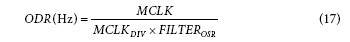

使用式17計(jì)算ADC的輸出數(shù)據(jù)速率:

其中:

MCLK為主時(shí)鐘。

MCLKDIV為主時(shí)鐘分頻器系數(shù)。

FILTEROSR為所選數(shù)字濾波器的過采樣率(OSR)。

時(shí)鐘分頻器和濾波器OSR是寄存器設(shè)置,可以通過SPI總線進(jìn)行更改。有限脈沖響應(yīng)(FIR)和SINC5濾波器的OSR是在AD7768-1的寄存器映射中嚴(yán)格設(shè)置。用戶可以使用下式將特定值寫入13位SINC3抽取率寄存器,從而將SINC3濾波器設(shè)置為自己偏好的OSR并更改輸出數(shù)據(jù)速率:

其中,ODR為所需的輸出數(shù)據(jù)速率,單位為Hz;213 為SINC3寄存器可接受的最大值。例如,對(duì)于4 Hz輸出數(shù)據(jù)速率、16.384 MHz MCLK及低功耗模式(MCLK/16),SINC3寄存器值為7999。

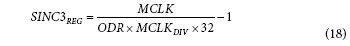

此參考設(shè)計(jì)的默認(rèn)設(shè)置針對(duì)32 kHz的ADC測量帶寬進(jìn)行了優(yōu)化,如下所示:

•功耗模式:低功耗模式

•MCLK分頻器:16

•濾波器類型:FIR

•濾波器抽取率:32

•輸入預(yù)充電緩沖器:使能

•基準(zhǔn)電壓緩沖器:使能預(yù)充電

•VCM引腳輸出:(AVDD1 − AVSS)/2

•轉(zhuǎn)換長度:24位

•轉(zhuǎn)換模式:連續(xù)

•校驗(yàn)和:無校驗(yàn)和

•數(shù)據(jù)讀取模式:連續(xù)

•狀態(tài)位:禁用

•DRDY信號(hào):使能

針對(duì)低功耗、高要求的應(yīng)用,兩個(gè)緩沖器均可關(guān)閉。但是,緩沖器保持開啟可改善整體THD和SNR。

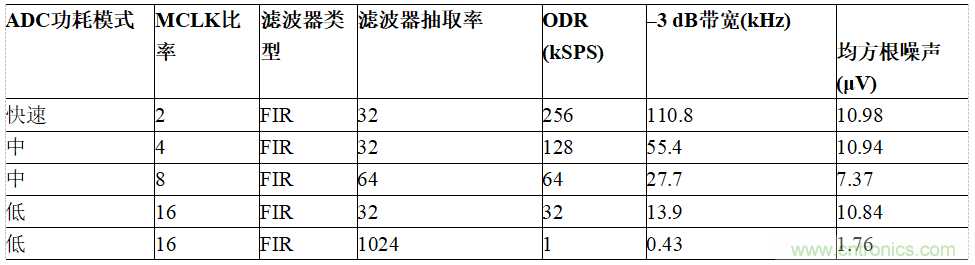

表4.針對(duì)不同帶寬的建議ADC設(shè)置

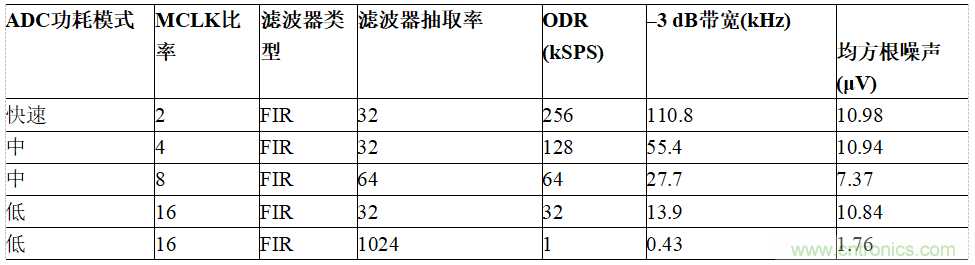

表5.信號(hào)鏈噪聲測量

1 低紋波FIR濾波器帶寬 = 0.433×ODR。

信號(hào)鏈的實(shí)測性能

該信號(hào)鏈設(shè)計(jì)針對(duì)的是中等到更寬帶寬的振動(dòng)檢測,較高的諧波和高于1 kHz的頻率成分很重要。設(shè)計(jì)必須權(quán)衡系統(tǒng)帶寬、線性度和可實(shí)現(xiàn)的噪聲性能。選擇較高的輸入阻抗以保持信號(hào)精度(線性度),在此設(shè)計(jì)中它決定了最大噪聲性能極限。信號(hào)帶寬也被設(shè)置得較寬,以保持系統(tǒng)在較高頻率下的響應(yīng)。使用帶寬較窄的設(shè)計(jì)可以實(shí)現(xiàn)更低噪聲解決方案,消除更多的寬帶噪聲。

CN-0540將模擬輸入帶寬設(shè)置為54 kHz,但實(shí)際信號(hào)帶寬由ADC配置決定。

噪聲

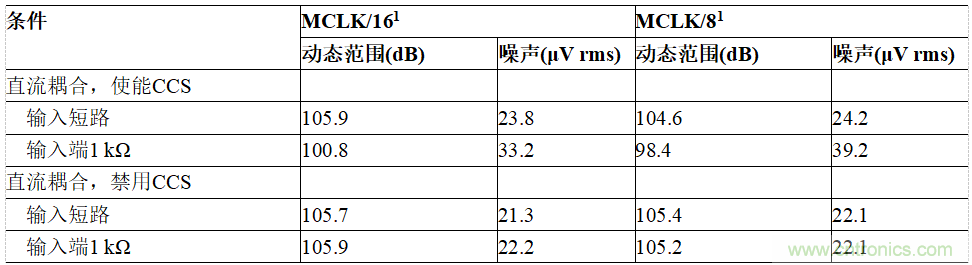

在幾種不同情況下對(duì)整個(gè)信號(hào)鏈的噪聲性能進(jìn)行了測量。

表5詳細(xì)列出了未連接任何傳感器時(shí)和添加1 kΩ負(fù)載電阻時(shí)信號(hào)鏈的典型噪聲性能。在信號(hào)鏈輸入端連接1 kΩ電阻的結(jié)果表明,恒定電流源會(huì)影響噪聲性能。電流噪聲轉(zhuǎn)換為電壓噪聲,乘以1 kΩ電阻,導(dǎo)致系統(tǒng)噪聲升高。

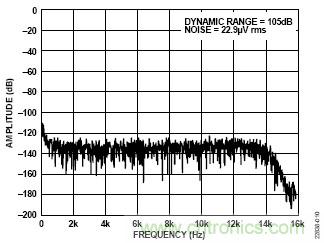

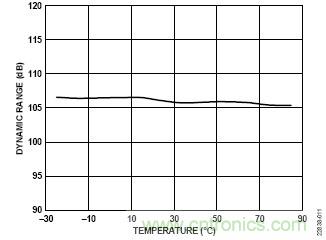

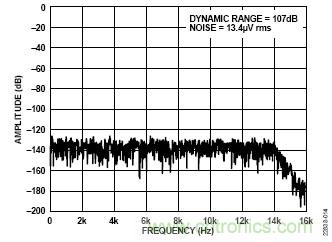

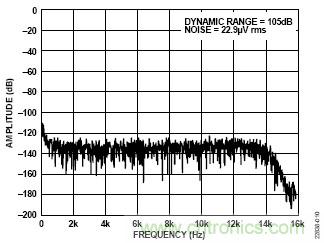

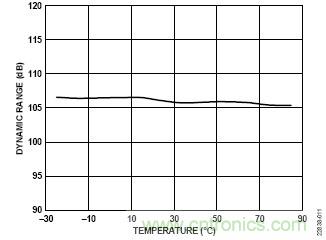

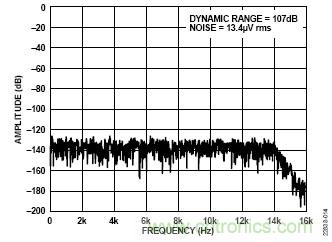

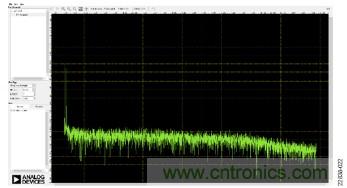

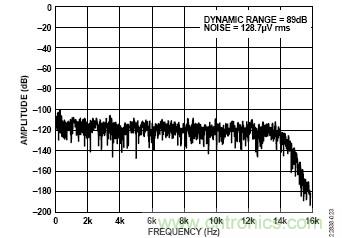

圖10顯示了輸入短路的系統(tǒng)的典型FFT圖。圖11顯示了輸入短路的直流耦合解決方案在整個(gè)溫度范圍內(nèi)的動(dòng)態(tài)范圍。

圖10.輸入短路的直流耦合解決方案的FFT,DAC輸出為半量程

圖11.輸入短路的直流耦合解決方案在整個(gè)溫度范圍內(nèi)的動(dòng)態(tài)范圍

傳感器噪聲貢獻(xiàn)

數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)人員的常見目的是盡可能準(zhǔn)確地捕獲傳感器輸出信號(hào)。這在實(shí)踐中意味著,系統(tǒng)性能應(yīng)該由傳感器特性設(shè)置。傳感器的噪聲性能常常是整體測量系統(tǒng)的關(guān)鍵限制因素之一,了解這一點(diǎn)有助于確定設(shè)計(jì)的性能要求。

此設(shè)計(jì)的目標(biāo)是支持傳感器以在大于1 kHz的帶寬提供振動(dòng)數(shù)據(jù),這些傳感器用于狀態(tài)監(jiān)控應(yīng)用的數(shù)據(jù)采集系統(tǒng),以對(duì)旋轉(zhuǎn)式或往復(fù)式工廠設(shè)備進(jìn)行預(yù)測性維護(hù)。

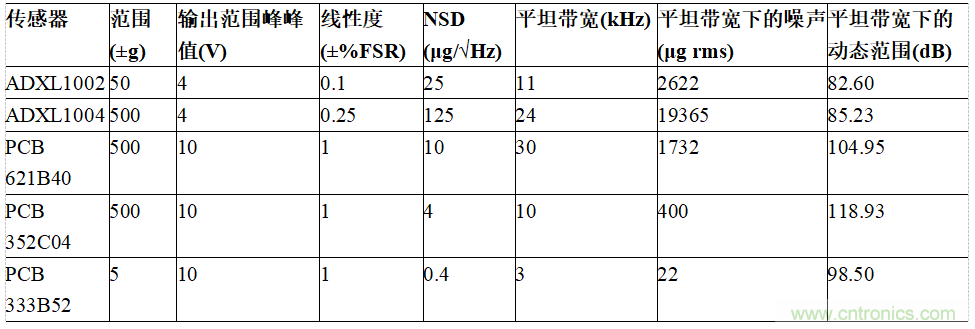

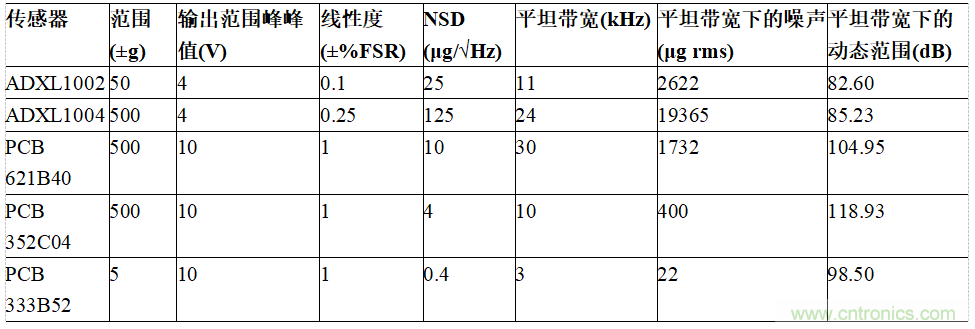

表6詳細(xì)列出了少量振動(dòng)傳感器的性能水平和帶寬。傳感器選擇的主要考慮因素通常是帶寬、范圍、噪聲頻譜密度(NSD)和功耗。

ADXL1002和ADXL1004傳感器是低功耗器件,適用于功耗和帶寬至關(guān)重要的各種振動(dòng)應(yīng)用。這些加速度計(jì)適合于連續(xù)監(jiān)控應(yīng)用,例如物聯(lián)網(wǎng)(IoT)機(jī)器監(jiān)控。

如需最高靈敏度和帶寬(較高頻率下的低噪聲和靈敏度至關(guān)重要),壓電傳感器仍然是最適合使用的傳感器。由于AD7768-1具有寬帶寬和低噪聲特性,因此該信號(hào)鏈可在超過10 kHz的較寬帶寬范圍內(nèi)匹配典型傳感器的性能水平。

對(duì)于CN-0540,系統(tǒng)帶寬設(shè)置為54 kHz,信號(hào)鏈噪聲性能針對(duì)的是可以在該帶寬上實(shí)現(xiàn)>100 dB動(dòng)態(tài)范圍的傳感器。例如,Piezotronics PCB 621B40型加速度計(jì)在30 kHz時(shí)可實(shí)現(xiàn)近105 dB的動(dòng)態(tài)范圍。

通過調(diào)整各級(jí)的電阻值和增益,并且利用AD7768-1的較高過采樣模式,該電路可適用于動(dòng)態(tài)范圍更高、帶寬更窄的傳感器。完整的分析超出了本文的范圍,但AD7768-1數(shù)據(jù)手冊(cè)中提供了有關(guān)使用過采樣時(shí)權(quán)衡動(dòng)態(tài)范圍和帶寬的更多信息。

表6.傳感器及相應(yīng)的噪聲密度測量結(jié)果

線性度

傳感器測量系統(tǒng)的線性度對(duì)于確保測量結(jié)果不會(huì)因傳感器輸出變化而變化至關(guān)重要。測量系統(tǒng)的精度不應(yīng)隨輸出偏置電壓或傳感器信號(hào)幅度變化而變化。理想情況下,當(dāng)測量系統(tǒng)的溫度發(fā)生變化時(shí),精度也應(yīng)保持不變。

CN-0540被設(shè)計(jì)為盡可能線性,并在整個(gè)溫度范圍內(nèi)保持該線性度,因此對(duì)測量信號(hào)鏈的校準(zhǔn)需求不多。系統(tǒng)對(duì)直流輸入電壓變化的非線性被報(bào)告為INL誤差。系統(tǒng)對(duì)正弦波輸入的非線性被報(bào)告為THD誤差。

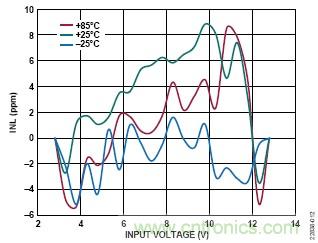

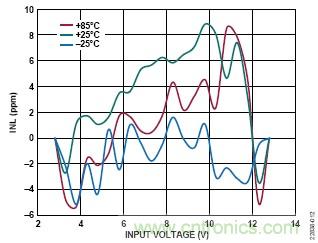

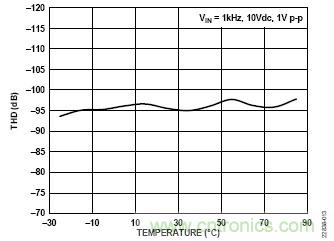

圖12和圖13中的數(shù)據(jù)表明:在寬輸入電壓范圍內(nèi),直流線性度(INL)在±10 ppm以內(nèi);在寬溫度范圍內(nèi),INL和THD均相對(duì)平坦。

圖12.不同溫度下INL與輸入電壓的關(guān)系

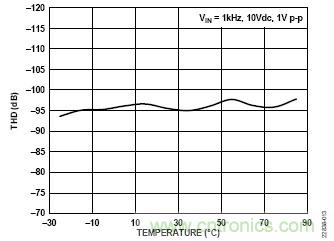

圖13.THD與溫度的關(guān)系

交流與直流耦合解決方案

CN-0540針對(duì)的是直流耦合應(yīng)用場景,其中必須保留信號(hào)的直流分量,或者必須將系統(tǒng)的響應(yīng)保持到低于1 Hz或更低的頻率。因此,該系統(tǒng)設(shè)計(jì)用于處理IEPE傳感器的大直流偏置。

但是,某些系統(tǒng)可能不需要低至DC的響應(yīng),在這些情況下,交流耦合輸入通道是可接受的。

兩種解決方案的主要區(qū)別在于信號(hào)鏈的復(fù)雜性以及直流和低頻時(shí)的精度。交流耦合解決方案的復(fù)雜度較低,但在低頻時(shí)精度不高。

用戶可以插入一個(gè)耦合電容與輸入電阻串聯(lián),使該設(shè)計(jì)適應(yīng)交流耦合設(shè)計(jì)。如需更多信息,請(qǐng)參閱設(shè)計(jì)支持包中的原理圖文件。

插入耦合電容的效果是將輸入響應(yīng)變?yōu)楦咄憫?yīng),在這種情況下,通常選擇遠(yuǎn)小于10 Hz的極點(diǎn)頻率。此濾波器不僅阻隔直流偏置電流,而且會(huì)消除一些1/f噪聲。交流耦合系統(tǒng)的動(dòng)態(tài)范圍似乎高于直流耦合版本,但這僅僅是由于消除了低頻噪聲。這樣做的代價(jià)是對(duì)低頻振動(dòng)測量數(shù)據(jù)的靈敏度降低。

由于DAC輸出以及信號(hào)鏈輸入端缺少高通濾波器,直流耦合解決方案的噪聲預(yù)期也會(huì)更高。圖14顯示了CN-0540交流耦合時(shí)的響應(yīng),其高通截止頻率為1 Hz。測量條件如下:信號(hào)鏈的輸入短路,使能恒流源,ADC處于低功耗模式,MCLK/16,F(xiàn)IR濾波器抽取率為32,直流耦合測量。

圖14.輸入短路的交流耦合解決方案的FFT

如果實(shí)施交流耦合解決方案,則必須選擇正確的電容類型以獲得最佳性能。一般而言,陶瓷電容會(huì)因?yàn)閴弘娦?yīng)而產(chǎn)生噪聲,因?yàn)殡妷合禂?shù)(相對(duì)介電常數(shù)隨施加的電壓而變化)和電介質(zhì)吸收而產(chǎn)生非線性。鉭電容可提供合理的性能,并且可制造出寬范圍的電容值,最高可達(dá)數(shù)百μF。在交流耦合情況下,鉭電容可以實(shí)現(xiàn)的THD性能水平與直流耦合系統(tǒng)相似,但頻率須高于10 Hz。為了準(zhǔn)確表示更低頻振動(dòng),最好選擇直流耦合版本。

系統(tǒng)電源

CN-0540帶有一個(gè)最優(yōu)電源解決方案,支持通過3.3 V單電源軌為整個(gè)信號(hào)鏈供電。

電源解決方案

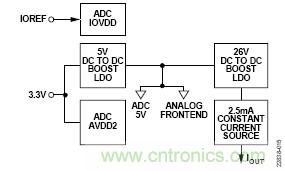

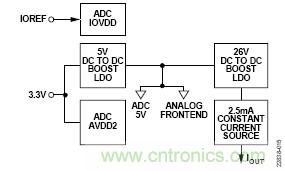

圖15顯示了CN-0540電源部分的簡化框圖。為了與具有Arduino樣式連接的微控制器和其他開發(fā)板兼容,該板的電源解決方案設(shè)計(jì)為采用3.3 V單電源(通常由Arduino兼容板提供)供電。

為了確保系統(tǒng)的穩(wěn)定性,微控制器板應(yīng)能通過3.3 V電源向振動(dòng)監(jiān)控板供應(yīng)至少250 mA的電流。這不算微控制器板本身從該電源獲取的電源電流。

雖然CN-0540評(píng)估板在穩(wěn)態(tài)工作時(shí)不需要250 mA電流,但在初始上電階段,可能有高達(dá)200 mA或更高的浪涌電流并持續(xù)最長30 ms。如果微控制器板無法承受此電流,可能導(dǎo)致微控制器板上發(fā)生復(fù)位。如果發(fā)生意外復(fù)位,請(qǐng)檢查微控制器板的電流輸出規(guī)格。

圖15.電源部分框圖

電源解決方案包括三個(gè)電壓域:3.3 V域、5 V域和26 V域。它還包括用于IEPE傳感器的2.5 mA電流源。

Arduino兼容板提供CN-0540直接使用的IOREF電源,因此不需要電源解決方案。IOREF為AD7768-1 (IOVDD)提供數(shù)字接口電源,并為16.384 MHz主時(shí)鐘源供電。

CN-0540與低至1.8 V的IOREF電壓兼容,因此CN-0540板可連接至邏輯電平較低的微控制器板。

所提供的電源解決方案電路的目的是讓CN-0540板可以從單個(gè)低壓電源(通常由微控制器板提供)供電,并從該電源生成其他所需的電壓軌。在CN-0540上,原始3.3 V輸入供電軌直接用于為AD7768-1提供數(shù)字接口邏輯電源(AVDD2電源),而且還為DC-DC級(jí)提供電源,從而將電壓提升至5 V和26 V。

第一個(gè)DC-DC級(jí)將3.3 V升壓至7 V,然后通過LTC3459和ADP7118器件組合調(diào)節(jié)至5 V,以提供AD7768-1、LTC2606和ADR4540基準(zhǔn)電壓源以及相關(guān)放大器級(jí)所需的干凈供電軌。

第二個(gè)DC-DC級(jí)將3.3 V升壓至28 V,然后通過LT3494和LT3008器件組合調(diào)節(jié)至26 V。這個(gè)干凈的26 V電源軌用于為LT3092電流源供電,從而為IEPE傳感器提供2.5 mA電流和高達(dá)26 V的電壓。

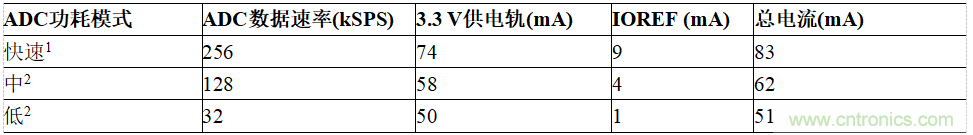

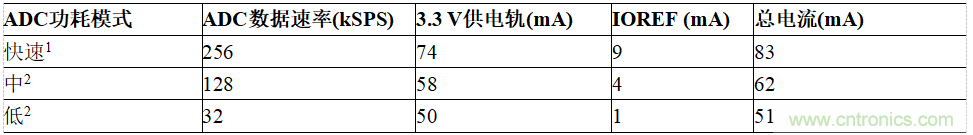

功耗測量

功耗測量直接從3.3 V和IOREF供電軌進(jìn)行。因此,功耗測量包括電源解決方案元件本身的貢獻(xiàn)。

由于恒流源,流向26 V供電軌的電流是恒定的,不會(huì)隨ADC設(shè)置而變化。

系統(tǒng)其余部分的功耗在ADC的不同工作模式下進(jìn)行了測量。信號(hào)鏈輸入端放置了一個(gè)1 kΩ負(fù)載電阻,以為恒流源流出的電流提供一條路徑,并在AD8605的輸入端保持直流偏置。

功耗

ADC上影響功耗的最重要寄存器設(shè)置為

•電源模式

•MCLK分頻器

•MCLK頻率

•濾波器類型

•濾波器抽取率

•VCM引腳輸出分壓器

•模擬輸入預(yù)充電緩沖器

•基準(zhǔn)電壓緩沖

•通用輸入/輸出(GPIO)

系統(tǒng)默認(rèn)配置

對(duì)于ADC設(shè)置,針對(duì)窄帶寬測量的系統(tǒng)默認(rèn)配置如下:

•MCLK分頻器:MCLK/16

•功耗模式:低功耗模式

•FIR濾波器,抽取率超過32

•VCM引腳輸出:(AVSS − AVDD)/2

•基準(zhǔn)電壓(REF)緩沖器:預(yù)充電開啟

•模擬輸入(AIN)緩沖器:預(yù)充電開啟

•MCLK頻率為16.384 MHz

•使能FDA,低功耗模式

•使能DAC緩沖器

•DAC輸出設(shè)置為半量程

該參考設(shè)計(jì)中包含的大多數(shù)測量均使用系統(tǒng)默認(rèn)配置。

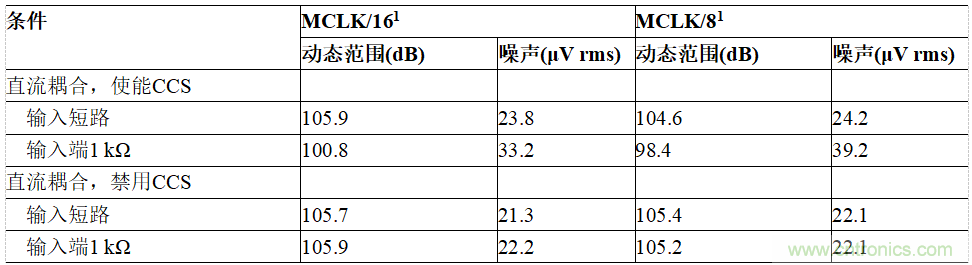

表7.各種數(shù)據(jù)速率下的功耗

1 FDA處于全功率模式。

2 FDA處于低功耗模式。

AD7768-1上的模擬輸入和基準(zhǔn)電壓輸入緩沖器設(shè)置為預(yù)充電模式。ADA4945-1 FDA設(shè)置為低功耗模式。在全功率模式下,F(xiàn)DA可以提供更寬的帶寬和更好的線性度性能。但是,由于此設(shè)計(jì)的目標(biāo)帶寬小于50 kHz,因此低功耗模式就夠了。通過使能AD7768-1內(nèi)部預(yù)充電緩沖器,可以實(shí)現(xiàn)更好的線性度和噪聲性能,而不會(huì)顯著增加系統(tǒng)功耗。有關(guān)匹配驅(qū)動(dòng)器放大器以及使用AD7768系列的輸入緩沖選項(xiàng)的更多信息,參見應(yīng)用筆記AN-1384。

常見變化

對(duì)于更高通道數(shù)的系統(tǒng),多通道AD7768和AD7768-4是AD7768-1的合適替代產(chǎn)品。ADC的噪聲和線性度與AD7768-1相似,但這些器件的優(yōu)勢是可在單個(gè)芯片中提供多達(dá)8個(gè)同步通道,從而簡化多通道IEPE DAQ設(shè)計(jì)的實(shí)現(xiàn)。

其他可以考慮用于振動(dòng)和狀態(tài)監(jiān)控信號(hào)鏈的ADC有AD4000、AD4002和AD7380。

ADA4610-1適用于第一級(jí)信號(hào)調(diào)理和電平轉(zhuǎn)換,但需要更高的電源電壓才能正常工作。ADA4807-1和ADA4940-1是ADC輸入抗混疊濾波器和驅(qū)動(dòng)器級(jí)的替代產(chǎn)品。

ADAQ7980/ADAQ7988是16位ADC μModule®數(shù)據(jù)采集系統(tǒng),ADC和ADC驅(qū)動(dòng)器級(jí)以及最關(guān)鍵的無源元件均被集成到系統(tǒng)級(jí)封裝(SiP)設(shè)計(jì)中。建議在尺寸或?qū)崿F(xiàn)的簡易性更為關(guān)鍵的場合使用這些器件。

這些方案允許根據(jù)性能(噪聲或線性度)、解決方案尺寸和成本來選擇信號(hào)鏈元件。

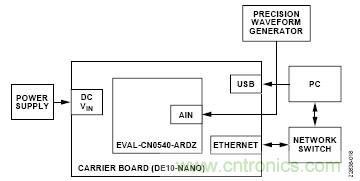

電路評(píng)估與測試

下面概述CN-0540電路設(shè)計(jì)的測試程序和結(jié)果的收集。有關(guān)硬件和軟件設(shè)置的完整詳細(xì)信息,參見CN-0540用戶指南。

設(shè)備要求

需要以下設(shè)備:

•EVAL-CN0540-ARDZ參考設(shè)計(jì)板

•Terasic DE10-Nano FPGA

•帶有CN-0540參考軟件的FPGA Linux鏡像

•帶有高清多媒體接口(HDMI®)端口的顯示器

•HDMI轉(zhuǎn)HDMI電纜

•帶有USB加密狗的無線鍵盤和鼠標(biāo)

•USB on-the-go (OTG)電纜(micro USB轉(zhuǎn)USB)

•精密交流電源(例如,Brüel&Kjær AP2700或類似精密正弦波發(fā)生器)

•帶BNC和SMA終端的同軸電纜

圖16.CN-0540參考設(shè)計(jì)板的3D渲染圖

開始使用

基本測試設(shè)置要求將EVAL-CN0540-ARDZ板插入支持的FGPA載板。載板需要為EVAL-CN0540-ARDZ板供電、運(yùn)行嵌入式Linux鏡像、捕獲數(shù)據(jù)并顯示數(shù)據(jù)。該軟件可從ADI公司網(wǎng)站獲得,其支持Terasic DE10-Nano和類似的Arduino兼容FPGA載板。

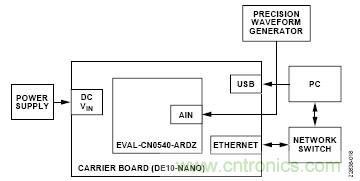

圖17.設(shè)置框圖

要測試該板的基本功能,請(qǐng)將精密高質(zhì)量正弦波或任意波形發(fā)生器連接到EVAL-CN0540-ARDZ板的模擬輸入連接器。

分步說明如下:

1. 插入Arduino接頭,將EVAL-CN0540-ARDZ評(píng)估板安裝到載板上(Terasic DE10-Nano),如圖18所示。

圖18.EVAL-CN0540-ARDZ安裝在Terasic DE10-Nano載板上

2. 將同軸電纜的BNC端連接到信號(hào)源單端或不平衡輸出,另一端連接到EVAL-CN0540-ARDZ模擬輸入SMA連接器(參見圖19)。

圖19.同軸電纜連接到CN-0540模擬輸入連接器的特寫照片

3. 將ADI FPGA Linux鏡像加載到micro SD卡上。

4. 配置micro SD卡以對(duì)CN-0540和載板使用正確的文件。

5. 將HDMI電纜從Terasic DE10-Nano連接到顯示器。

6. 將USB OTG電纜連接到Terasic DE10-Nano上的micro USB端口,然后插入無線鼠標(biāo)/鍵盤的USB加密狗。

7. 使用所提供的電源,將管式插孔連接到DE10-Nano,然后接通Terasic DE10-Nano電源開關(guān)。

8. 按照如下步驟開啟正弦或任意波形發(fā)生器的電源:

a. 將信號(hào)類型設(shè)置為正弦波。

b. 在1 kHz下將電平設(shè)置為1 V p-p。

c. 使能輸出。

9. 運(yùn)行該軟件并捕獲生成的ADC數(shù)據(jù)和FFT數(shù)據(jù)。

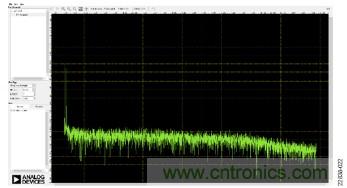

圖20和圖21中的兩幅圖顯示了按照步驟1至步驟9所述進(jìn)行配置時(shí)載卡的預(yù)期典型捕獲結(jié)果。圖20顯示了ADC捕獲數(shù)據(jù)的時(shí)域視圖,說明了多個(gè)樣本的預(yù)期幅度。

圖20.時(shí)域數(shù)據(jù)

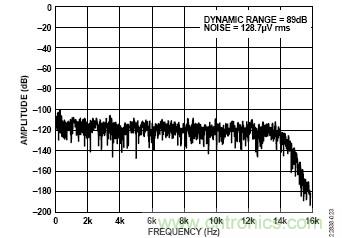

圖21顯示了經(jīng)過處理后顯示為頻域FFT圖的相同數(shù)據(jù)。

圖21.所捕獲數(shù)據(jù)的FFT

有關(guān)硬件和軟件設(shè)置的更多信息,請(qǐng)參閱CN-0540用戶指南以了解詳情。

壓電加速度計(jì)傳感器結(jié)果

為了實(shí)現(xiàn)合理的噪聲測量,必須讓壓電加速度計(jì)保持穩(wěn)定——要么使用主動(dòng)振動(dòng)臺(tái)來抵消環(huán)境振動(dòng),要么將其固定在大型物體上以減少從環(huán)境中拾取的振動(dòng)。在壓電加速度計(jì)直接連到信號(hào)鏈輸入端的場合,使用了固定到大型物體的方法。所用傳感器為Piezotronics PCB 333B52型3 kHz傳感器。

圖22顯示了連接傳感器時(shí)獲得的FFT的比較性能圖。系統(tǒng)的噪聲主要由傳感器信號(hào)決定。

圖22.連接有無源穩(wěn)定壓電傳感器的直流耦合解決方案的FFT

了解更多

CN0540設(shè)計(jì)支持包:https://www.analog.com/CN0540-DesignSupport

CN0540用戶指南

ADC驅(qū)動(dòng)器工具

MS-2066技術(shù)文章,傳感器電路的低噪聲信號(hào)調(diào)理

AN-1384:驅(qū)動(dòng)放大器與

AD7768/AD7768-4或AD7768-1配合使用

數(shù)據(jù)手冊(cè)和評(píng)估板

CN-0540電路評(píng)估板(EVAL-CN0540-ARDZ)

LT3092數(shù)據(jù)手冊(cè)

LT3092EDD演示板

AD8605數(shù)據(jù)手冊(cè)

ADA4945-1數(shù)據(jù)手冊(cè)

ADA4945-1評(píng)估板

AD7768-1數(shù)據(jù)手冊(cè)

AD7768-1評(píng)估板

LTC2606數(shù)據(jù)手冊(cè)

LTC2606 DAC演示板

ADA4807-1數(shù)據(jù)手冊(cè)

ADR4540 Data Sheet

ADR4540數(shù)據(jù)手冊(cè)

ADA4807-2數(shù)據(jù)手冊(cè)

LTC3459數(shù)據(jù)手冊(cè)

LT3494數(shù)據(jù)手冊(cè)

LT3008數(shù)據(jù)手冊(cè)

ADP7118數(shù)據(jù)手冊(cè)

ADP7118評(píng)估板

I2C指最初由Philips Semiconductors(現(xiàn)為NXP Semiconductors)開發(fā)的一種通信協(xié)議。

Circuits from the Lab電路僅供與ADI公司產(chǎn)品一起使用,并且其知識(shí)產(chǎn)權(quán)歸ADI公司或其授權(quán)方所有。雖然您可以在產(chǎn)品設(shè)計(jì)中使用參考電路,但是并未默認(rèn)授予其它許可,或是通過此參考電路的應(yīng)用及使用而獲得任何專利或其它知識(shí)產(chǎn)權(quán)。ADI公司確信其所提供的信息是準(zhǔn)確可靠的。不過,Circuits from the Lab電路是以“原樣”的方式提供的,并不具有任何性質(zhì)的承諾,包括但不限于:明示、暗示或者法定承諾,任何適銷性、非侵權(quán)或者某特定用途實(shí)用性的暗示承諾,ADI公司無需為參考電路的使用承擔(dān)任何責(zé)任,也不對(duì)那些可能由于其使用而造成任何專利或其它第三方權(quán)利的侵權(quán)負(fù)責(zé)。ADI公司有權(quán)隨時(shí)修改任何參考電路,恕不另行通知。

推薦閱讀: